Cortex-A510------内核及汇编

小狼@http://blog.csdn.net/xiaolangyangyang

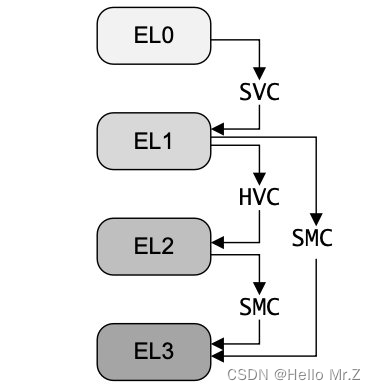

1、异常等级

2、异常等级切换

同步异常:

1、SVC/HVC/SMC;

2、MMU引发的异常(内核态EL1发生,发生后不会进行异常等级切换);

3、SP和PC对齐检查;

4、未分配或者没有权限的指令。

异步异常(ERET/ERETAA/ERETAB):

1、SError: 通常是由硬件导致的,没办法修复;

2、IRQ:如从EL0->EL1,如在EL1发生IRQ,不会切换异常等级;

3、FIQ:如从EL0->EL1,如在EL1发生FIQ,不会切换异常等级。

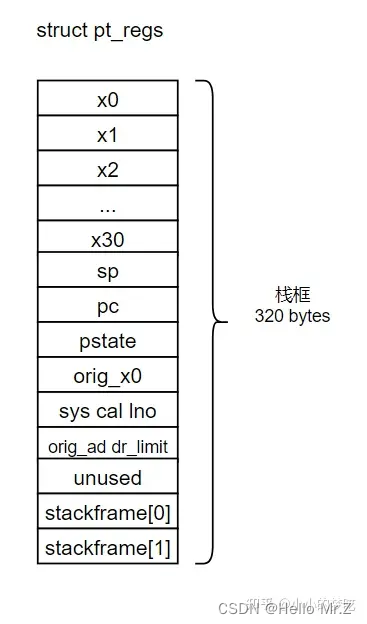

3、异常进入

硬件执行:

1、把PSTATE寄存器保存到对应的目标等级的SPSR_ELx;

2、把返回地址保存到目标异常等级的ELR_ELx;

3、把PSTATE的D/A/I/F标志置1;

4、同步异常将异常原因写入ESR_ELx;

5、切换SP为SP_ELx或SP_EL0。

软件执行:

1、软件压栈。

4、异常退出

硬件执行:

1、从ELR_ELx中恢复PC指针;

2、从SPSR_ELx中恢复PSTATE,其中SPSR.M[3:0]记录了返回哪个异常等级,SPSR.M[4]记录了返回哪个执行状态。

软件执行:

1、软件出栈;

2、执行ERET指令退出异常。

这里异常返回与函数返回不一样,函数返回使用ret指令,返回使用的LR是X30(LR)。

5、安全模式切换

安全模式切换只能在EL3进行,步骤如下(EL1_S->EL1_NS)

1、使用SMC指令,进入到EL3;

2、改变SCR_EL3.NS的值,将NS位写1;

3、然后从EL3返回(ERET)到EL1。

6、栈帧

7、异常向量

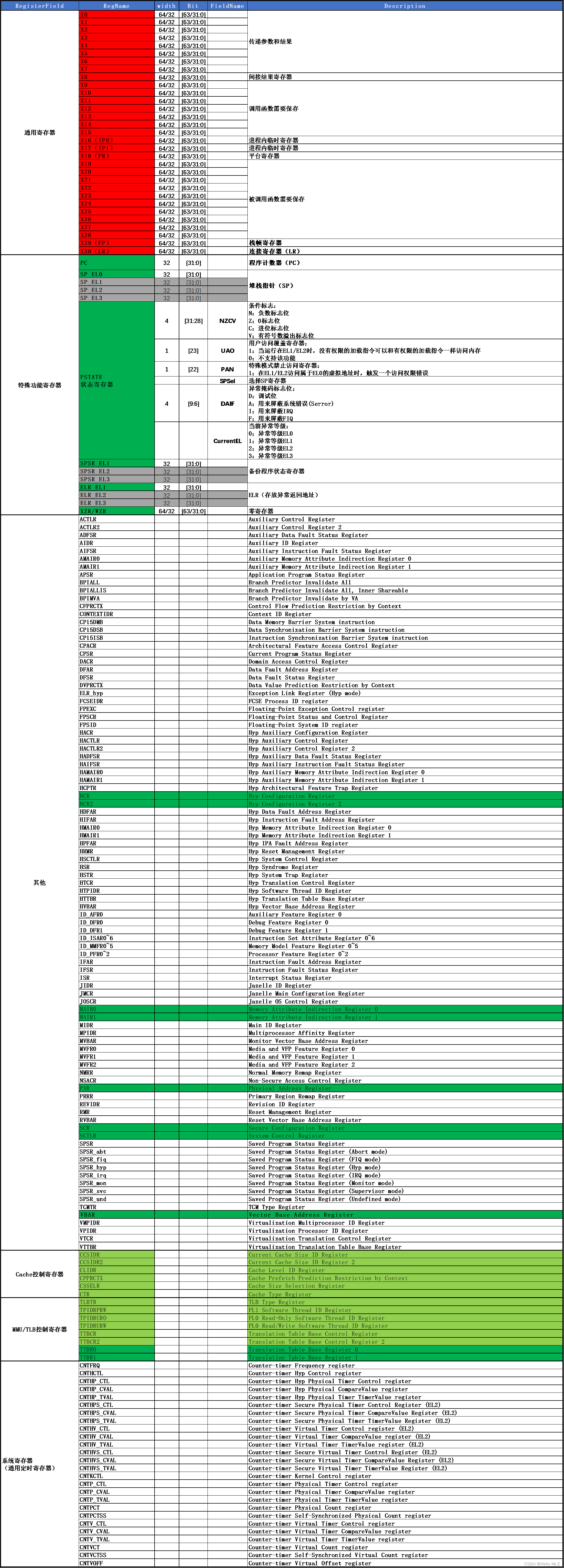

8、内核寄存器

013 - ARM64的异常处理(Exception)机制

ARM64基础12:ARM64的异常模式及异常向量表

ARMv8的异常等级(Exception Level)以及执行状态(AArch64/AArch32)

异常等级切换

ARM处理器的secure 和 Non-secure模式切换方法:SMC指令和SCR.NS