一、异步FIFO需要注意的问题

所谓异步FIFO,指的是写时钟与读时钟可以不同步,读时钟可以比写时钟快,反之亦然。思考一下,这样会直接地造成两个问题:

1. 读满或者写满

由于异步FIFO的基本存储单元是双端口RAM,因此读写速率不一致,就会造成读满或者写满的问题。

2. 跨时钟域的同步

为了判断读满、写满的情况,势必需要将写指针(告诉读模块,写到哪个位置了,我还可不可以继续读?)同步到读模块,(或者读指针同步到写模块,通知写模块,现在读到哪里了,我还能不能继续写啦?如果还没读,我再写一轮不就把数据覆盖了啊?),这样就会存在跨时钟域的同步问题。

因此,针对上述问题,我们解决办法如下:

3. 针对问题一,将读指针与写指针进行比较,产生读空、写满标志。

思考一下如何判断读空、写满标志呢,假设有一个深度为8的RAM,那么其地址线的宽度为3,这里我们扩展一位,让最高位作为读空、写满标志,(实际给到RAM的只有[2:0]),其原理如下

假设写指针写到了0111,此时读指针也读到了0111,意味着读指针追上了写写指针,那么此时就是读空了;

假设写指针写到了1000(实际上是第二轮的000),此时读指针读到了000(第一轮的000),那么就是写满。

因此,可以总结:

当最高位相同,其余位相同认为是读空

当最高位不同,其余位相同认为是写满

4. 针对问题二:两级寄存器同步 + 格雷码

我们将读写指针编码为Gray码并打两拍进行同步。采用Gray码的原因可参考上一篇博客,简单来说就是Gray码相邻两个编码之间只存在一个bit变化,避免多个bit同时跳变的问题。再进行两拍同步就可以将读写指针进行异步时钟同步化了。

5. 由于问题二,采用Gray码,导致我们判断读空及写满的逻辑需要稍微改变下了:

我们观察一下基于gray码的读空、写满的情况:

因此,用格雷码判断是否为读空或写满时应看最高位和次高位是否相等:即:

当最高位和次高位相同,其余位相同认为是读空

当最高位和次高位不同,其余位相同认为是写满

二、异步FIFO架构

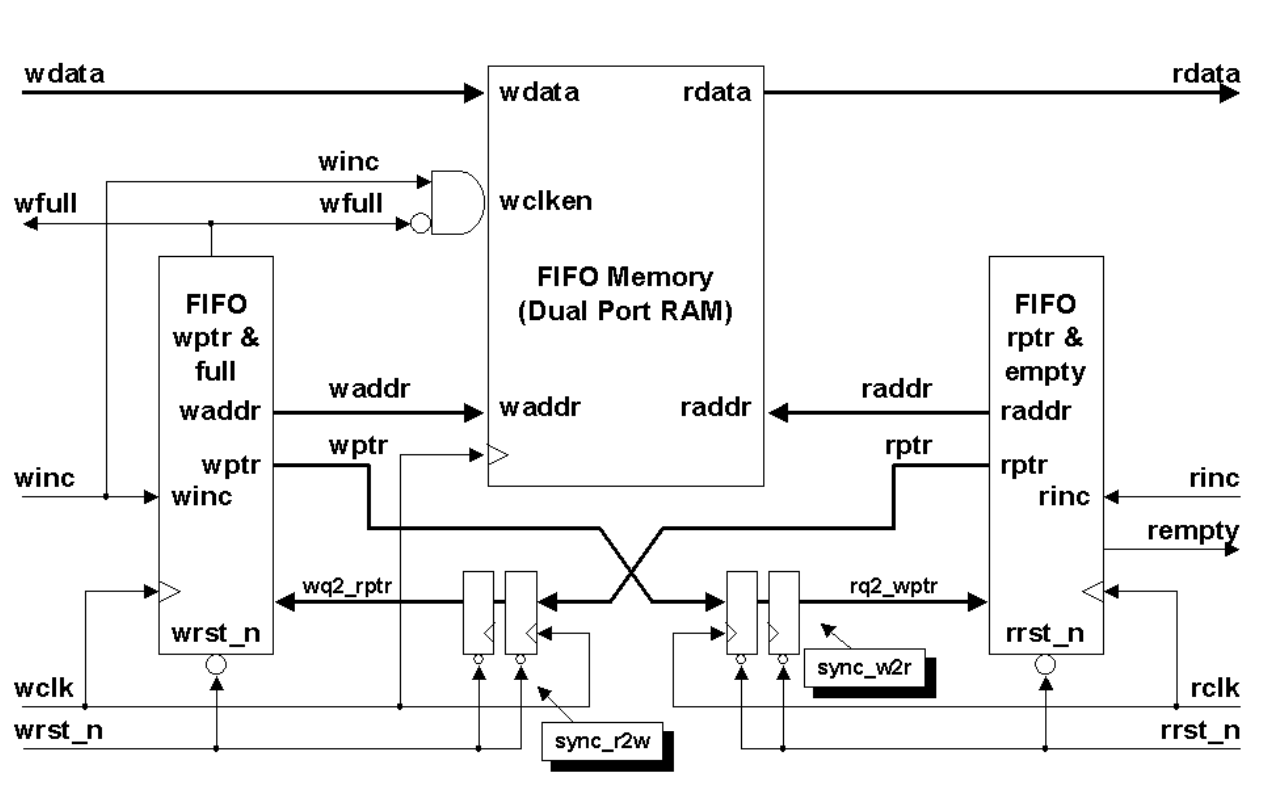

根据上述讨论,我们可以总结一个异步FIFO的架构包括以下几个部分:

- 双端口RAM,作为FIFO的存储体。可以采用硬件描述的方式描述一个RAM,也可以采用IP核、原语的方式。

- FIFO写模块,用于产生写地址,写使能,写满等信号

- FIFO读模块,用于产生读地址,读使能、读空等信号。

- Gray码转换模块,用于自然二进制与Gray码转换

- 时钟同步,用于将读写指针打拍同步。

结构框架如下:

三、reference

《Simulation and Synthesis Techniques for Asynchronous FIFO Design》Clifford E. Cummings, Sunburst Design, Inc.