目录

[一、D 锁存器(D Latch)](#一、D 锁存器(D Latch))

[1. 原理与结构](#1. 原理与结构)

[2. 工作特性 :电平出发:EN高电平:随D变化而变化, EN低电平:保持上一个状态。](#2. 工作特性 :电平出发:EN高电平:随D变化而变化, EN低电平:保持上一个状态。)

[3. 实际器件](#3. 实际器件)

[二、D 触发器(D Flip-Flop)](#二、D 触发器(D Flip-Flop))

[1. 原理与结构](#1. 原理与结构)

[2. 工作特性:边缘触发采样,上升沿到来前,保持上一个时刻状态](#2. 工作特性:边缘触发采样,上升沿到来前,保持上一个时刻状态)

[3. 分类](#3. 分类)

[1. 74HC74(双 D 触发器)](#1. 74HC74(双 D 触发器))

[2. 74LS373(八 D 透明锁存器)](#2. 74LS373(八 D 透明锁存器))

题目汇总版--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客

【硬件-笔试面试题】硬件/电子工程师,笔试面试题-42,(知识点:D触发器,D锁存器,工作原理,区别)

1、题目

简述D 触发器和 D 锁存器的原理,以及它们区别是什么?

2、解答

D 触发器和 D 锁存器是数字电路中的基础存储元件,广泛应用于时序逻辑设计。以下从原理、结构、应用和实际器件等方面进行详细分析:

一、D 锁存器(D Latch)

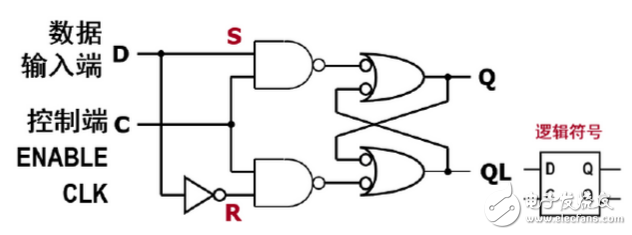

1. 原理与结构

-

电平触发 :D 锁存器是电平敏感的存储元件,在使能信号(EN)有效期间(通常为高电平),输出 Q 跟随输入 D 变化;当 EN 无效时,输出保持最后状态。

-

基本结构 :由门电路组成,常见的是SR 锁存器加控制门。

-

电路图示例 :

-

工作过程 :当使能信号(EN,Enable)为高电平时,D 锁存器处于透明状态,输出端 Q 会跟随输入信号 D 的变化而变化,即输入信号 D 可以直接传输到输出端 Q;

-

当使能信号 EN 变为低电平时,锁存器进入锁存状态,此时无论输入信号 D 如何变化,输出端 Q 都将保持使能信号 EN 变为低电平前那一刻的状态,直到下一次使能信号 EN 再次变为高电平 。

-

特性方程 :\(Q(t+1) = \begin{cases} D, & \text{当EN=1时 ,随D变化而变化} \\ Q(t), & \text{当EN=0时,保持上一个高电平的状态} \end{cases}\)

2. 工作特性 :电平出发:EN高电平: 随D变化而变化,EN低电平: 保持上一个状态。

- 透明性 :EN=1 时,输出对输入 "透明",称为透明锁存器。

- 应用场景 :

- 数据暂存(如地址锁存)。

- 总线隔离(通过 EN 控制数据传输)。

- 异步电路(无需时钟同步)。

3. 实际器件

- 74HC75:四 D 锁存器(带使能端),TTL/CMOS 兼容。

- 74LS373:八 D 透明锁存器(三态输出),常用于地址 / 数据总线隔离。

二、D 触发器(D Flip-Flop)

1. 原理与结构

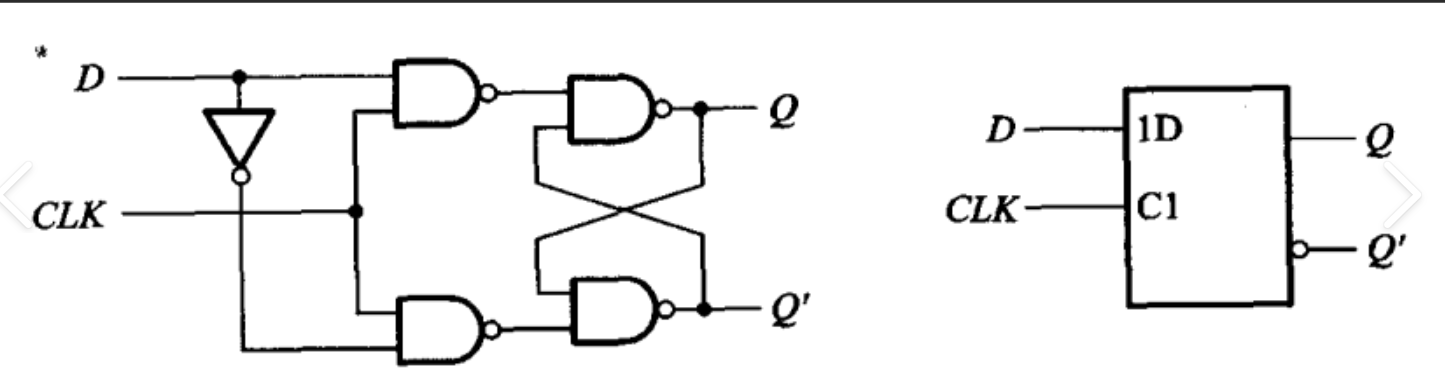

- 边沿触发 :D 触发器是时钟边沿敏感的存储元件,仅在时钟信号(CLK)的上升沿(或下降沿)采样 D 值并更新输出。

- 基本结构 :

- 主从触发器:由两个 D 锁存器级联组成,CLK 控制主锁存器接收 D,CLK' 控制从锁存器输出。

- 维持阻塞结构:通过反馈路径防止多次触发,常见于集成电路。

- 工作过程 :在时钟信号(CLK)的上升沿到来之前,主触发器根据输入信号 D 进行状态更新,此时从触发器处于保持状态。

- 当时钟信号 CLK 的上升沿到来时,主触发器停止接收输入信号 D,其状态被传递到从触发器,从触发器输出更新后的状态,此时输出端 Q 和 Q'(反相输出)反映当前 D 输入在时钟上升沿时刻的状态。

- 在时钟信号 CLK 的其他时刻,无论输入信号 D 如何变化,触发器的输出状态都保持不变,直到下一个时钟上升沿的到来。

2. 工作特性:边缘触发采样, 上升沿到来前,保持上一个时刻状态

- 边沿采样:仅在 CLK 边沿采样 D,避免毛刺干扰,提高可靠性。

- 特性方程 :\(Q(t+1) = D, \quad \text{在CLK边沿触发时}\) :输出上一个时刻的状态

- 异步控制端 :

- 置位(Set):强制 Q=1(低电平有效)。

- 复位(Reset):强制 Q=0(低电平有效)。

3. 分类

- 上升沿触发:CLK 从 0→1 时采样(如 74HC74)。

- 下降沿触发:CLK 从 1→0 时采样(如 74HC112)。

- 带使能端:如 74HC175(四 D 触发器,公共时钟和复位)。

三、关键区别对比

| 特性 | D 锁存器 | D 触发器 |

|---|---|---|

| 触发方式 | 电平触发(EN 控制) | 边沿触发(CLK 控制) |

| 透明性 | EN=1 时透明,输出随 D 变化 | 仅在边沿采样,其余时间保持 |

| 抗干扰能力 | 较弱(EN 有效期间易受干扰) | 强(仅对边沿敏感) |

| 应用场景 | 数据暂存、异步电路 | 同步时序电路(计数器、寄存器) |

| 典型器件 | 74HC75、74LS373 | 74HC74、74HC175 |

四、实际器件举例

1. 74HC74(双 D 触发器)

-

特性 :

- 上升沿触发,带异步置位(SET)和复位(RESET)。

- 电源范围:2V~6V,TTL/CMOS 兼容。

-

引脚图 :

plaintext

┌───────┐ 1│D1 Q1│14 VCC 2│CLK1 │13 Q1' 3│SET1 │12 D2 4│RESET1│11 CLK2 5│Q1' │10 SET2 6│ │9 RESET2 7│GND │8 Q2 └───────┘ -

应用:分频器、同步寄存器。

2. 74LS373(八 D 透明锁存器)

- 特性 :

- 三态输出,OE(输出使能)低电平有效。

- LE(锁存使能)高电平时透明,低电平时锁存。

- 应用:地址锁存器(如 8051 单片机的 P0 口扩展)。

五、应用场景选择

- 选 D 触发器 :

- 同步电路设计(如时钟驱动的计数器、移位寄存器)。

- 高速系统(需避免电平触发导致的竞争冒险)。

- 需严格时序控制的场景(如数据同步、状态机)。

- 选 D 锁存器 :

- 数据暂存(如地址 / 数据缓冲)。

- 异步控制(如使能信号控制的临时存储)。

- 简化电路(无需时钟,降低功耗)。

六、注意事项

- 亚稳态风险 :

- 当 D 信号在 CLK 边沿附近变化时,触发器可能进入亚稳态(输出不确定)。

- 解决方案:增加同步器(级联多个触发器)。

- 建立时间(Setup Time) :

- D 信号需在 CLK 边沿前保持稳定的最小时间。

- 保持时间(Hold Time) :

- D 信号需在 CLK 边沿后保持稳定的最小时间。

总结

D 锁存器和 D 触发器是时序逻辑的基础,前者适合异步、暂存场景,后者适合同步、可靠存储。实际应用中需根据触发方式、抗干扰性和时序要求合理选择器件。

题目汇总--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客