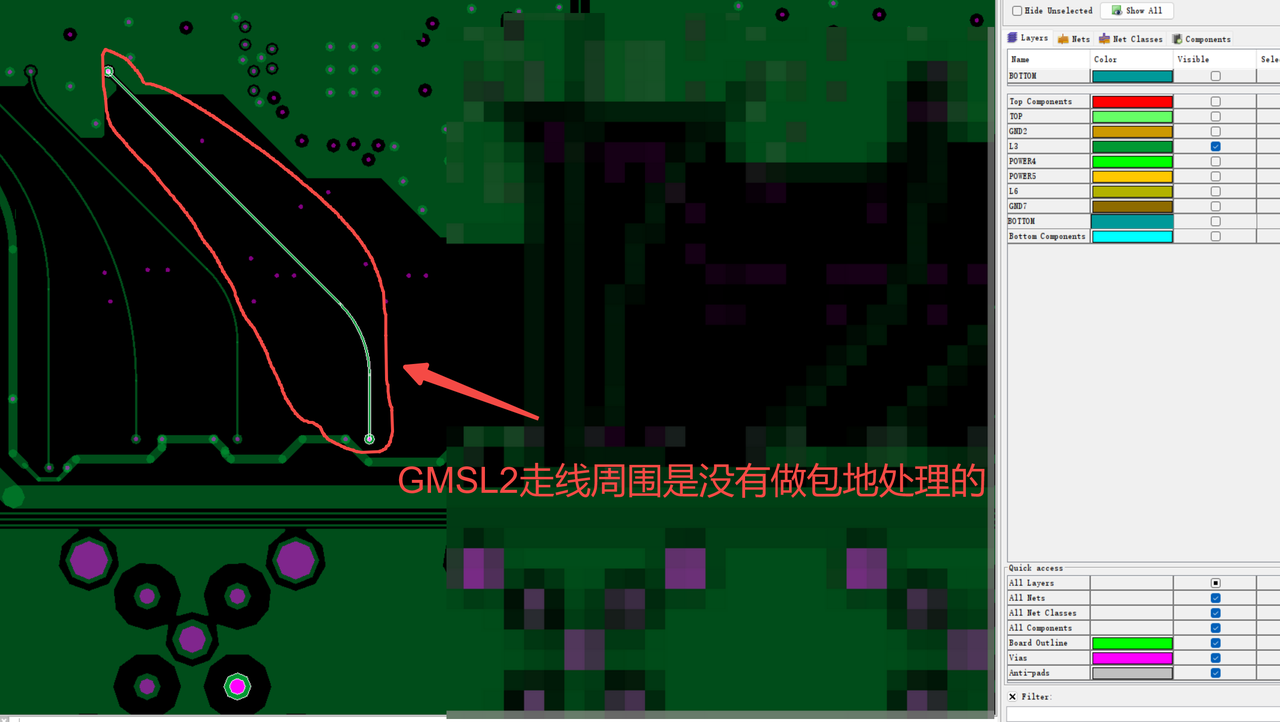

一,RX0_96712_FAKRA_1测试结果是不过的,我们看下把这个GMSL2走线周围做包地处理是否对其S21和S11性能有所改善?

1,

(初始版本的PCB)

(优化后版本的PCB)

(优化后版本的PCB)

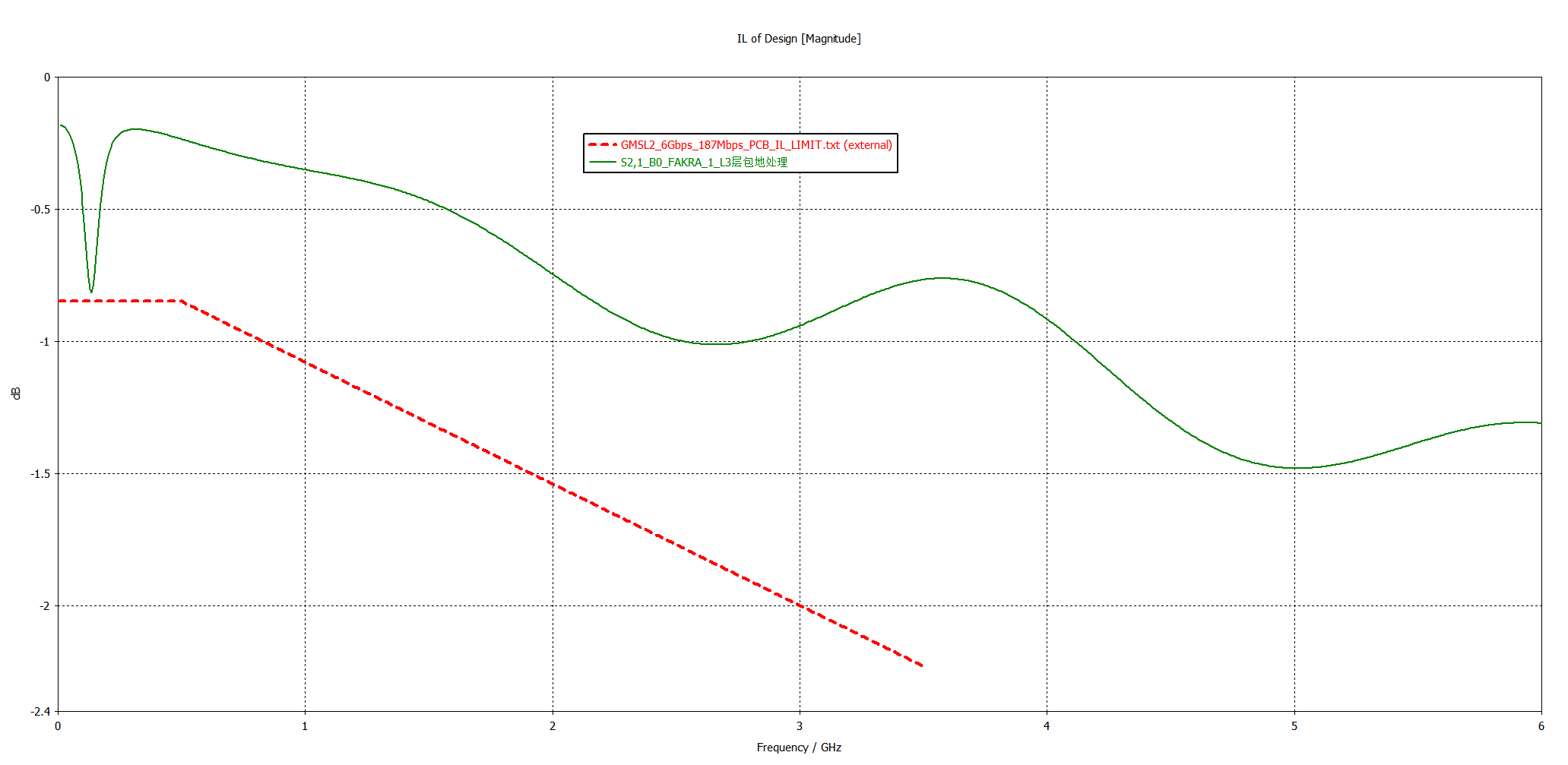

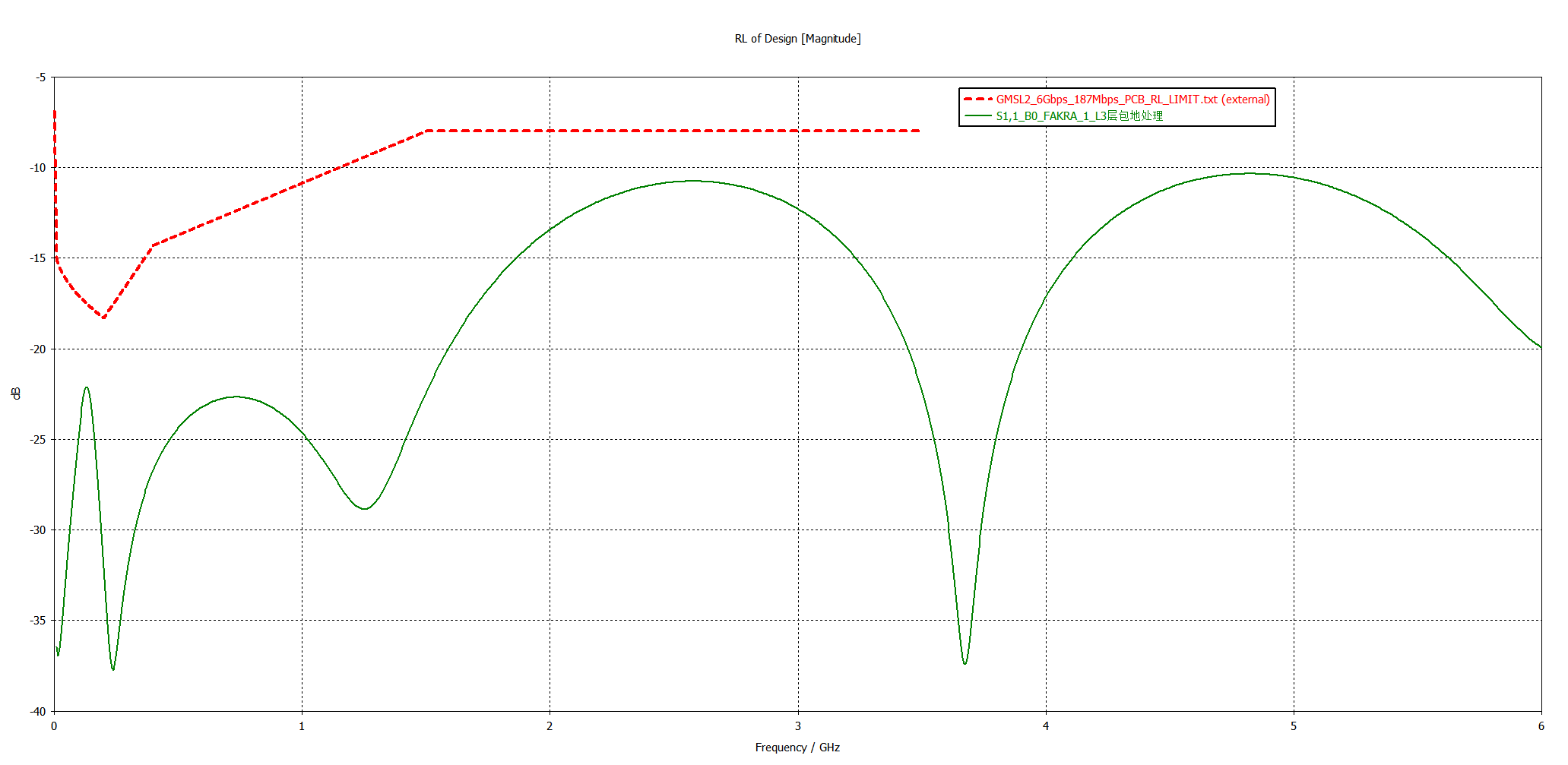

二,优化后看下其仿真效果:

1, RX0_96712_FAKRA_1_S21:PASS的

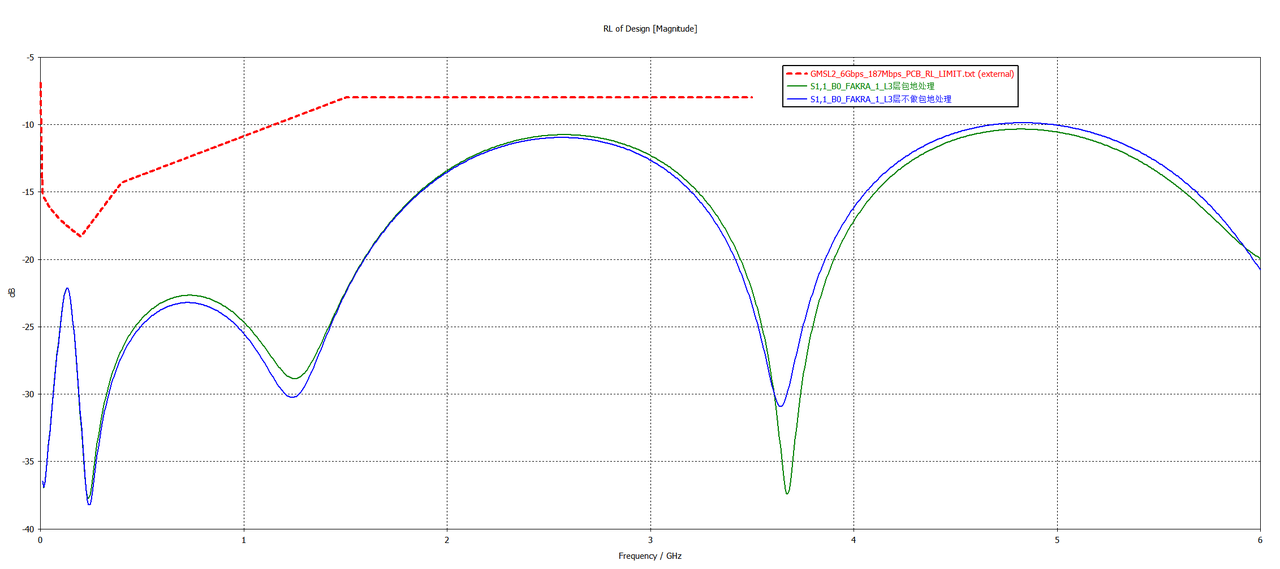

2, RX0_96712_FAKRA_1_S11: PASS的

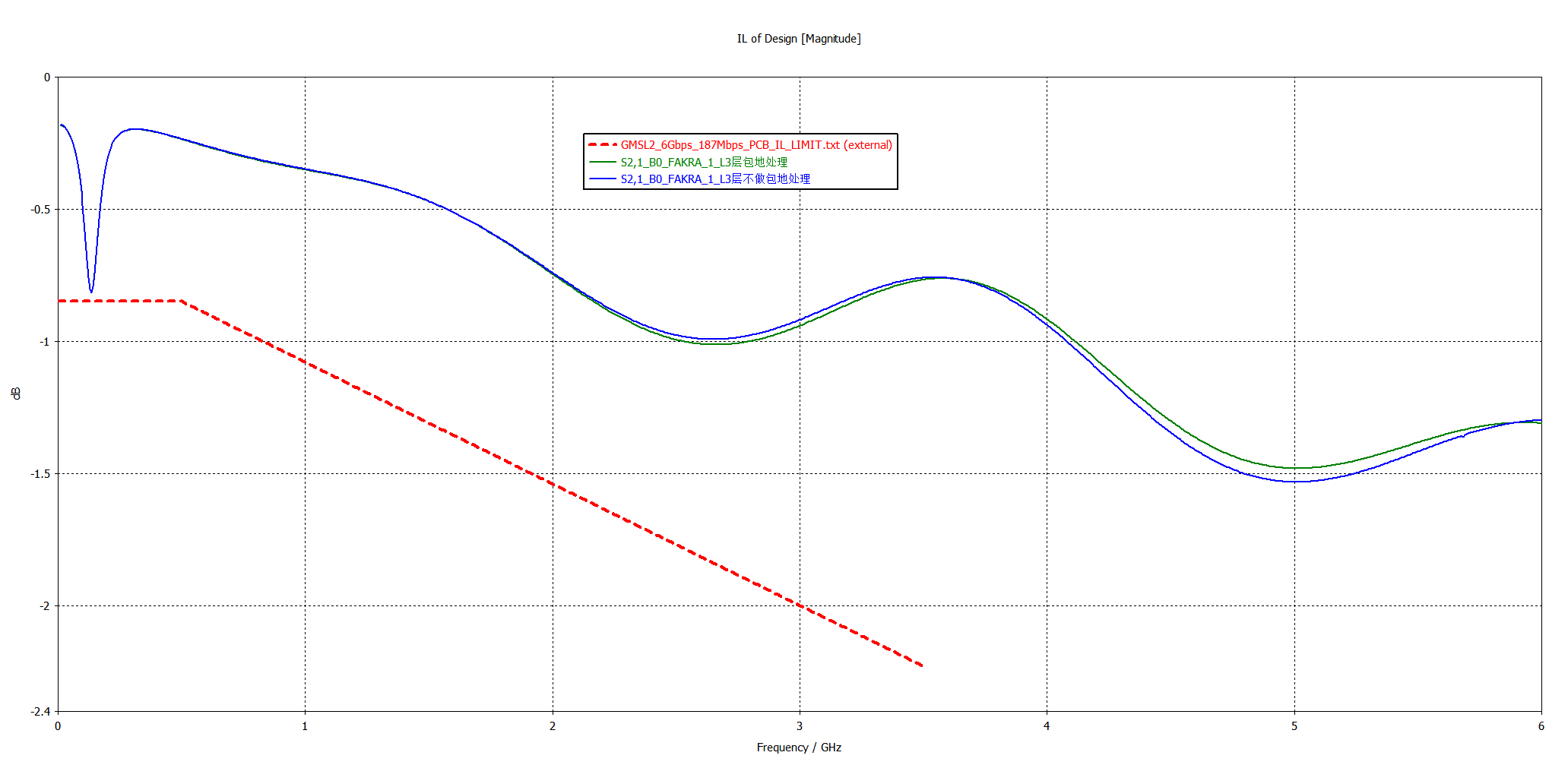

3, RX0_96712_FAKRA_1_S21对比之前初始版本:

4, RX0_96712_FAKRA_1_S11对比之前初始版本:

三,分析总结:

对于我们单板上的GMSL2走线上做包地处理的话改善不是很多,尤其在低频阶段,主要是因为在损耗中,我们的低频段(如 <1GHz)辐射损耗占比低,包地对插损改善有限,反而可能因寄生参数增加损耗;高频段(如> 5GHz)辐射损耗显著,包地的屏蔽作用更能体现价值。

所以我们在PCB设计的时候,需要把高速信号线做包地处理来改善其插损和回损,需满足以下设计原则,否则可能适得其反:

-

阻抗连续性优先: 包地需纳入特性阻抗计算模型(如使用仿真工具验证),确保信号线与包地的间距、地平面厚度、板材介电常数等参数匹配目标阻抗(如 50Ω),避免阻抗突变。

-

接地平面连续完整: 包地需与主接地平面通过密集过孔(如每隔 1/20 波长)连接,避免形成 "悬浮地" 或 "天线结构"(否则会增加辐射损耗或反射)。

-

合理间距: 包地与信号线的距离需满足 "3W 原则"(至少 3 倍线宽),或根据阻抗要求调整,避免过度耦合导致阻抗偏移。

-

适配频率范围: 低频段(如 <1GHz)辐射损耗占比低,包地对插损改善有限,反而可能因寄生参数增加损耗;高频段(如> 5GHz)辐射损耗显著,包地的屏蔽作用更能体现价值。

四、结论

合理的包地处理可以改善高速 PCB 走线的插损和回损性能,但需满足阻抗连续、接地完整、间距合理等设计要求:

-

对回损:主要通过稳定特性阻抗减少反射,设计不当会因阻抗突变恶化回损;

-

对插损:主要通过减少辐射损耗改善衰减,但需避免因寄生参数增加导体 / 介质损耗。

所以在实际设计中,我们还是需结合一些仿真的工具来验证包地前后的插损S21 / 回损曲线S11的性能,并根据具体频率、板材、布线长度优化方案。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!