目录

- 1、前言:EMIF在FPGA+DSP架构中的作用

- 2、相关方案推荐

- 3、工程详细设计方案

- 4、工程源码1详解:FPGA逻辑工程

- 5、工程源码2详解:DSP裸机工程

- [6、工程源码3详解:DSP RTOS系统工程](#6、工程源码3详解:DSP RTOS系统工程)

- 7、工程移植说明

- 8、上板调试验证

- 9、工程代码获取

FPGA实现EMIF接口与DSP交互,FPGA+DSP异构方案,提供3套工程源码和技术支持

1、前言:EMIF在FPGA+DSP架构中的作用

EMIF简介:

EMIF(External Memory Interface)是一种并行存储器接口标准,用于连接处理器(如DSP/CPU)与外部存储设备(SRAM/SDRAM/Flash)或FPGA等协处理器。其核心是通过地址/数据总线+控制信号实现高速数据交换,典型特性如下:

DSP+FPGA架构中EMIF的核心作用如下:

高速数据交换通道

实时数据流传输:FPGA作为数据采集前端(如ADC采样),通过EMIF将GB/s级数据直通DSP处理,避免总线竞争瓶颈。

硬件加速协同:DSP将算法密集型任务(如FFT矩阵)传输至FPGA硬件加速,结果经EMIF回传。

内存映射扩展

统一寻址空间:DSP通过EMIF将FPGA内部RAM映射到自身地址空间,实现寄存器级访问(如配置FPGA工作模式)。

大容量缓存:连接FPGA板载DDR,为DSP扩展存储池(如雷达信号历史数据缓存)。

低延迟控制

硬件触发联动:DSP通过EMIF发送32ns级脉冲信号触发FPGA采集动作(如激光雷达同步)。

中断响应:FPGA用EMIF的WAIT引脚向DSP发起中断(如帧数据就绪)。

EMIF在DSP+FPGA架构的五大优势

极致带宽利用率

以TI C6678 DSP + Xilinx Kintex-7为例,EMIF突发传输效率达98%

确定性延迟

相比PCIe/USB等协议,消除报文封装/拆解带来的微秒级抖动,满足实时控制需求(如电机伺服系统)。

硬件简化设计

免协议栈:直连电路省去PHY芯片/协议控制器(如PCIe Endpoint),降低BOM成本30%。

布线简单:单端信号布线(DDR需差分),减少PCB层数需求。

低功耗特性

EMIF与PCIE功耗对比如下:

开发便捷性

DSP端:直接操作内存地址(如*(volatile uint32_t*)0x80000000 = data)

FPGA端:用Verilog实现双口RAM接口;

典型应用场景

EMIF接口在FPGA+DSP架构中有广泛的工业应用场景,比如雷达信号处理系统、工业运动控制、医疗影像设备等;

总结

在DSP+FPGA异构架构中,EMIF的核心价值在于:

1、提供纳秒级延迟的确定性数据通道

2、实现内存级协同,突破传统总线带宽限制

3、以极简硬件达成GB/s级传输效率

尤其适合实时信号处理(雷达/医疗影像)、高速控制(机器人/数控)等场景。随着JESD204B等高速接口普及,EMIF仍将在追求低抖动、高可靠的嵌入式系统中不可替代。

工程概述

本文详细描述了Xilinx的7系列FPGA实现FPGA实现EMIF接口与DSP交互;以下从FPGA工程和DSP工程两个方向描述整个设计:

FPGA工程

FPGA工程基于BRAM模拟ASRAM存储设备,实现EMIF接口与DSP交互;EMIF接口时序以EMIF标准协议为基础,使用纯verilo代码实现EMIF接口时序,包括数据读写与地址映射;基于BRAM的数据缓存用来存储EMIF接口数据,调用BRAM_SINGLE_MACRO原语实现BRAM部署,BRAM数据位宽设为16bit,地址位宽设为10bit,数据深度设为1024,则总容量为 16bit x 1024 = 2048 Byte;

DSP工程

DSP工程实现EMIF接口数据读写和数据正确性对比,充当ASRAM读写控制器;DSP工程分为裸机工程和RTOS系统工程,裸机工程不带操作系统,实时性更好,RTOS系统工程带轻量版RTOS操作系统,稳定性更好;DSP工程模拟了EMIF接口时序,调用TI系列DSP特有的EDMA3实现数据搬运,程序中对EMIF接口数据配置读写空间,DSP通过CPU创建2048 Byte的累加数,再调用EDMA3发起写操作,一次性通过EMIF接口向FPGA写入2048 Byte的累加数,然后再通过EMIF接口读取2048 Byte数据,再调用EDMA3发起读操作,在CPU中进行读写数据对比和读写速率计算,最后将对比结果和速率通过串口打印观察;

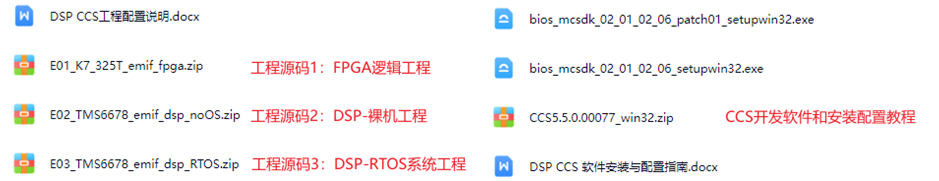

针对市场主流需求,本博客提供3套工程源码,具体如下:

现对上述3套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx公司的XC7K325T-2FFG676I;FPGA工程基于BRAM模拟ASRAM存储设备,实现EMIF接口与DSP交互;

工程源码2

开发板DSP型号为TI公司的TMS320C6678;DSP工程实现EMIF接口数据读写和数据正确性对比,充当ASRAM读写控制器;本套工程为CCS 裸机工程,不带操作系统,实时性更好;

工程源码3

开发板DSP型号为TI公司的TMS320C6678;DSP工程实现EMIF接口数据读写和数据正确性对比,充当ASRAM读写控制器;本套工程为CCS RTOS工程,带RTOS操作系统,稳定性更好;

本文详细描述了FPGA实现EMIF接口与DSP交互的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的高速接口领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

我这里已有的FPGA+DSP异构方案

目前我这里有大量FPGA+DSP异构方案的工程源码,包括EMIF、SRIO、PCIE等等,对FPGA+DSP异构方案有需求的兄弟可以去看看:

直接点击前往

3、工程详细设计方案

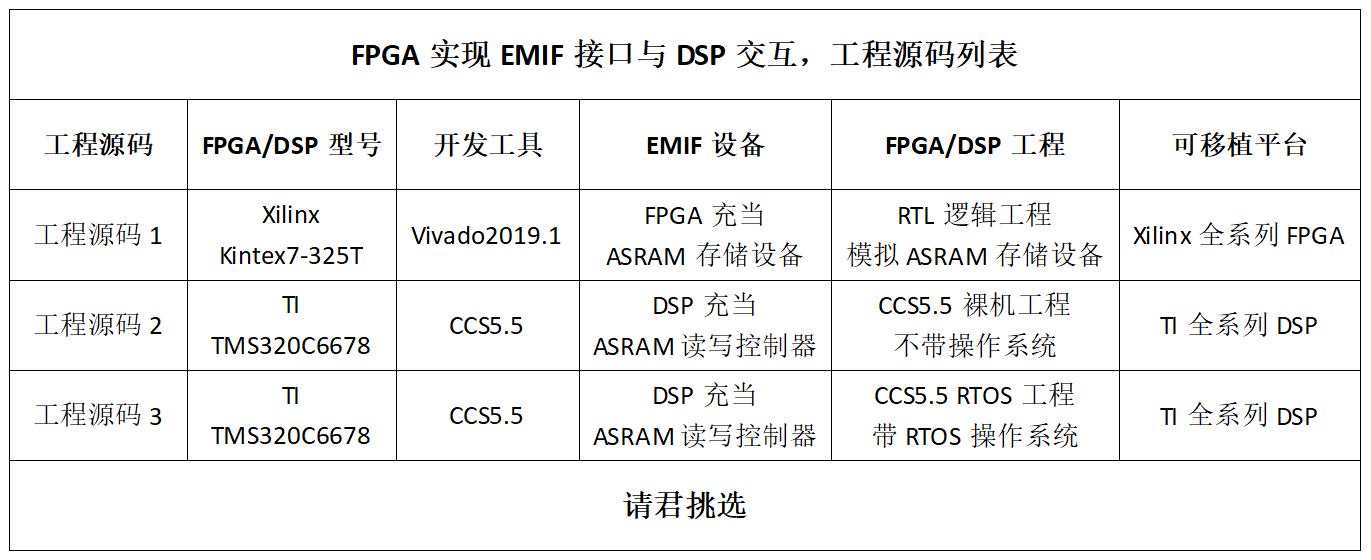

工程设计原理框图

工程设计原理框图如下:

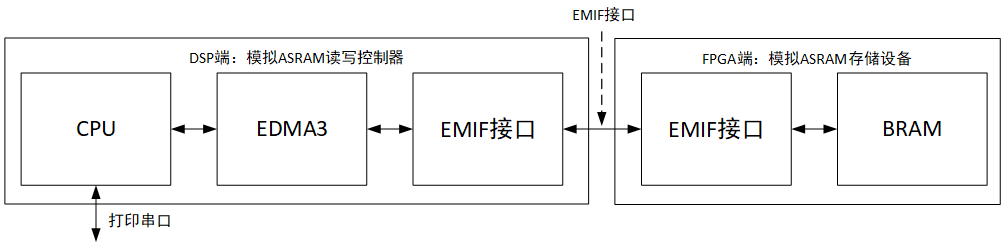

FPGA端工程

FPGA工程基于BRAM模拟ASRAM存储设备,实现EMIF接口与DSP交互;EMIF接口时序以EMIF标准协议为基础,使用纯verilo代码实现EMIF接口时序,包括数据读写与地址映射;基于BRAM的数据缓存用来存储EMIF接口数据,调用BRAM_SINGLE_MACRO原语实现BRAM部署,BRAM数据位宽设为16bit,地址位宽设为10bit,数据深度设为1024,则总容量为 16bit x 1024 = 2048 Byte;FPGA端工程源码如下:

DSP端工程

DSP工程实现EMIF接口数据读写和数据正确性对比,充当ASRAM读写控制器;DSP工程分为裸机工程和RTOS系统工程,裸机工程不带操作系统,实时性更好,RTOS系统工程带轻量版RTOS操作系统,稳定性更好;DSP工程模拟了EMIF接口时序,调用TI系列DSP特有的EDMA3实现数据搬运,程序中对EMIF接口数据配置读写空间,DSP通过CPU创建2048 Byte的累加数,再调用EDMA3发起写操作,一次性通过EMIF接口向FPGA写入2048 Byte的累加数,然后再通过EMIF接口读取2048 Byte数据,再调用EDMA3发起读操作,在CPU中进行读写数据对比和读写速率计算,最后将对比结果和速率通过串口打印观察;

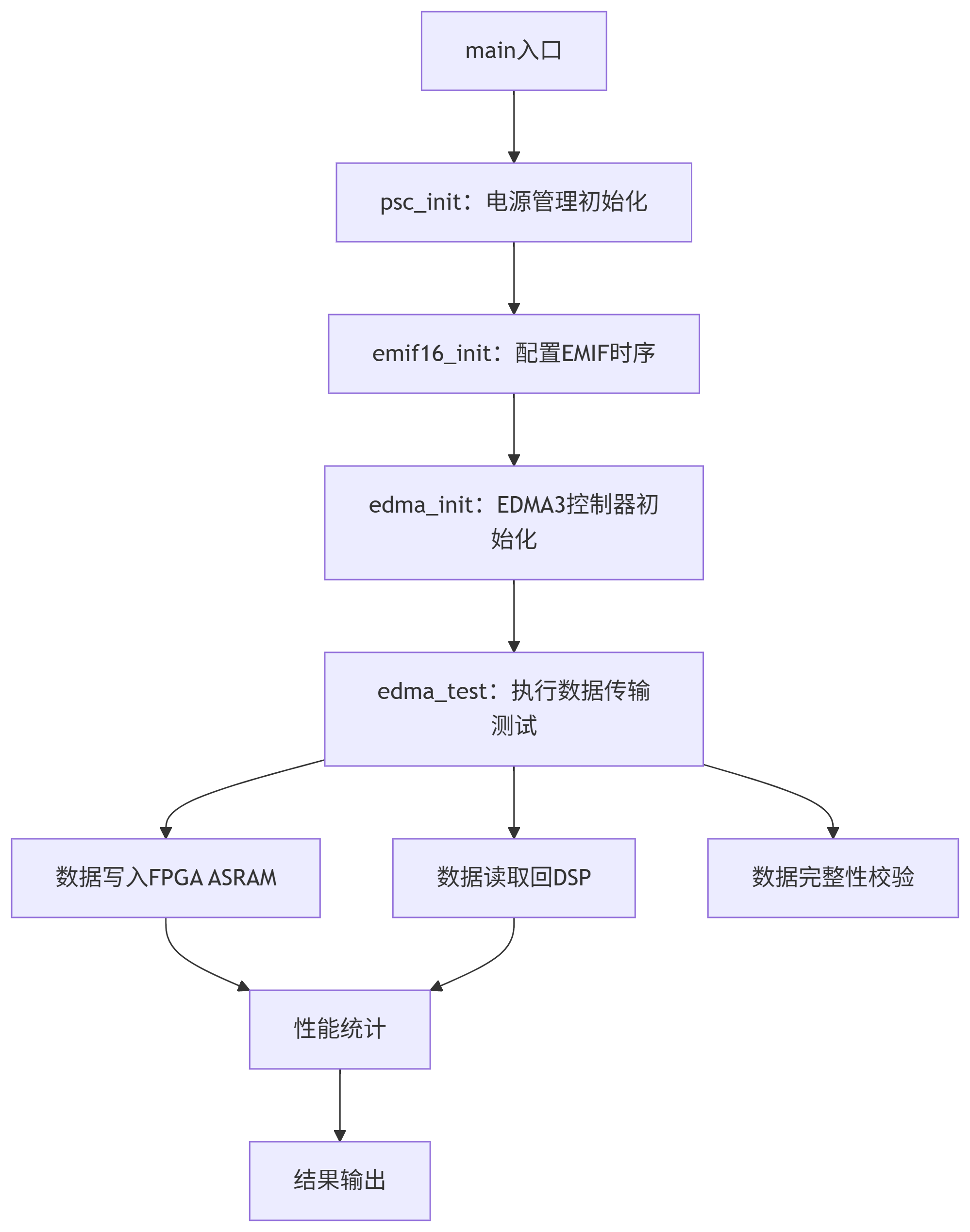

DSP端工程流程图如下:

DSP端EMIF16写数据关键细节

1、时序配置(emif16_init函数)

配置CE1空间时序参数(以166MHz时钟为例):

c

hEmif16Cfg->A1CR =

(1 << CSL_EMIF16_A1CR_WSETUP_SHIFT) | // 写建立时间=1周期(6ns)

(2 << CSL_EMIF16_A1CR_WSTROBE_SHIFT) | // 写选通时间=3周期(18ns)

(1 << CSL_EMIF16_A1CR_WHOLD_SHIFT) | // 写保持时间=1周期(6ns)

(1 << CSL_EMIF16_A1CR_ASIZE_SHIFT); // 16位总线2、数据写入流程(edma_test函数)

步骤1:准备测试数据

c

for(i=0; i<test_size/2; i++)

write_buffer[i] = i; // 填充0,1,2,...1023步骤2:配置EDMA写参数

c

myParamSetup.option = CSL_EDMA3_OPT_MAKE(

...,

CSL_EDMA3_SYNC_AB, // AB同步模式

CSL_EDMA3_ADDRMODE_INCR, // 源地址递增

CSL_EDMA3_ADDRMODE_INCR // 目标地址递增

);

myParamSetup.srcAddr = (uint32_t)edma_write_buffer; // DSP内存地址

myParamSetup.dstAddr = (uint32_t)dev_addr; // EMIF地址(0x74000000)

myParamSetup.aCntbCnt = CSL_EDMA3_CNT_MAKE(2048,1);// 传输2048字节步骤3:触发EDMA传输

c

CSL_edma3HwChannelControl(hChannel, CSL_EDMA3_CMD_CHANNEL_SET, NULL);步骤4:等待传输完成

c

while(!(regionIntr.intr & 0x1)) asm(''nop''); // 轮询中断标志DSP端关键代码解析

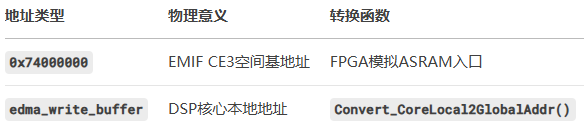

1、地址转换(DSP↔FPGA)

2、性能计算原理

c

t_start = _itoll(TSCH, TSCL); // 读取时间戳计数器

// ...传输操作...

t_cost = _itoll(TSCH, TSCL) - t_start; // 计算耗时周期数

w_rate = (test_size * main_pll_freq) / t_cost / 1e6; // MB/s

3、数据校验机制

c

for(i=0; i<1024; i++) { // 1024个16位数据

if(write_buffer[i] != read_buffer[i]) {

err_count++;

// 打印首个错误位置

}

}DSP端测试结果输出

举例执行TEST_TIMES=30000次后的典型输出:

c

=== EMIF16 ram write and read test completed with 0 errors.

average write rate: 58.72 MB/s, average read rate: 59.15 MB/s4、工程源码1详解:FPGA逻辑工程

开发板FPGA型号:Xilinx--XC7K325T-2FFG676I;

FPGA开发环境:Vivado2019.1;

输入输出接口:EMIF;

实现功能:FPGA模拟ASRAM存储设备;

工程作用:此工程目的是让读者掌握FPGA实现EMIF接口与DSP交互的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

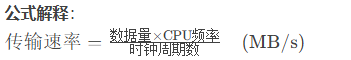

工程的资源消耗和功耗如下:

5、工程源码2详解:DSP裸机工程

开发板DSP型号:TI--TMS320C6678;

FPGA开发环境:CCS5.5;

输入输出接口:EMIF;

实现功能:DSP模拟ASRAM读写控制器;

DSP工程操作系统:裸机,无操作系统;

工程作用:此工程目的是让读者掌握FPGA实现EMIF接口与DSP交互的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

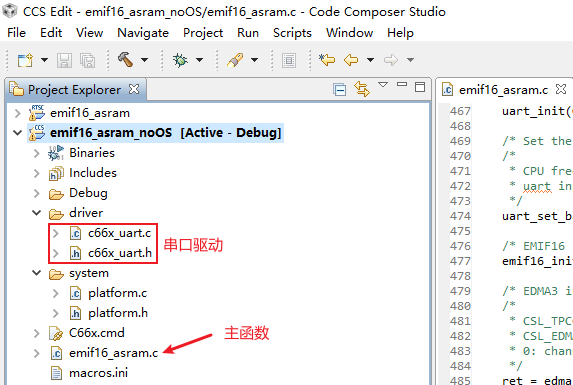

DSP裸机工程源码架构如下:

6、工程源码3详解:DSP RTOS系统工程

开发板DSP型号:TI--TMS320C6678;

FPGA开发环境:CCS5.5;

输入输出接口:EMIF;

实现功能:DSP模拟ASRAM读写控制器;

DSP工程操作系统:RTOS操作系统;

工程作用:此工程目的是让读者掌握FPGA实现EMIF接口与DSP交互的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

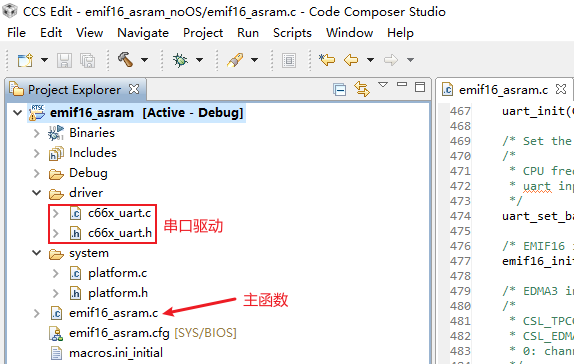

DSP RTOS系统工程源码架构如下:

7、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件-->另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

8、上板调试验证

准备工作

需要准备的器材如下:

FPGA+DSP异构开发板;

测试用PC电脑;

串口线;

程序下载bit

步骤如下:(顺序一定要对)

1、先下载FPGA程序

2、再下载DSP程序

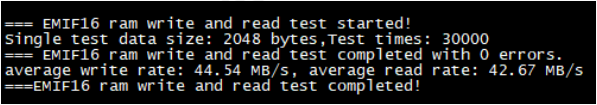

DSP裸机工程测试

DSP裸机工程测试结果如下:

平均写速率:44.54MB/s

平均读速率:42.67MB/s

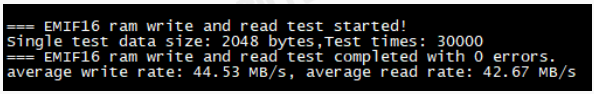

DSP RTOS系统工程测试

DSP RTOS系统工程测试结果如下:

平均写速率:44.53MB/s

平均读速率:42.67MB/s

9、工程代码获取

工程代码如下: