半导体产业链:

Design → Fab → Wafer Sort → Assembly → Final Test → System

一、设计阶段数据

1. 电路设计数据

a. 来源

++EDA++ 工具(Cadence,Synopsys)、++RTL代码++ 、++IP核库++、仿真日志

b. 用途

定义芯片功能、验证逻辑正确性、优化功耗和时序

c. 分析方法

- 静态时序分析(STA):验证时序约束

- 功耗分析:通过仿真工具(如PrimePower)计算动态/静态功耗

- 形式验证:数学方法验证RTL与网表一致性

o. 注解

++① EDA++ :电子设计自动化,适用于集成电路、PCB 设计等场景。

++② RTL代码++ :寄存器传输级,是数字电路设计中对硬件功能进行抽象描述的一种层次。其"主角"是寄存器和寄存器之间的数据通路,即在一个时钟周期内,信号会从寄存器输出,经过组合逻辑运算,最后进入下一级寄存器。类比:就像设计一个"生产线流程图"时,大家关心的是原材料(数据)在各个关键工位(寄存器)之间流转的顺序,而不是先去选择工位的具体设备品牌或规格。RTL核心作用: 描述电路功能、作为综合的输入(后续将抽象电路转变为真实电路的起点)、提高设计效率与灵活性(在RTL层面,可以先验证功能是否正确、时序是否大致满足需求,而不必一开始就面临海量器件和复杂连线,极大提高了设计的灵活性)。RTL主要内容: 寄存器定义(用于存储数据的基本单元)、组合逻辑运算(在寄存器之间插入"运算"逻辑)、控制信号与状态机。RTL的使用和测试 :编写代码(常用硬件描述语言Verilong、VHDL等来书写RTL代码)→ 仿真测试(使用仿真工具如VCS载入RTL代码和测试平台,跑出波形结果,验证是否达成预期功能,如数据处理是否正确、控制时序是否合理)→ 波形测试(仿真之后,会用波形查看器来可视化信号变化,快速定位并修复设计BUG)。++参考:RTL介绍++

++③ IP核库++ :是具有知识产权核的集成电路芯核的总称,是芯片设计环节中逐步分离出来的经过反复验证的、具有特定功能的、可以重复使用的、包含特定核心元素的(指令集、功能描述、代码等)集成电路设计宏模块(逻辑或功能单元),可以理解为部分可重复使用的''芯片设计模块''。++参考:IP核库介绍++

2. 物理设计数据

a. 来源

布局布线(Place & Route)工具、GDSLL文件、DRC/LVS报告。

b. 用途

确保物理设计符合工艺规则,避免断路/短路。

c. 分析方法

- 设计规则检查(++DRC++):验证几何规则

- 版图对比电路(LVS):确保版图与电路图匹配

- 寄生参数提取:分析互连线电容电阻(RC)

o. 注解

++① DRC++:用于验证芯片版图是否符合制造工艺的物理规则限制。

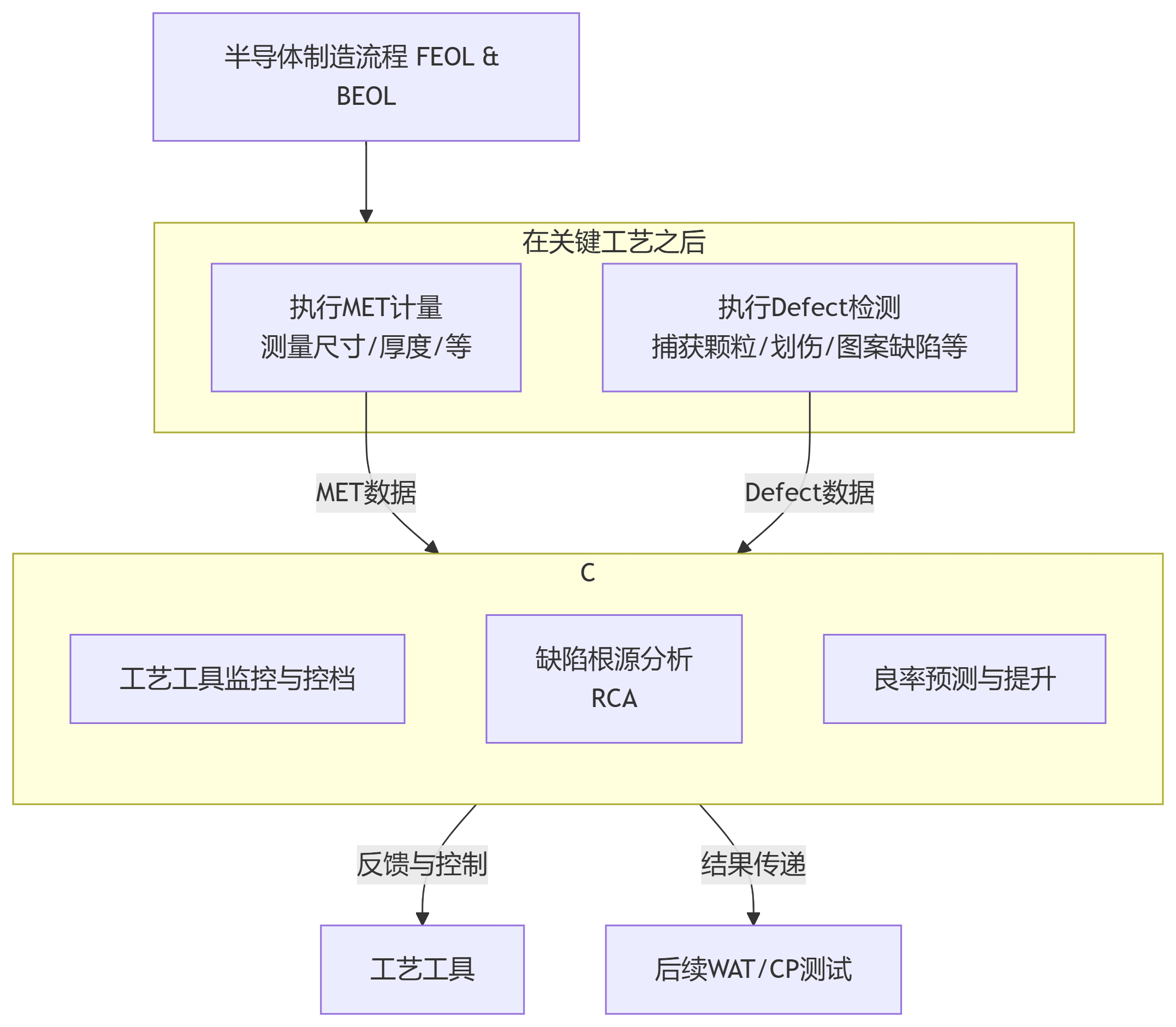

二、制造(Fab)阶段数据

1. 工艺参数数据/计量数据(++MET++数据)

a. 来源

设备传感器(温度、压力、气体流量)、晶圆计量(膜厚、CD尺寸)。

计量设备 (Metrology Tools):

-

CD-SEM (关键尺寸扫描电子显微镜) :用于测量晶体管等器件的关键尺寸(Critical Dimension, CD),例如栅极线条的宽度。这是光刻和刻蚀工艺最重要的监控参数。

-

OCD (光学临界尺寸量测):利用散射光信号反推出复杂的三维结构参数(如栅极的高度、侧壁角等),速度快,适用于在线监控。

-

膜厚测量设备:如椭圆偏振仪(Ellipsometer)用于测量氧化层、氮化硅等薄膜的厚度。

-

轮廓形貌测量仪 (AFM, Profilometer):用于测量表面粗糙度或台阶高度。

b. 用途

监控工艺稳定性,确保每道工序(如光刻、刻蚀)符合规格。

-

工艺控制:确保每一道工艺的输出结果都严格符合设计规格(Spec)。例如,确保栅极CD在±1nm的波动范围内,否则晶体管性能会不达标。

-

工艺窗口优化:帮助工艺工程师找到最佳工艺参数(如光刻的焦距、曝光量)。

-

设备匹配:确保线上多台相同功能的设备加工出的产品尺寸是一致的(Machine Matching)。

c. 分析方法

-

实时监控(FDC):通过AI预测工艺偏差

-

统计过程控制 (SPC):这是最核心的分析方法。对计量数据(如CD、膜厚)绘制控制图(Control Chart:X-bar,R图...),实时监控工艺是否处于稳定的统计受控状态。如果数据点超出控制限(Control Limit),系统会报警,工程师会介入调查。

-

趋势分析 (Trend Analysis):观察某个参数随时间的变化趋势,预测设备是否需要预防性维护(PM)。例如,CVD机台沉积的薄膜厚度有缓慢漂移的趋势,说明气体流量计可能需要校准。

-

多变量分析 (Multivariate Analysis):分析多个计量参数之间的相互关系。→识别关键因子因素

o. 注解

++① Met数据++:

- 核心问题:是否出现不该出现的?(颗粒、划伤、桥接、断路)

- 检测对象:随机、偶然的异常

- 数据特点:定性+定位(分类、数量、位置分布)

- 主要目的:发现和消除异常,减少随机缺陷密度

- 比喻:"质量检验员",负责挑出次品并报告问题源头。

2. 缺陷数据(++Defect++数据)

a. 来源

光学/电子束检测设备(++KLA++, AMAT)、缺陷扫描图。

-

光学图形化晶圆缺陷检测设备 : 如 KLA 的 Surfscan (用于无图案晶圆,检查硅片表面颗粒)和 eSeries / 39xx系列(用于有图案晶圆,检查光刻、刻蚀后的缺陷)。

-

电子束检测设备 (E-beam) : 如 Applied Materials 的 Vision 系列,分辨率更高,用于发现光学设备难以检测到的微小缺陷。

b. 用途

定位晶圆表面颗粒、刮痕、图案缺陷。

-

实时工艺监控:及时发现某道工艺后产生的异常缺陷激增,防止大批量不良品产生。

-

根源分析 (RCA):定位缺陷的来源,是哪个机台、哪个工艺步骤、哪个参数设置导致的问题。

-

良率关联 :与CP测试的失效点(Fail Die)进行关联分析,确定哪些类型的缺陷是导致芯片失效的"致命伤"(Killer Defects)。

-

设备监控:监控特定工艺设备的稳定性,比如检查CVD(化学气相沉积)设备是否因维护不当而产生过多颗粒。

c. 分析方法

-

缺陷分区 (Binning):自动化检测工具会用算法将检测到的缺陷按形态特征(大小、亮度、对比度)自动分类。

-

空间图案分析 (Spatial Pattern Analysis) :生成 "缺陷地图",观察缺陷在晶圆上的分布。

-

随机分布:通常意味着随机污染(如颗粒)。

-

集中簇状分布:很可能由光罩缺陷或工艺设备腔体内的特定问题引起。

-

边缘环状分布:通常与刻蚀、镀膜等工艺的边缘效应有关。

-

-

根源调查 (Root Cause Investigation):工程师将缺陷地图与特定工艺机台加工的晶圆序列号关联,快速锁定问题机台。

o. 注解

++① Defect数据++:

- 核心问题:该有的东西尺寸对不对?(厚度、宽度、高度、CD)

- 检测对象:工艺的系统性输出

- 数据特点:定量(精确的数值,单位是nm、Å)

- 主要目的:控制和优化工艺,减少参数波动

- 比喻:"尺子",负责确保每个零件的尺寸都精准无误。

++② KLA & Klarf++ :KLA是一家全球领先的半导体过程控制和检测设备供应商,专注于提高半导体制造的效率和质量。

Klarf是 KLA Result File 的缩写,最初是由KLA公司开发的,用于存储KLA半导体公司的测试仪器产生的测试数据。其设计的目的是方便数据的传输和解释,同时提供一种通用的格式,使不同的设备和工具能够互相交换数据。

后来由于其通用性和广泛应用于半导体测试产业,Klarf文件格式逐渐成为了一种行业标准。Klarf文件采用基于文本的格式存储数据,其结构包括头文件和多个数据块的组合。文件头部分包含了与整个文件相关的通用信息,例如数据格式版本、测试时间等。

++③ 与MET的联系++ :一道工艺步骤(如刻蚀)结束后,先用MET数据 确认刻蚀的线条宽度(CD)是否正确,再用Defect检测工具检查是否有残留物、桥接等缺陷。两者共同确保该工艺步骤的输出既"准确"又"干净",为最终的高良率打下坚实基础。

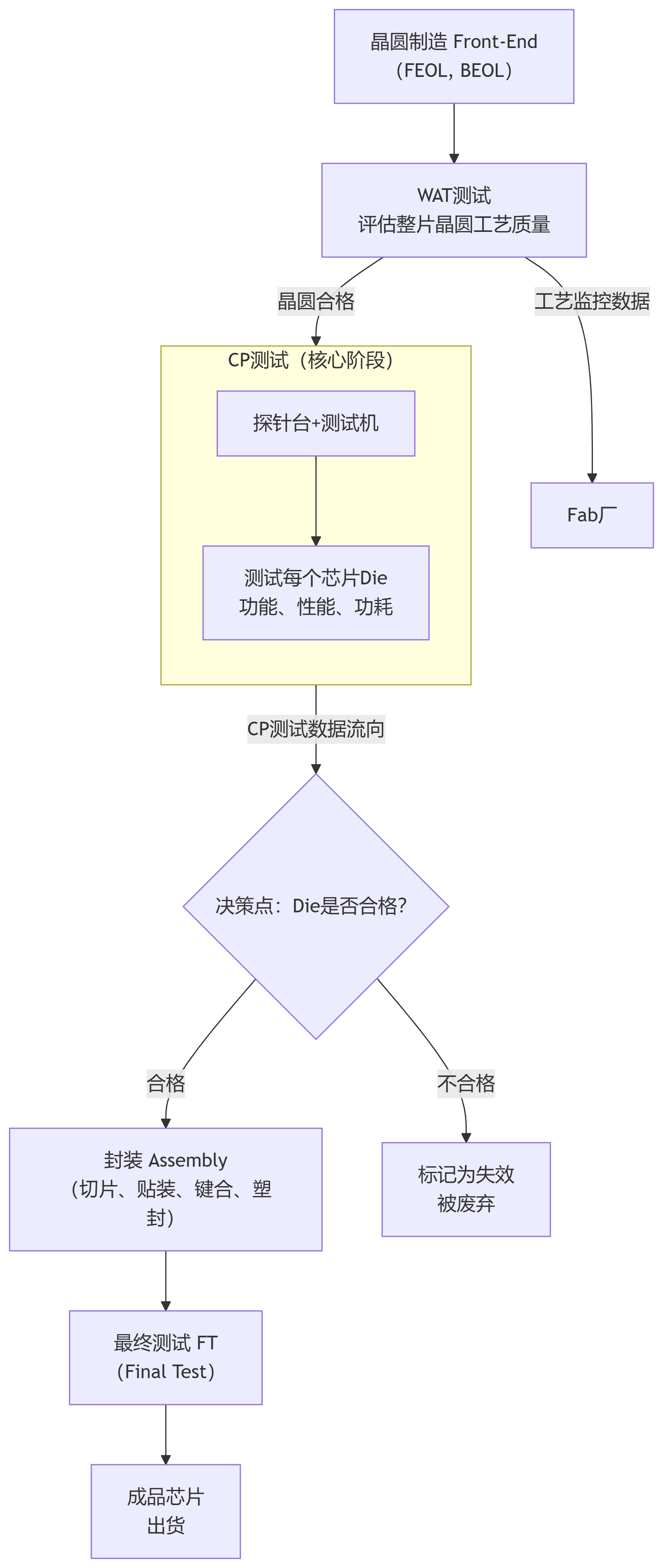

3. 良率数据(WAT、CP、FT)

a. 来源

晶圆允收测试(++WAT++ )、晶圆针测(++CP++ )、最终测试(++FT++)

b. 用途

量化制程质量,驱动成本优化

c. 分析方法

- 良率模型(Yield Modeling):如Poisson模型,负二项分布

- 相关性分析:关联缺陷数据与电性失效

- 良率学习曲线(Learning Curve):跟踪良率随时间提升趋势

o. 注释

++① WAT++:晶圆允收测试或晶圆电性测试(Wafer Accept Test)。

- 名称说明:

晶圆允收测试 强调的是测试的目的 :指晶圆在出厂前(发给封装厂或客户前)的"期末考试",目的是判断整片晶圆的制造工艺是否合格,能否被"接受"(Acceptance);

晶圆电性测试 强调的是这个测试的手段和内容:它是通过电性参数(如电压、电流、电阻、电容等)来评估工艺的; - 测试对象:工艺监控模块(PCM);

- 测试位置:位于晶圆的划片槽 (Scribe Line) 上,是专门设计的测试结构;

- 测试目的:评估制造工艺的水平(如晶体管性能、线宽、接触孔电阻、介质的厚度与击穿电压等);

- 测试内容:测量直流/参数(如 Idsat, Vth, Rs, Ileakage, C);

- 结果代表:整片晶圆的工艺质量;

- 数据用途:Fab端:监控和改善工艺;客户端:来料质量验证

- 比喻:就像是厨师在炒完一锅菜之后,先自己尝一口汤的咸淡 。他检查的是这整锅菜的"工艺水平"(盐、火候)是否达标,而不是检查每一块肉、每一片菜叶。

++② CP++:晶圆针测/电路probing(Chip Probing / Circuit Pr)

- 测试对象:每一个独立的芯片Die;

- 测试位置:位于晶圆的芯片核心电路上;

- 测试目的:筛选出功能正常且性能达标的芯片,淘汰坏的芯片;

- 测试内容:进行功能测试 (Function Test)、直流参数测试 (DC Test)、交流参数测试 (AC Test);

- 结果代表:单个芯片的好坏;

- 数据用途:Fab/封测端:计算晶圆良率,决定芯片是否封装;设计端:获取芯片性能分布;

- CP数据来源:自动化测试设备(ATE,控制测试流程、施加测试向量、采集响应)、探针台(Prober,精密移动晶圆,使探针卡上的针精确扎到芯片的焊盘Pad上)、探针卡(Probe Card,链接ATE和晶圆上芯片的关键接口);

- 数据类型与内容:功能测试数据(芯片的逻辑功能是否正确)、直流参数测试数据(DC Test,静态参数,如漏电流、输入/输出电平电压、短路/开路测试)、交流参数测试数据(AC-Test,动态性能参数,如运行速度、建立时间/保持时间、访问时间)、Bin Code数据(每个芯片都会被赋予一个分类代码Bin,代表它的测试结果,Bin = 1 为合格,Bin = 2为功能失效,Bin = 3为功耗超标等)、芯片坐标位置数据(记录每个芯片在晶圆上的具体位置);

- 核心数据分析方法:良率计算 (Yield Calculation,良率 = (合格芯片数 / 总测试芯片数) * 100%)、Wafer Map分析 (晶圆图分析,将Bin Code数据可视化到晶圆地图上,通过观察失效芯片的分布模式如随机分布、边缘分布、集群分布等,可以快速诊断问题根源)、统计过程控制 (SPC,监控关键电性参数(如Vth, Idsat)的分布和趋势,确保其处于稳定的统计控制范围内)、相关性分析 (Correlation Analysis,将CP测试数据与之前的WAT数据 、缺陷扫描图即Defect Map图进行关联分析,找出影响最终芯片良率的关键工艺步骤或参数。);

- CP测试的数据和结果:直接决定了哪些芯片值的封装(将好的Die(通常标记为Bin 1)和坏的Die(标记为Bin 2, 3, 4... 代表不同失效模式)区分开。避免花费高昂的封装成本去包装一个已知的坏芯片)、提供第一手良率数据(计算出最重要的晶圆良率(Wafer Yield),即一片晶圆上合格芯片的数量占比。这是Fab厂工艺水平的核心指标)、反馈设计与制造(CP测试数据(特别是失效芯片的空间分布图)可以帮助定位问题是来自设计缺陷(Design Bug)还是特定区域的制造缺陷(Process Defect));

- 比喻:就像是把这一锅菜里的每一块肉和菜叶都挑出来尝一遍 ,把炒焦的、没味的坏掉的个体挑出去扔掉,只把好的装盘(送去封装)。

++③ FT++:

++④ WAT和CP的联系++ :在制造完成后,会对晶圆进行 WAT ,使用测试结构 测量电性参数 ,以评估工艺 。通过WAT后,才会进行 CP ,使用探针卡 接触芯片的焊盘 ,对每个芯片 进行功能和高速度测试。

三、测试与封装数据

2. 电性测试数据

a. 来源

自动测试设备(ATE)、探针卡、测试程序日志

b. 用途

筛选功能失效芯片,提供设计反馈

c. 分析方法

- Shmoo图:可视化电压/频率下的芯片工作边界

- Bin分析:分类失效模式(如逻辑故障、内存故障)

- 统计分箱(Statistical Binning):优化测试流程效率

3. 可靠性与老化数据

a. 来源

加速寿命测试(HTOL, ELFR)、封装应力测试

b. 用途

预测芯片寿命(如FIT率),确保产品耐用性

c. 分析方法

- 威尔分布分析:建模失效时间分布

- Arrhenius模型:推算温度对寿命的影响

- 失效物理(PoF):分析材料退化机制

四、供应链与运营数据

1. 设备健康数据

a. 来源

设备日志、预测性维护传感器、备件更换记录

b. 用途

减少宕机时间,优化维护计划

c. 分析方法:

-

故障预测(PdM):用机器学习(如LSTM)预警设备失效

-

OEE计算:综合可用率、性能率、良率评估设备效率

2. 物料与物流数据

a. 来源

MES系统、ERP系统、晶圆追溯码

b. 用途

追踪晶圆流向,管理物料库存

c. 分析方法

-

关键路径分析(CPA):优化晶圆在Fab中的移动路径

-

库存周转率:降低WIP(在制品)积压

五、市场与产品数据

1. 终端产品性能数据

a.来源

客户反馈、现场失效报告、IOT传感器

b. 用途

改进下一代设计,提升客户满意度

c. 分析方法

-

失效模式与效应分析(FMEA):优先级排序改进方向

-

根因分析(Fishbone图):定位系统级失效源头

2. 竞争情报数据

a. 来源

拆解报告(Teardown)、专利数据库、市场研报

b. 用途

制定技术路线图,保持竞争优势

c. 分析方法

-

技术对标(Benchmarking):对比对手芯片性能/成本

-

专利地图(Patent Mapping):识别技术空白与机会

六、关键分析工具与技术