20250822给荣品RD-RK3588开发板刷Rockchip原厂的Android14时点亮荣品的8寸屏

2025/8/22 19:52

缘起:当你把开发板重新适配一把,就相当于从头做了一个项目。

当然,开发板的功能都是好的,你免除了调试的过程,也就没有解决硬件出错的经验了!

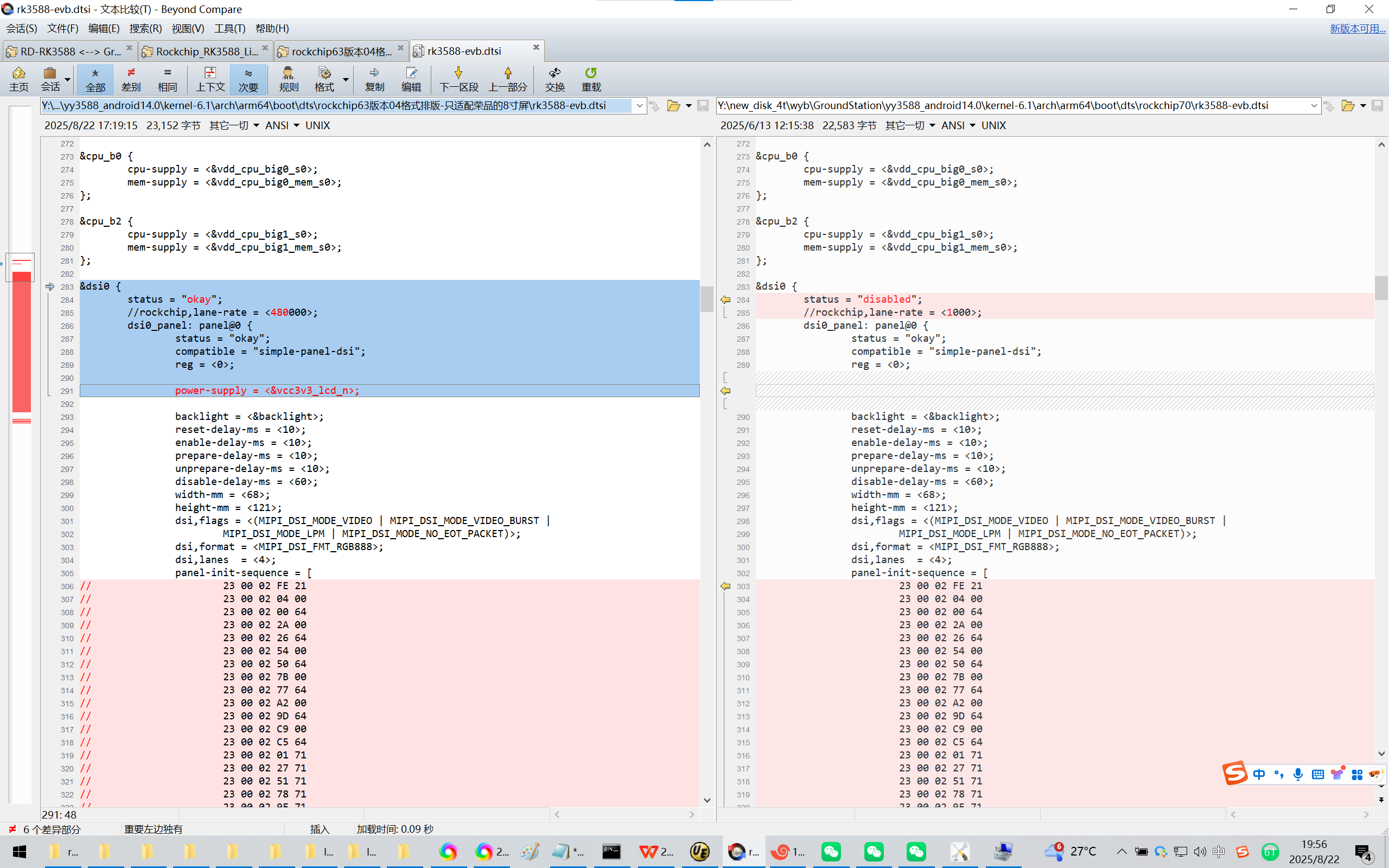

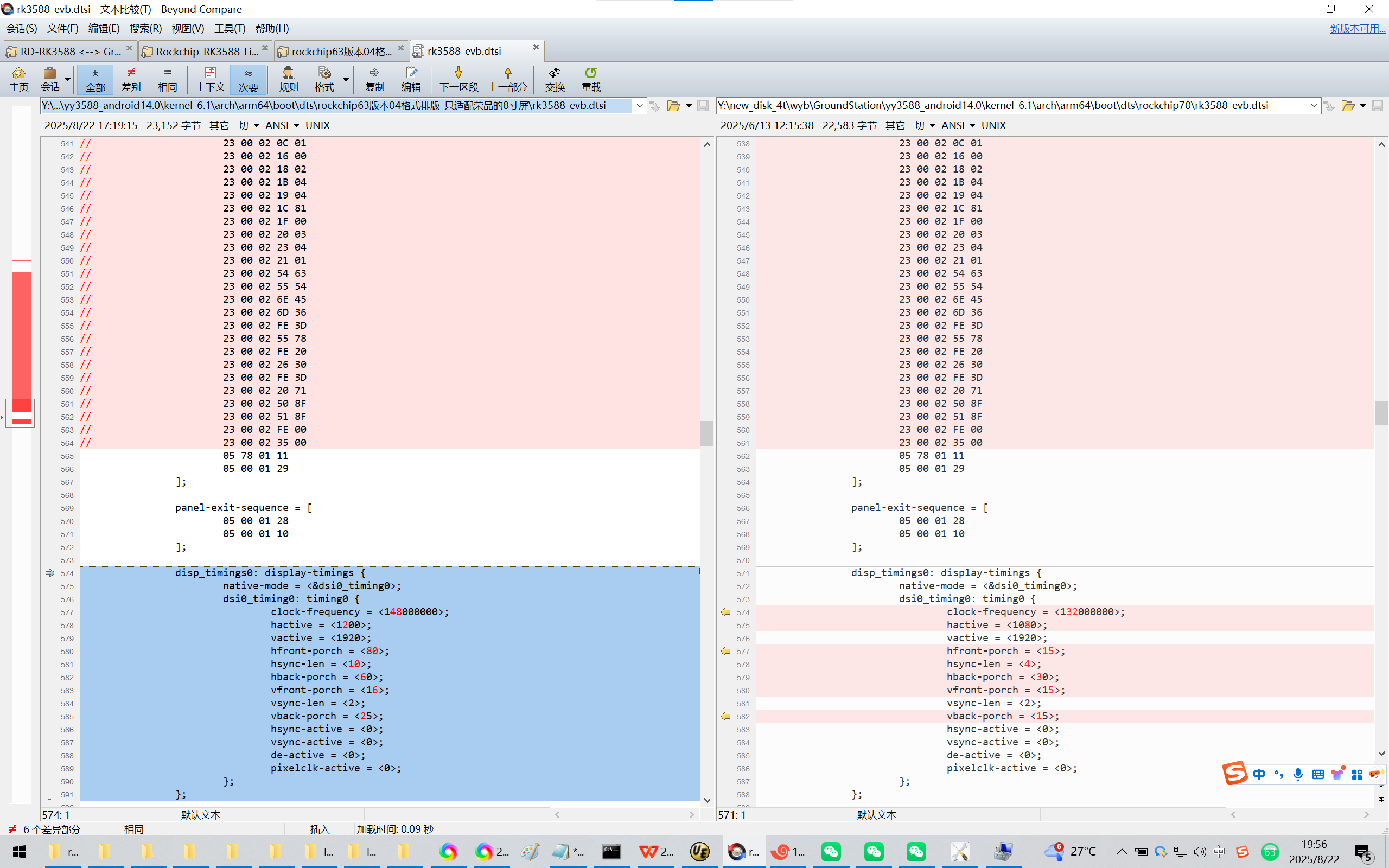

荣品8寸屏的初始化代码+LCD屏参数!

Y:\new_disk_4t\wyb\GroundStation\yy3588_android14.0\kernel-6.1\arch\arm64\boot\dts\rockchip\rk3588-evb.dtsi

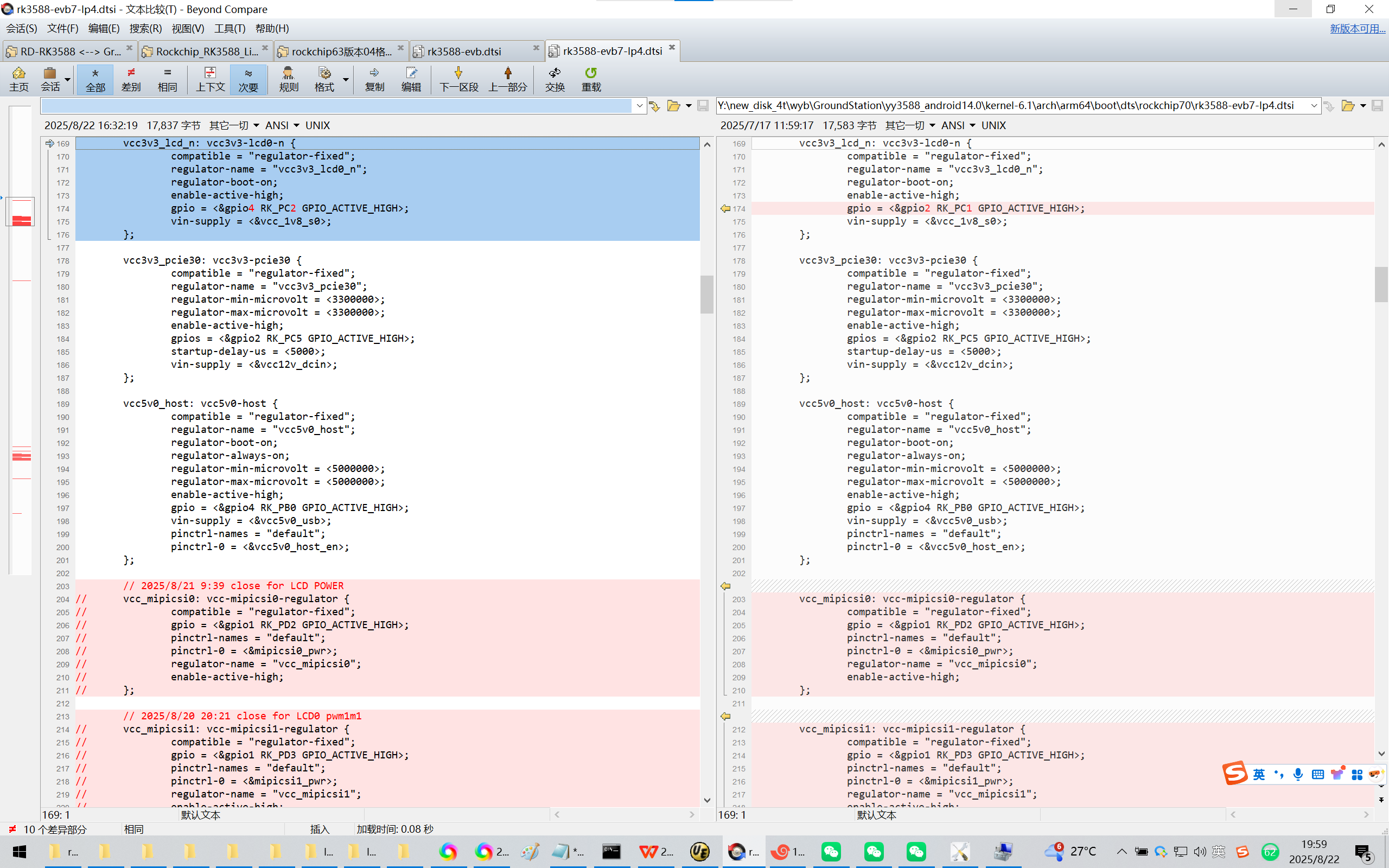

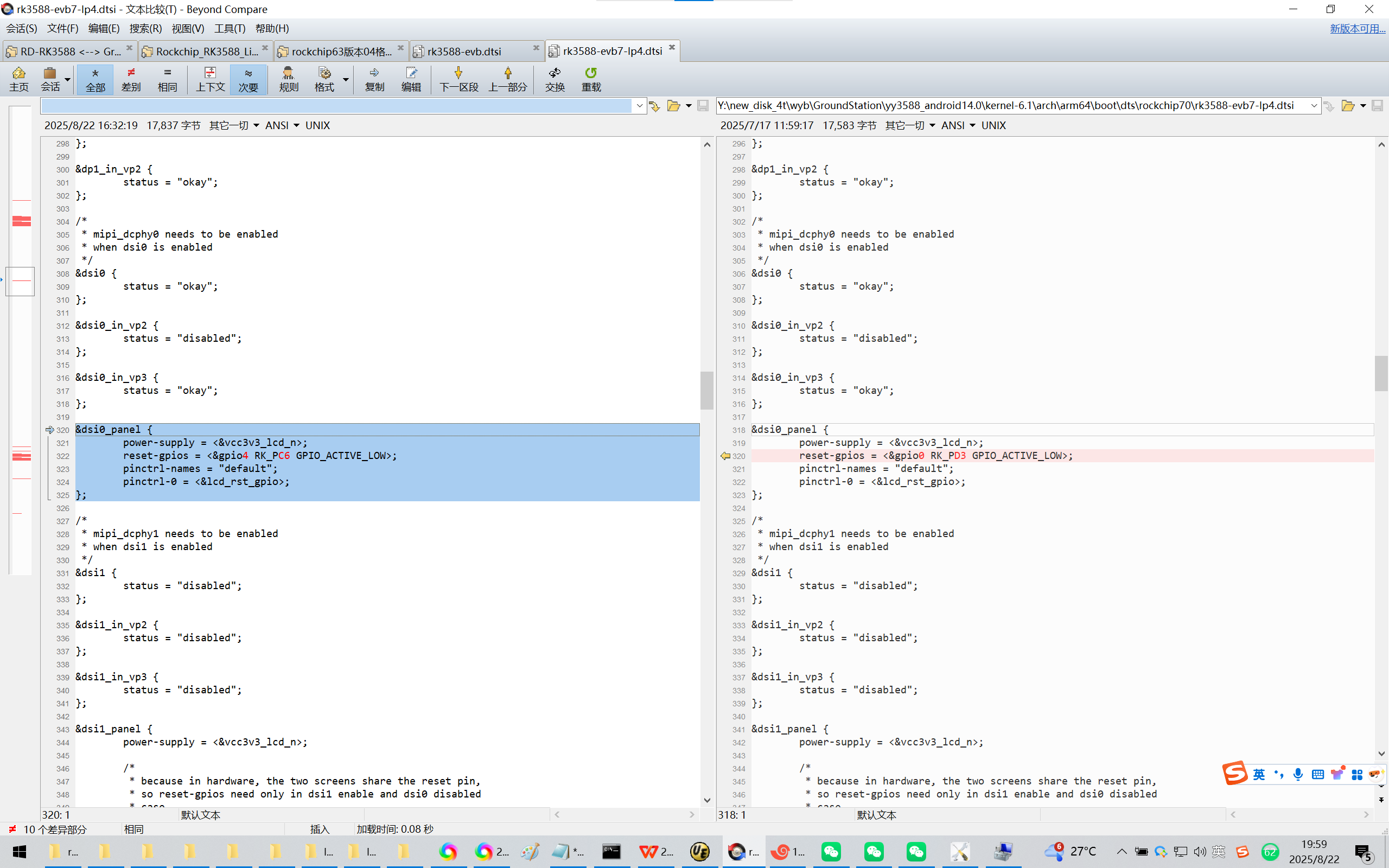

荣品8寸屏的相关GPIO/电源的配置:

Y:\new_disk_4t\wyb\GroundStation\yy3588_android14.0\kernel-6.1\arch\arm64\boot\dts\rockchip\rk3588-evb7-lp4.dtsi

荣品8寸屏的初始化代码+LCD屏参数!

Y:\new_disk_4t\wyb\GroundStation\yy3588_android14.0\kernel-6.1\arch\arm64\boot\dts\rockchip63版本04格式排版-只适配荣品的8寸屏\rk3588-evb.dtsi

&dsi0 {

status = "okay";

//rockchip,lane-rate = <480000>;

dsi0_panel: panel@0 {

status = "okay";

compatible = "simple-panel-dsi";

reg = <0>;

power-supply = <&vcc3v3_lcd_n>;

backlight = <&backlight>;

reset-delay-ms = <10>;

enable-delay-ms = <10>;

prepare-delay-ms = <10>;

unprepare-delay-ms = <10>;

disable-delay-ms = <60>;

width-mm = <68>;

height-mm = <121>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_NO_EOT_PACKET)>;

dsi,format = <MIPI_DSI_FMT_RGB888>;

dsi,lanes = <4>;

panel-init-sequence = [

// 23 00 02 FE 21

// 23 00 02 04 00

// 23 00 02 00 64

// 23 00 02 2A 00

// 23 00 02 26 64

// 23 00 02 54 00

// 23 00 02 50 64

// 23 00 02 7B 00

// 23 00 02 77 64

// 23 00 02 A2 00

// 23 00 02 9D 64

// 23 00 02 C9 00

// 23 00 02 C5 64

// 23 00 02 01 71

// 23 00 02 27 71

// 23 00 02 51 71

// 23 00 02 78 71

// 23 00 02 9E 71

// 23 00 02 C6 71

// 23 00 02 02 89

// 23 00 02 28 89

// 23 00 02 52 89

// 23 00 02 79 89

// 23 00 02 9F 89

// 23 00 02 C7 89

// 23 00 02 03 9E

// 23 00 02 29 9E

// 23 00 02 53 9E

// 23 00 02 7A 9E

// 23 00 02 A0 9E

// 23 00 02 C8 9E

// 23 00 02 09 00

// 23 00 02 05 B0

// 23 00 02 31 00

// 23 00 02 2B B0

// 23 00 02 5A 00

// 23 00 02 55 B0

// 23 00 02 80 00

// 23 00 02 7C B0

// 23 00 02 A7 00

// 23 00 02 A3 B0

// 23 00 02 CE 00

// 23 00 02 CA B0

// 23 00 02 06 C0

// 23 00 02 2D C0

// 23 00 02 56 C0

// 23 00 02 7D C0

// 23 00 02 A4 C0

// 23 00 02 CB C0

// 23 00 02 07 CF

// 23 00 02 2F CF

// 23 00 02 58 CF

// 23 00 02 7E CF

// 23 00 02 A5 CF

// 23 00 02 CC CF

// 23 00 02 08 DD

// 23 00 02 30 DD

// 23 00 02 59 DD

// 23 00 02 7F DD

// 23 00 02 A6 DD

// 23 00 02 CD DD

// 23 00 02 0E 15

// 23 00 02 0A E9

// 23 00 02 36 15

// 23 00 02 32 E9

// 23 00 02 5F 15

// 23 00 02 5B E9

// 23 00 02 85 15

// 23 00 02 81 E9

// 23 00 02 AD 15

// 23 00 02 A9 E9

// 23 00 02 D3 15

// 23 00 02 CF E9

// 23 00 02 0B 14

// 23 00 02 33 14

// 23 00 02 5C 14

// 23 00 02 82 14

// 23 00 02 AA 14

// 23 00 02 D0 14

// 23 00 02 0C 36

// 23 00 02 34 36

// 23 00 02 5D 36

// 23 00 02 83 36

// 23 00 02 AB 36

// 23 00 02 D1 36

// 23 00 02 0D 6B

// 23 00 02 35 6B

// 23 00 02 5E 6B

// 23 00 02 84 6B

// 23 00 02 AC 6B

// 23 00 02 D2 6B

// 23 00 02 13 5A

// 23 00 02 0F 94

// 23 00 02 3B 5A

// 23 00 02 37 94

// 23 00 02 64 5A

// 23 00 02 60 94

// 23 00 02 8A 5A

// 23 00 02 86 94

// 23 00 02 B2 5A

// 23 00 02 AE 94

// 23 00 02 D8 5A

// 23 00 02 D4 94

// 23 00 02 10 D1

// 23 00 02 38 D1

// 23 00 02 61 D1

// 23 00 02 87 D1

// 23 00 02 AF D1

// 23 00 02 D5 D1

// 23 00 02 11 04

// 23 00 02 39 04

// 23 00 02 62 04

// 23 00 02 88 04

// 23 00 02 B0 04

// 23 00 02 D6 04

// 23 00 02 12 05

// 23 00 02 3A 05

// 23 00 02 63 05

// 23 00 02 89 05

// 23 00 02 B1 05

// 23 00 02 D7 05

// 23 00 02 18 AA

// 23 00 02 14 36

// 23 00 02 42 AA

// 23 00 02 3D 36

// 23 00 02 69 AA

// 23 00 02 65 36

// 23 00 02 8F AA

// 23 00 02 8B 36

// 23 00 02 B7 AA

// 23 00 02 B3 36

// 23 00 02 DD AA

// 23 00 02 D9 36

// 23 00 02 15 74

// 23 00 02 3F 74

// 23 00 02 66 74

// 23 00 02 8C 74

// 23 00 02 B4 74

// 23 00 02 DA 74

// 23 00 02 16 9F

// 23 00 02 40 9F

// 23 00 02 67 9F

// 23 00 02 8D 9F

// 23 00 02 B5 9F

// 23 00 02 DB 9F

// 23 00 02 17 DC

// 23 00 02 41 DC

// 23 00 02 68 DC

// 23 00 02 8E DC

// 23 00 02 B6 DC

// 23 00 02 DC DC

// 23 00 02 1D FF

// 23 00 02 19 03

// 23 00 02 47 FF

// 23 00 02 43 03

// 23 00 02 6E FF

// 23 00 02 6A 03

// 23 00 02 94 FF

// 23 00 02 90 03

// 23 00 02 BC FF

// 23 00 02 B8 03

// 23 00 02 E2 FF

// 23 00 02 DE 03

// 23 00 02 1A 35

// 23 00 02 44 35

// 23 00 02 6B 35

// 23 00 02 91 35

// 23 00 02 B9 35

// 23 00 02 DF 35

// 23 00 02 1B 45

// 23 00 02 45 45

// 23 00 02 6C 45

// 23 00 02 92 45

// 23 00 02 BA 45

// 23 00 02 E0 45

// 23 00 02 1C 55

// 23 00 02 46 55

// 23 00 02 6D 55

// 23 00 02 93 55

// 23 00 02 BB 55

// 23 00 02 E1 55

// 23 00 02 22 FF

// 23 00 02 1E 68

// 23 00 02 4C FF

// 23 00 02 48 68

// 23 00 02 73 FF

// 23 00 02 6F 68

// 23 00 02 99 FF

// 23 00 02 95 68

// 23 00 02 C1 FF

// 23 00 02 BD 68

// 23 00 02 E7 FF

// 23 00 02 E3 68

// 23 00 02 1F 7E

// 23 00 02 49 7E

// 23 00 02 70 7E

// 23 00 02 96 7E

// 23 00 02 BE 7E

// 23 00 02 E4 7E

// 23 00 02 20 97

// 23 00 02 4A 97

// 23 00 02 71 97

// 23 00 02 97 97

// 23 00 02 BF 97

// 23 00 02 E5 97

// 23 00 02 21 B5

// 23 00 02 4B B5

// 23 00 02 72 B5

// 23 00 02 98 B5

// 23 00 02 C0 B5

// 23 00 02 E6 B5

// 23 00 02 25 F0

// 23 00 02 23 E8

// 23 00 02 4F F0

// 23 00 02 4D E8

// 23 00 02 76 F0

// 23 00 02 74 E8

// 23 00 02 9C F0

// 23 00 02 9A E8

// 23 00 02 C4 F0

// 23 00 02 C2 E8

// 23 00 02 EA F0

// 23 00 02 E8 E8

// 23 00 02 24 FF

// 23 00 02 4E FF

// 23 00 02 75 FF

// 23 00 02 9B FF

// 23 00 02 C3 FF

// 23 00 02 E9 FF

// 23 00 02 FE 3D

// 23 00 02 00 04

// 23 00 02 FE 23

// 23 00 02 08 82

// 23 00 02 0A 00

// 23 00 02 0B 00

// 23 00 02 0C 01

// 23 00 02 16 00

// 23 00 02 18 02

// 23 00 02 1B 04

// 23 00 02 19 04

// 23 00 02 1C 81

// 23 00 02 1F 00

// 23 00 02 20 03

// 23 00 02 23 04

// 23 00 02 21 01

// 23 00 02 54 63

// 23 00 02 55 54

// 23 00 02 6E 45

// 23 00 02 6D 36

// 23 00 02 FE 3D

// 23 00 02 55 78

// 23 00 02 FE 20

// 23 00 02 26 30

// 23 00 02 FE 3D

// 23 00 02 20 71

// 23 00 02 50 8F

// 23 00 02 51 8F

// 23 00 02 FE 00

// 23 00 02 35 00

05 78 01 11

05 00 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

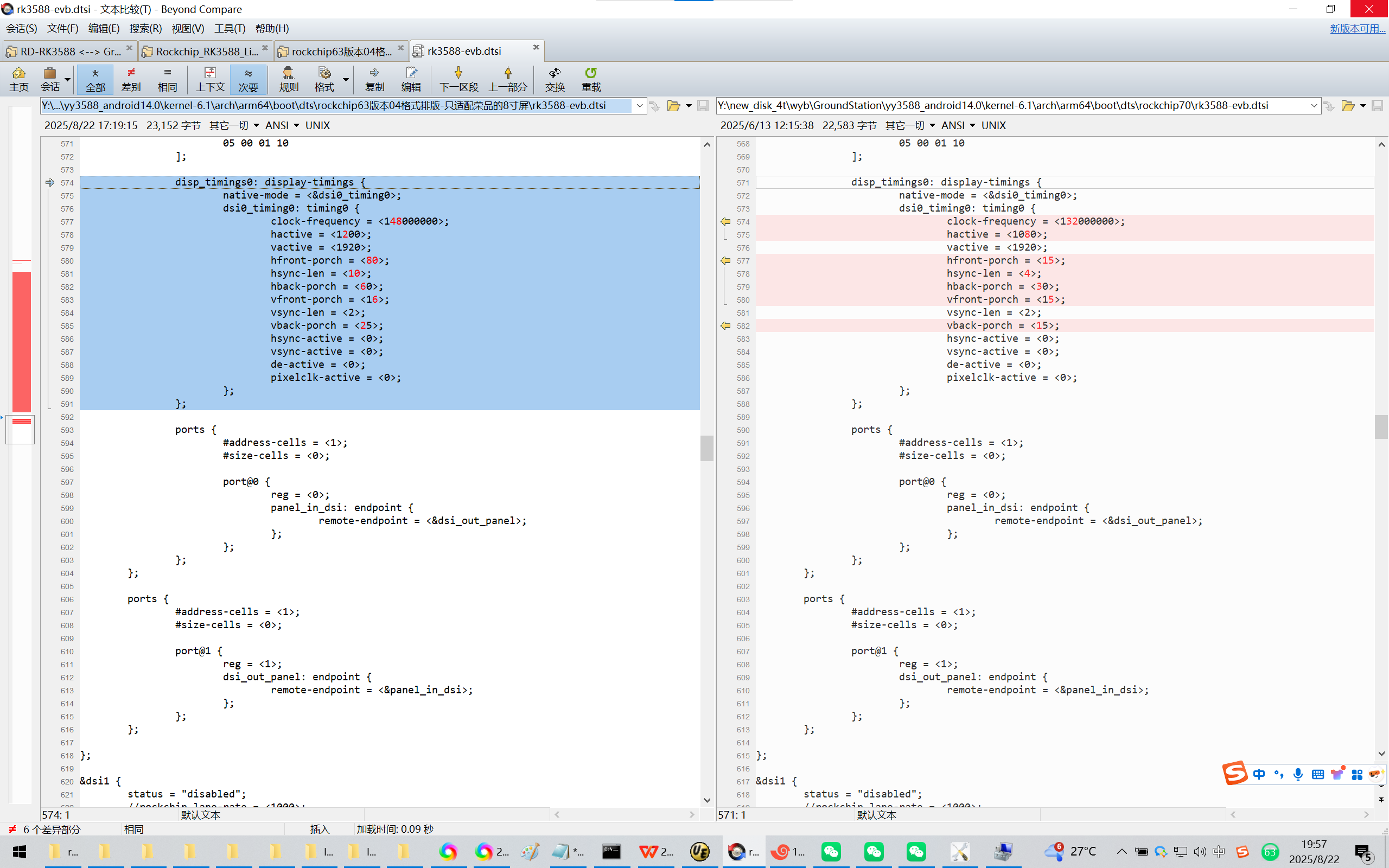

disp_timings0: display-timings {

native-mode = <&dsi0_timing0>;

dsi0_timing0: timing0 {

clock-frequency = <148000000>;

hactive = <1200>;

vactive = <1920>;

hfront-porch = <80>;

hsync-len = <10>;

hback-porch = <60>;

vfront-porch = <16>;

vsync-len = <2>;

vback-porch = <25>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi: endpoint {

remote-endpoint = <&dsi_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi>;

};

};

};

};

荣品8寸屏的相关GPIO/电源的配置:

Y:\new_disk_4t\wyb\GroundStation\yy3588_android14.0\kernel-6.1\arch\arm64\boot\dts\rockchip63版本04格式排版-只适配荣品的8寸屏\rk3588-evb7-lp4.dtsi

vcc3v3_lcd_n: vcc3v3-lcd0-n {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_lcd0_n";

regulator-boot-on;

enable-active-high;

gpio = <&gpio2 RK_PC1 GPIO_ACTIVE_HIGH>;

vin-supply = <&vcc_1v8_s0>;

};

修改为:

vcc3v3_lcd_n: vcc3v3-lcd0-n {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_lcd0_n";

regulator-boot-on;

enable-active-high;

gpio = <&gpio4 RK_PC2 GPIO_ACTIVE_HIGH>;

vin-supply = <&vcc_1v8_s0>;

};

&pinctrl {

lcd {

lcd_rst_gpio: lcd-rst-gpio {

rockchip,pins = <0 RK_PD3 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

};

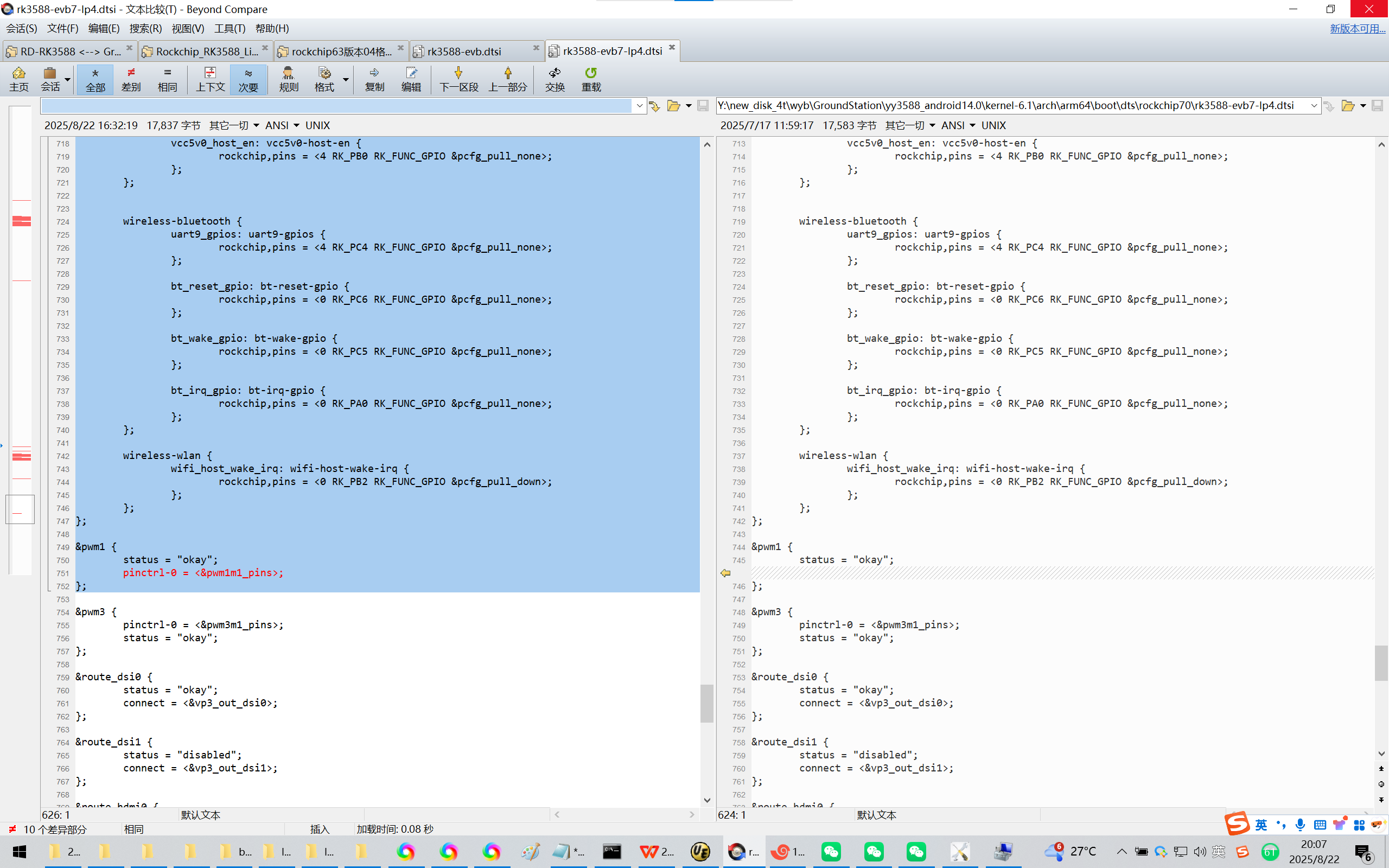

&pwm1 {

status = "okay";

};

修改为:

&pcie30phy {

rockchip,pcie30-phymode = <PHY_MODE_PCIE_AGGREGATION>;

status = "disabled";

};

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB3 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

pinctrl-names = "default";

pinctrl-0 = <&pcie30x4_clkreqn_m1>;

status = "disabled";

};

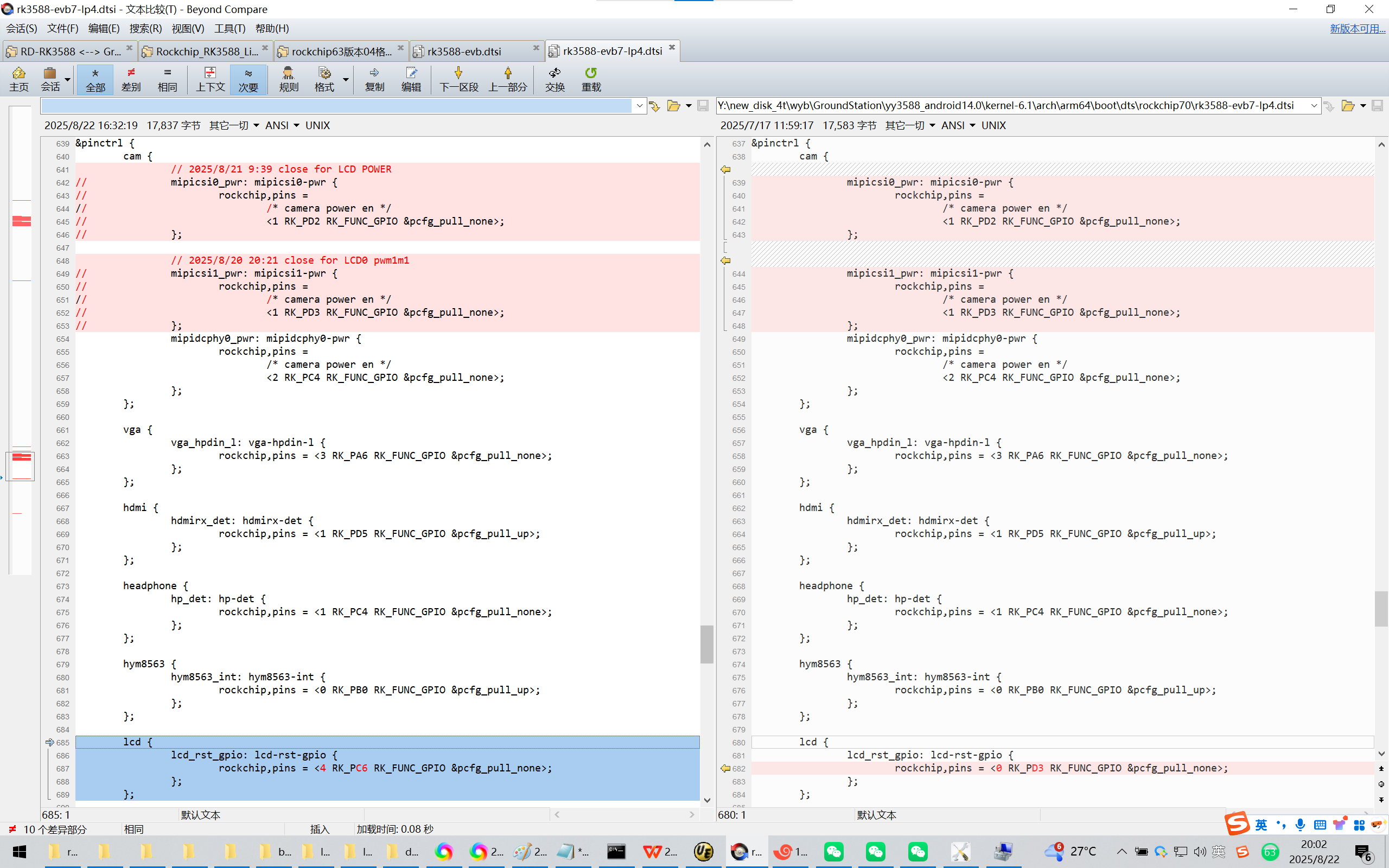

&pinctrl {

cam {

// 2025/8/21 9:39 close for LCD POWER

// mipicsi0_pwr: mipicsi0-pwr {

// rockchip,pins =

// /* camera power en */

// <1 RK_PD2 RK_FUNC_GPIO &pcfg_pull_none>;

// };

// 2025/8/20 20:21 close for LCD0 pwm1m1

// mipicsi1_pwr: mipicsi1-pwr {

// rockchip,pins =

// /* camera power en */

// <1 RK_PD3 RK_FUNC_GPIO &pcfg_pull_none>;

// };

mipidcphy0_pwr: mipidcphy0-pwr {

rockchip,pins =

/* camera power en */

<2 RK_PC4 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

lcd {

lcd_rst_gpio: lcd-rst-gpio {

rockchip,pins = <4 RK_PC6 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

};

&pwm1 {

status = "okay";

pinctrl-0 = <&pwm1m1_pins>;

};

Y:\new_disk_4t\wyb\GroundStation\yy3588_android14.0\kernel-6.1\arch\arm64\boot\dts\rockchip63版本04格式排版-只适配荣品的8寸屏\rk3588-evb.dtsi

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/*

* Copyright (c) 2021 Rockchip Electronics Co., Ltd.

*

*/

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/pwm/pwm.h>

#include <dt-bindings/pinctrl/rockchip.h>

#include <dt-bindings/input/rk-input.h>

#include <dt-bindings/display/drm_mipi_dsi.h>

#include <dt-bindings/display/rockchip_vop.h>

#include <dt-bindings/sensor-dev.h>

/ {

adc_keys: adc-keys {

compatible = "adc-keys";

io-channels = <&saradc 1>;

io-channel-names = "buttons";

keyup-threshold-microvolt = <1800000>;

poll-interval = <100>;

vol-up-key {

label = "volume up";

linux,code = <KEY_VOLUMEUP>;

press-threshold-microvolt = <17000>;

};

vol-down-key {

label = "volume down";

linux,code = <KEY_VOLUMEDOWN>;

press-threshold-microvolt = <417000>;

};

menu-key {

label = "menu";

linux,code = <KEY_MENU>;

press-threshold-microvolt = <890000>;

};

back-key {

label = "back";

linux,code = <KEY_BACK>;

press-threshold-microvolt = <1235000>;

};

};

backlight: backlight {

compatible = "pwm-backlight";

brightness-levels = <

0 20 20 21 21 22 22 23

23 24 24 25 25 26 26 27

27 28 28 29 29 30 30 31

31 32 32 33 33 34 34 35

35 36 36 37 37 38 38 39

40 41 42 43 44 45 46 47

48 49 50 51 52 53 54 55

56 57 58 59 60 61 62 63

64 65 66 67 68 69 70 71

72 73 74 75 76 77 78 79

80 81 82 83 84 85 86 87

88 89 90 91 92 93 94 95

96 97 98 99 100 101 102 103

104 105 106 107 108 109 110 111

112 113 114 115 116 117 118 119

120 121 122 123 124 125 126 127

128 129 130 131 132 133 134 135

136 137 138 139 140 141 142 143

144 145 146 147 148 149 150 151

152 153 154 155 156 157 158 159

160 161 162 163 164 165 166 167

168 169 170 171 172 173 174 175

176 177 178 179 180 181 182 183

184 185 186 187 188 189 190 191

192 193 194 195 196 197 198 199

200 201 202 203 204 205 206 207

208 209 210 211 212 213 214 215

216 217 218 219 220 221 222 223

224 225 226 227 228 229 230 231

232 233 234 235 236 237 238 239

240 241 242 243 244 245 246 247

248 249 250 251 252 253 254 255

>;

default-brightness-level = <200>;

};

bt_sco: bt-sco {

status = "disabled";

compatible = "delta,dfbmcs320";

#sound-dai-cells = <1>;

};

bt_sound: bt-sound {

status = "disabled";

compatible = "simple-audio-card";

simple-audio-card,format = "dsp_a";

simple-audio-card,bitclock-inversion;

simple-audio-card,mclk-fs = <256>;

simple-audio-card,name = "rockchip,bt";

simple-audio-card,cpu {

sound-dai = <&i2s2_2ch>;

};

simple-audio-card,codec {

sound-dai = <&bt_sco 1>;

};

};

edp0_sound: edp0-sound {

status = "disabled";

compatible = "rockchip,hdmi";

rockchip,mclk-fs = <128>;

rockchip,card-name = "rockchip-edp0";

rockchip,cpu = <&i2s5_8ch>;

rockchip,codec = <&edp0 0>;

};

edp1_sound: edp1-sound {

status = "disabled";

compatible = "rockchip,hdmi";

rockchip,mclk-fs = <128>;

rockchip,card-name = "rockchip-edp1";

rockchip,cpu = <&i2s6_8ch>;

rockchip,codec = <&edp1 0>;

};

hdmi0_sound: hdmi0-sound {

status = "disabled";

compatible = "rockchip,hdmi";

rockchip,mclk-fs = <128>;

rockchip,card-name = "rockchip-hdmi0";

rockchip,cpu = <&i2s5_8ch>;

rockchip,codec = <&hdmi0>;

rockchip,jack-det;

};

hdmi1_sound: hdmi1-sound {

status = "disabled";

compatible = "rockchip,hdmi";

rockchip,mclk-fs = <128>;

rockchip,card-name = "rockchip-hdmi1";

rockchip,cpu = <&i2s6_8ch>;

rockchip,codec = <&hdmi1>;

rockchip,jack-det;

};

dp0_sound: dp0-sound {

status = "disabled";

compatible = "rockchip,hdmi";

rockchip,card-name= "rockchip-dp0";

rockchip,mclk-fs = <512>;

rockchip,cpu = <&spdif_tx2>;

rockchip,codec = <&dp0 1>;

rockchip,jack-det;

};

dp1_sound: dp1-sound {

status = "disabled";

compatible = "rockchip,hdmi";

rockchip,card-name= "rockchip-dp1";

rockchip,mclk-fs = <512>;

rockchip,cpu = <&spdif_tx5>;

rockchip,codec = <&dp1 1>;

rockchip,jack-det;

};

leds: leds {

compatible = "gpio-leds";

work_led: work {

gpios = <&gpio3 RK_PB7 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "heartbeat";

};

};

spdif_tx0_dc: spdif-tx0-dc {

status = "disabled";

compatible = "linux,spdif-dit";

#sound-dai-cells = <0>;

};

spdif_tx0_sound: spdif-tx0-sound {

status = "disabled";

compatible = "simple-audio-card";

simple-audio-card,mclk-fs = <128>;

simple-audio-card,name = "rockchip,spdif-tx0";

simple-audio-card,cpu {

sound-dai = <&spdif_tx0>;

};

simple-audio-card,codec {

sound-dai = <&spdif_tx0_dc>;

};

};

spdif_tx1_dc: spdif-tx1-dc {

status = "disabled";

compatible = "linux,spdif-dit";

#sound-dai-cells = <0>;

};

spdif_tx1_sound: spdif-tx1-sound {

status = "disabled";

compatible = "simple-audio-card";

simple-audio-card,mclk-fs = <128>;

simple-audio-card,name = "rockchip,spdif-tx1";

simple-audio-card,cpu {

sound-dai = <&spdif_tx1>;

};

simple-audio-card,codec {

sound-dai = <&spdif_tx1_dc>;

};

};

test-power {

status = "okay";

};

vcc12v_dcin: vcc12v-dcin {

compatible = "regulator-fixed";

regulator-name = "vcc12v_dcin";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <12000000>;

regulator-max-microvolt = <12000000>;

};

vcc5v0_sys: vcc5v0-sys {

compatible = "regulator-fixed";

regulator-name = "vcc5v0_sys";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

vin-supply = <&vcc12v_dcin>;

};

vcc5v0_usbdcin: vcc5v0-usbdcin {

compatible = "regulator-fixed";

regulator-name = "vcc5v0_usbdcin";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

vin-supply = <&vcc12v_dcin>;

};

vcc5v0_usb: vcc5v0-usb {

compatible = "regulator-fixed";

regulator-name = "vcc5v0_usb";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

vin-supply = <&vcc5v0_usbdcin>;

};

};

&av1d {

status = "okay";

};

&av1d_mmu {

status = "okay";

};

&avsd {

status = "okay";

};

&cpu_l0 {

cpu-supply = <&vdd_cpu_lit_s0>;

mem-supply = <&vdd_cpu_lit_mem_s0>;

};

&cpu_b0 {

cpu-supply = <&vdd_cpu_big0_s0>;

mem-supply = <&vdd_cpu_big0_mem_s0>;

};

&cpu_b2 {

cpu-supply = <&vdd_cpu_big1_s0>;

mem-supply = <&vdd_cpu_big1_mem_s0>;

};

&dsi0 {

status = "okay";

//rockchip,lane-rate = <480000>;

dsi0_panel: panel@0 {

status = "okay";

compatible = "simple-panel-dsi";

reg = <0>;

power-supply = <&vcc3v3_lcd_n>;

backlight = <&backlight>;

reset-delay-ms = <10>;

enable-delay-ms = <10>;

prepare-delay-ms = <10>;

unprepare-delay-ms = <10>;

disable-delay-ms = <60>;

width-mm = <68>;

height-mm = <121>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_NO_EOT_PACKET)>;

dsi,format = <MIPI_DSI_FMT_RGB888>;

dsi,lanes = <4>;

panel-init-sequence = [

// 23 00 02 FE 21

// 23 00 02 04 00

// 23 00 02 00 64

// 23 00 02 2A 00

// 23 00 02 26 64

// 23 00 02 54 00

// 23 00 02 50 64

// 23 00 02 7B 00

// 23 00 02 77 64

// 23 00 02 A2 00

// 23 00 02 9D 64

// 23 00 02 C9 00

// 23 00 02 C5 64

// 23 00 02 01 71

// 23 00 02 27 71

// 23 00 02 51 71

// 23 00 02 78 71

// 23 00 02 9E 71

// 23 00 02 C6 71

// 23 00 02 02 89

// 23 00 02 28 89

// 23 00 02 52 89

// 23 00 02 79 89

// 23 00 02 9F 89

// 23 00 02 C7 89

// 23 00 02 03 9E

// 23 00 02 29 9E

// 23 00 02 53 9E

// 23 00 02 7A 9E

// 23 00 02 A0 9E

// 23 00 02 C8 9E

// 23 00 02 09 00

// 23 00 02 05 B0

// 23 00 02 31 00

// 23 00 02 2B B0

// 23 00 02 5A 00

// 23 00 02 55 B0

// 23 00 02 80 00

// 23 00 02 7C B0

// 23 00 02 A7 00

// 23 00 02 A3 B0

// 23 00 02 CE 00

// 23 00 02 CA B0

// 23 00 02 06 C0

// 23 00 02 2D C0

// 23 00 02 56 C0

// 23 00 02 7D C0

// 23 00 02 A4 C0

// 23 00 02 CB C0

// 23 00 02 07 CF

// 23 00 02 2F CF

// 23 00 02 58 CF

// 23 00 02 7E CF

// 23 00 02 A5 CF

// 23 00 02 CC CF

// 23 00 02 08 DD

// 23 00 02 30 DD

// 23 00 02 59 DD

// 23 00 02 7F DD

// 23 00 02 A6 DD

// 23 00 02 CD DD

// 23 00 02 0E 15

// 23 00 02 0A E9

// 23 00 02 36 15

// 23 00 02 32 E9

// 23 00 02 5F 15

// 23 00 02 5B E9

// 23 00 02 85 15

// 23 00 02 81 E9

// 23 00 02 AD 15

// 23 00 02 A9 E9

// 23 00 02 D3 15

// 23 00 02 CF E9

// 23 00 02 0B 14

// 23 00 02 33 14

// 23 00 02 5C 14

// 23 00 02 82 14

// 23 00 02 AA 14

// 23 00 02 D0 14

// 23 00 02 0C 36

// 23 00 02 34 36

// 23 00 02 5D 36

// 23 00 02 83 36

// 23 00 02 AB 36

// 23 00 02 D1 36

// 23 00 02 0D 6B

// 23 00 02 35 6B

// 23 00 02 5E 6B

// 23 00 02 84 6B

// 23 00 02 AC 6B

// 23 00 02 D2 6B

// 23 00 02 13 5A

// 23 00 02 0F 94

// 23 00 02 3B 5A

// 23 00 02 37 94

// 23 00 02 64 5A

// 23 00 02 60 94

// 23 00 02 8A 5A

// 23 00 02 86 94

// 23 00 02 B2 5A

// 23 00 02 AE 94

// 23 00 02 D8 5A

// 23 00 02 D4 94

// 23 00 02 10 D1

// 23 00 02 38 D1

// 23 00 02 61 D1

// 23 00 02 87 D1

// 23 00 02 AF D1

// 23 00 02 D5 D1

// 23 00 02 11 04

// 23 00 02 39 04

// 23 00 02 62 04

// 23 00 02 88 04

// 23 00 02 B0 04

// 23 00 02 D6 04

// 23 00 02 12 05

// 23 00 02 3A 05

// 23 00 02 63 05

// 23 00 02 89 05

// 23 00 02 B1 05

// 23 00 02 D7 05

// 23 00 02 18 AA

// 23 00 02 14 36

// 23 00 02 42 AA

// 23 00 02 3D 36

// 23 00 02 69 AA

// 23 00 02 65 36

// 23 00 02 8F AA

// 23 00 02 8B 36

// 23 00 02 B7 AA

// 23 00 02 B3 36

// 23 00 02 DD AA

// 23 00 02 D9 36

// 23 00 02 15 74

// 23 00 02 3F 74

// 23 00 02 66 74

// 23 00 02 8C 74

// 23 00 02 B4 74

// 23 00 02 DA 74

// 23 00 02 16 9F

// 23 00 02 40 9F

// 23 00 02 67 9F

// 23 00 02 8D 9F

// 23 00 02 B5 9F

// 23 00 02 DB 9F

// 23 00 02 17 DC

// 23 00 02 41 DC

// 23 00 02 68 DC

// 23 00 02 8E DC

// 23 00 02 B6 DC

// 23 00 02 DC DC

// 23 00 02 1D FF

// 23 00 02 19 03

// 23 00 02 47 FF

// 23 00 02 43 03

// 23 00 02 6E FF

// 23 00 02 6A 03

// 23 00 02 94 FF

// 23 00 02 90 03

// 23 00 02 BC FF

// 23 00 02 B8 03

// 23 00 02 E2 FF

// 23 00 02 DE 03

// 23 00 02 1A 35

// 23 00 02 44 35

// 23 00 02 6B 35

// 23 00 02 91 35

// 23 00 02 B9 35

// 23 00 02 DF 35

// 23 00 02 1B 45

// 23 00 02 45 45

// 23 00 02 6C 45

// 23 00 02 92 45

// 23 00 02 BA 45

// 23 00 02 E0 45

// 23 00 02 1C 55

// 23 00 02 46 55

// 23 00 02 6D 55

// 23 00 02 93 55

// 23 00 02 BB 55

// 23 00 02 E1 55

// 23 00 02 22 FF

// 23 00 02 1E 68

// 23 00 02 4C FF

// 23 00 02 48 68

// 23 00 02 73 FF

// 23 00 02 6F 68

// 23 00 02 99 FF

// 23 00 02 95 68

// 23 00 02 C1 FF

// 23 00 02 BD 68

// 23 00 02 E7 FF

// 23 00 02 E3 68

// 23 00 02 1F 7E

// 23 00 02 49 7E

// 23 00 02 70 7E

// 23 00 02 96 7E

// 23 00 02 BE 7E

// 23 00 02 E4 7E

// 23 00 02 20 97

// 23 00 02 4A 97

// 23 00 02 71 97

// 23 00 02 97 97

// 23 00 02 BF 97

// 23 00 02 E5 97

// 23 00 02 21 B5

// 23 00 02 4B B5

// 23 00 02 72 B5

// 23 00 02 98 B5

// 23 00 02 C0 B5

// 23 00 02 E6 B5

// 23 00 02 25 F0

// 23 00 02 23 E8

// 23 00 02 4F F0

// 23 00 02 4D E8

// 23 00 02 76 F0

// 23 00 02 74 E8

// 23 00 02 9C F0

// 23 00 02 9A E8

// 23 00 02 C4 F0

// 23 00 02 C2 E8

// 23 00 02 EA F0

// 23 00 02 E8 E8

// 23 00 02 24 FF

// 23 00 02 4E FF

// 23 00 02 75 FF

// 23 00 02 9B FF

// 23 00 02 C3 FF

// 23 00 02 E9 FF

// 23 00 02 FE 3D

// 23 00 02 00 04

// 23 00 02 FE 23

// 23 00 02 08 82

// 23 00 02 0A 00

// 23 00 02 0B 00

// 23 00 02 0C 01

// 23 00 02 16 00

// 23 00 02 18 02

// 23 00 02 1B 04

// 23 00 02 19 04

// 23 00 02 1C 81

// 23 00 02 1F 00

// 23 00 02 20 03

// 23 00 02 23 04

// 23 00 02 21 01

// 23 00 02 54 63

// 23 00 02 55 54

// 23 00 02 6E 45

// 23 00 02 6D 36

// 23 00 02 FE 3D

// 23 00 02 55 78

// 23 00 02 FE 20

// 23 00 02 26 30

// 23 00 02 FE 3D

// 23 00 02 20 71

// 23 00 02 50 8F

// 23 00 02 51 8F

// 23 00 02 FE 00

// 23 00 02 35 00

05 78 01 11

05 00 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

disp_timings0: display-timings {

native-mode = <&dsi0_timing0>;

dsi0_timing0: timing0 {

clock-frequency = <148000000>;

hactive = <1200>;

vactive = <1920>;

hfront-porch = <80>;

hsync-len = <10>;

hback-porch = <60>;

vfront-porch = <16>;

vsync-len = <2>;

vback-porch = <25>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi: endpoint {

remote-endpoint = <&dsi_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi>;

};

};

};

};

&dsi1 {

status = "disabled";

//rockchip,lane-rate = <1000>;

dsi1_panel: panel@0 {

status = "okay";

compatible = "simple-panel-dsi";

reg = <0>;

backlight = <&backlight>;

reset-delay-ms = <10>;

enable-delay-ms = <10>;

prepare-delay-ms = <10>;

unprepare-delay-ms = <10>;

disable-delay-ms = <10>;

width-mm = <68>;

height-mm = <121>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_NO_EOT_PACKET)>;

dsi,format = <MIPI_DSI_FMT_RGB888>;

dsi,lanes = <4>;

panel-init-sequence = [

23 00 02 FE 21

23 00 02 04 00

23 00 02 00 64

23 00 02 2A 00

23 00 02 26 64

23 00 02 54 00

23 00 02 50 64

23 00 02 7B 00

23 00 02 77 64

23 00 02 A2 00

23 00 02 9D 64

23 00 02 C9 00

23 00 02 C5 64

23 00 02 01 71

23 00 02 27 71

23 00 02 51 71

23 00 02 78 71

23 00 02 9E 71

23 00 02 C6 71

23 00 02 02 89

23 00 02 28 89

23 00 02 52 89

23 00 02 79 89

23 00 02 9F 89

23 00 02 C7 89

23 00 02 03 9E

23 00 02 29 9E

23 00 02 53 9E

23 00 02 7A 9E

23 00 02 A0 9E

23 00 02 C8 9E

23 00 02 09 00

23 00 02 05 B0

23 00 02 31 00

23 00 02 2B B0

23 00 02 5A 00

23 00 02 55 B0

23 00 02 80 00

23 00 02 7C B0

23 00 02 A7 00

23 00 02 A3 B0

23 00 02 CE 00

23 00 02 CA B0

23 00 02 06 C0

23 00 02 2D C0

23 00 02 56 C0

23 00 02 7D C0

23 00 02 A4 C0

23 00 02 CB C0

23 00 02 07 CF

23 00 02 2F CF

23 00 02 58 CF

23 00 02 7E CF

23 00 02 A5 CF

23 00 02 CC CF

23 00 02 08 DD

23 00 02 30 DD

23 00 02 59 DD

23 00 02 7F DD

23 00 02 A6 DD

23 00 02 CD DD

23 00 02 0E 15

23 00 02 0A E9

23 00 02 36 15

23 00 02 32 E9

23 00 02 5F 15

23 00 02 5B E9

23 00 02 85 15

23 00 02 81 E9

23 00 02 AD 15

23 00 02 A9 E9

23 00 02 D3 15

23 00 02 CF E9

23 00 02 0B 14

23 00 02 33 14

23 00 02 5C 14

23 00 02 82 14

23 00 02 AA 14

23 00 02 D0 14

23 00 02 0C 36

23 00 02 34 36

23 00 02 5D 36

23 00 02 83 36

23 00 02 AB 36

23 00 02 D1 36

23 00 02 0D 6B

23 00 02 35 6B

23 00 02 5E 6B

23 00 02 84 6B

23 00 02 AC 6B

23 00 02 D2 6B

23 00 02 13 5A

23 00 02 0F 94

23 00 02 3B 5A

23 00 02 37 94

23 00 02 64 5A

23 00 02 60 94

23 00 02 8A 5A

23 00 02 86 94

23 00 02 B2 5A

23 00 02 AE 94

23 00 02 D8 5A

23 00 02 D4 94

23 00 02 10 D1

23 00 02 38 D1

23 00 02 61 D1

23 00 02 87 D1

23 00 02 AF D1

23 00 02 D5 D1

23 00 02 11 04

23 00 02 39 04

23 00 02 62 04

23 00 02 88 04

23 00 02 B0 04

23 00 02 D6 04

23 00 02 12 05

23 00 02 3A 05

23 00 02 63 05

23 00 02 89 05

23 00 02 B1 05

23 00 02 D7 05

23 00 02 18 AA

23 00 02 14 36

23 00 02 42 AA

23 00 02 3D 36

23 00 02 69 AA

23 00 02 65 36

23 00 02 8F AA

23 00 02 8B 36

23 00 02 B7 AA

23 00 02 B3 36

23 00 02 DD AA

23 00 02 D9 36

23 00 02 15 74

23 00 02 3F 74

23 00 02 66 74

23 00 02 8C 74

23 00 02 B4 74

23 00 02 DA 74

23 00 02 16 9F

23 00 02 40 9F

23 00 02 67 9F

23 00 02 8D 9F

23 00 02 B5 9F

23 00 02 DB 9F

23 00 02 17 DC

23 00 02 41 DC

23 00 02 68 DC

23 00 02 8E DC

23 00 02 B6 DC

23 00 02 DC DC

23 00 02 1D FF

23 00 02 19 03

23 00 02 47 FF

23 00 02 43 03

23 00 02 6E FF

23 00 02 6A 03

23 00 02 94 FF

23 00 02 90 03

23 00 02 BC FF

23 00 02 B8 03

23 00 02 E2 FF

23 00 02 DE 03

23 00 02 1A 35

23 00 02 44 35

23 00 02 6B 35

23 00 02 91 35

23 00 02 B9 35

23 00 02 DF 35

23 00 02 1B 45

23 00 02 45 45

23 00 02 6C 45

23 00 02 92 45

23 00 02 BA 45

23 00 02 E0 45

23 00 02 1C 55

23 00 02 46 55

23 00 02 6D 55

23 00 02 93 55

23 00 02 BB 55

23 00 02 E1 55

23 00 02 22 FF

23 00 02 1E 68

23 00 02 4C FF

23 00 02 48 68

23 00 02 73 FF

23 00 02 6F 68

23 00 02 99 FF

23 00 02 95 68

23 00 02 C1 FF

23 00 02 BD 68

23 00 02 E7 FF

23 00 02 E3 68

23 00 02 1F 7E

23 00 02 49 7E

23 00 02 70 7E

23 00 02 96 7E

23 00 02 BE 7E

23 00 02 E4 7E

23 00 02 20 97

23 00 02 4A 97

23 00 02 71 97

23 00 02 97 97

23 00 02 BF 97

23 00 02 E5 97

23 00 02 21 B5

23 00 02 4B B5

23 00 02 72 B5

23 00 02 98 B5

23 00 02 C0 B5

23 00 02 E6 B5

23 00 02 25 F0

23 00 02 23 E8

23 00 02 4F F0

23 00 02 4D E8

23 00 02 76 F0

23 00 02 74 E8

23 00 02 9C F0

23 00 02 9A E8

23 00 02 C4 F0

23 00 02 C2 E8

23 00 02 EA F0

23 00 02 E8 E8

23 00 02 24 FF

23 00 02 4E FF

23 00 02 75 FF

23 00 02 9B FF

23 00 02 C3 FF

23 00 02 E9 FF

23 00 02 FE 3D

23 00 02 00 04

23 00 02 FE 23

23 00 02 08 82

23 00 02 0A 00

23 00 02 0B 00

23 00 02 0C 01

23 00 02 16 00

23 00 02 18 02

23 00 02 1B 04

23 00 02 19 04

23 00 02 1C 81

23 00 02 1F 00

23 00 02 20 03

23 00 02 23 04

23 00 02 21 01

23 00 02 54 63

23 00 02 55 54

23 00 02 6E 45

23 00 02 6D 36

23 00 02 FE 3D

23 00 02 55 78

23 00 02 FE 20

23 00 02 26 30

23 00 02 FE 3D

23 00 02 20 71

23 00 02 50 8F

23 00 02 51 8F

23 00 02 FE 00

23 00 02 35 00

05 78 01 11

05 00 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

disp_timings1: display-timings {

native-mode = <&dsi1_timing0>;

dsi1_timing0: timing0 {

clock-frequency = <132000000>;

hactive = <1080>;

vactive = <1920>;

hfront-porch = <15>;

hsync-len = <4>;

hback-porch = <30>;

vfront-porch = <15>;

vsync-len = <2>;

vback-porch = <15>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi1: endpoint {

remote-endpoint = <&dsi1_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi1_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi1>;

};

};

};

};

&gpu {

mali-supply = <&vdd_gpu_s0>;

mem-supply = <&vdd_gpu_mem_s0>;

status = "okay";

};

&i2s0_8ch {

status = "okay";

pinctrl-0 = <&i2s0_lrck

&i2s0_sclk

&i2s0_sdi0

&i2s0_sdo0>;

};

&i2s2_2ch {

pinctrl-0 = <&i2s2m1_lrck &i2s2m1_sclk &i2s2m1_sdi &i2s2m1_sdo>;

rockchip,bclk-fs = <32>;

status = "disabled";

};

&iep {

status = "okay";

};

&iep_mmu {

status = "okay";

};

&jpegd {

status = "okay";

};

&jpegd_mmu {

status = "okay";

};

&jpege_ccu {

status = "okay";

};

&jpege0 {

status = "okay";

};

&jpege0_mmu {

status = "okay";

};

&jpege1 {

status = "okay";

};

&jpege1_mmu {

status = "okay";

};

&jpege2 {

status = "okay";

};

&jpege2_mmu {

status = "okay";

};

&jpege3 {

status = "okay";

};

&jpege3_mmu {

status = "okay";

};

&mpp_srv {

status = "okay";

};

&rga3_core0 {

status = "okay";

};

&rga3_0_mmu {

status = "okay";

};

&rga3_core1 {

status = "okay";

};

&rga3_1_mmu {

status = "okay";

};

&rga2 {

status = "okay";

};

&rknpu {

rknpu-supply = <&vdd_npu_s0>;

mem-supply = <&vdd_npu_mem_s0>;

status = "okay";

};

&rknpu_mmu {

status = "okay";

};

&rkvdec_ccu {

status = "okay";

};

&rkvdec0 {

status = "okay";

};

&rkvdec0_mmu {

status = "okay";

};

&rkvdec1 {

status = "okay";

};

&rkvdec1_mmu {

status = "okay";

};

&rkvenc_ccu {

status = "okay";

};

&rkvenc0 {

venc-supply = <&vdd_vdenc_s0>;

mem-supply = <&vdd_vdenc_mem_s0>;

status = "okay";

};

&rkvenc0_mmu {

status = "okay";

};

&rkvenc1 {

venc-supply = <&vdd_vdenc_s0>;

mem-supply = <&vdd_vdenc_mem_s0>;

status = "okay";

};

&rkvenc1_mmu {

status = "okay";

};

&rkvtunnel {

status = "okay";

};

&rockchip_suspend {

status = "okay";

rockchip,sleep-debug-en = <1>;

};

&saradc {

status = "okay";

vref-supply = <&vcc_1v8_s0>;

};

&sdhci {

bus-width = <8>;

no-sdio;

no-sd;

non-removable;

max-frequency = <200000000>;

mmc-hs400-1_8v;

mmc-hs400-enhanced-strobe;

full-pwr-cycle-in-suspend;

status = "okay";

};

&sdmmc {

max-frequency = <150000000>;

no-sdio;

no-mmc;

bus-width = <4>;

cap-mmc-highspeed;

cap-sd-highspeed;

disable-wp;

sd-uhs-sdr104;

vqmmc-supply = <&vccio_sd_s0>;

status = "disabled";

};

&tsadc {

status = "okay";

};

&u2phy0 {

status = "okay";

};

&u2phy1 {

status = "okay";

};

&u2phy2 {

status = "okay";

};

&u2phy3 {

status = "okay";

};

&u2phy0_otg {

status = "okay";

};

&u2phy1_otg {

status = "okay";

};

&u2phy2_host {

status = "okay";

};

&u2phy3_host {

status = "okay";

};

&usb_host0_ehci {

status = "okay";

};

&usb_host0_ohci {

status = "okay";

};

&usb_host1_ehci {

status = "okay";

};

&usb_host1_ohci {

status = "okay";

};

&usbdp_phy0 {

status = "okay";

};

&usbdp_phy0_dp {

status = "okay";

};

&usbdp_phy0_u3 {

status = "okay";

};

&usbdp_phy1 {

status = "okay";

};

&usbdp_phy1_dp {

status = "okay";

};

&usbdp_phy1_u3 {

status = "okay";

};

&usbdrd3_0 {

status = "okay";

};

&usbdrd_dwc3_0 {

dr_mode = "otg";

status = "okay";

};

&usbhost3_0 {

status = "okay";

};

&usbhost_dwc3_0 {

status = "okay";

};

&usbdrd3_1 {

status = "okay";

};

&usbdrd_dwc3_1 {

status = "okay";

};

&vdpu {

status = "okay";

};

&vdpu_mmu {

status = "okay";

};

&vepu {

status = "okay";

};

&vop {

status = "okay";

vop-supply = <&vdd_log_s0>;

};

&vop_mmu {

status = "okay";

};

/* vp0 & vp1 splice for 8K output */

&vp0 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER0 | 1 << ROCKCHIP_VOP2_ESMART0)>;

rockchip,primary-plane = <ROCKCHIP_VOP2_ESMART0>;

};

&vp1 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER1 | 1 << ROCKCHIP_VOP2_ESMART1)>;

rockchip,primary-plane = <ROCKCHIP_VOP2_ESMART1>;

};

&vp2 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER2 | 1 << ROCKCHIP_VOP2_ESMART2)>;

rockchip,primary-plane = <ROCKCHIP_VOP2_ESMART2>;

};

&vp3 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER3 | 1 << ROCKCHIP_VOP2_ESMART3)>;

rockchip,primary-plane = <ROCKCHIP_VOP2_ESMART3>;

};

Y:\new_disk_4t\wyb\GroundStation\yy3588_android14.0\kernel-6.1\arch\arm64\boot\dts\rockchip63版本04格式排版-只适配荣品的8寸屏\rk3588-evb7-lp4.dtsi

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/*

* Copyright (c) 2021 Rockchip Electronics Co., Ltd.

*

*/

#include "dt-bindings/usb/pd.h"

#include "rk3588.dtsi"

#include "rk3588-evb.dtsi"

#include "rk3588-rk806-single.dtsi"

/ {

/* If hdmirx node is disabled, delete the reserved-memory node here. */

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

/* Reserve 256MB memory for hdmirx-controller@fdee0000 */

cma {

compatible = "shared-dma-pool";

reusable;

reg = <0x0 (256 * 0x100000) 0x0 (256 * 0x100000)>;

linux,cma-default;

};

};

es8388_sound: es8388-sound {

status = "okay";

compatible = "rockchip,multicodecs-card";

rockchip,card-name = "rockchip-es8388";

hp-det-gpio = <&gpio1 RK_PC4 GPIO_ACTIVE_LOW>;

io-channels = <&saradc 3>;

io-channel-names = "adc-detect";

keyup-threshold-microvolt = <1800000>;

poll-interval = <100>;

spk-con-gpio = <&gpio4 RK_PA2 GPIO_ACTIVE_HIGH>;

hp-con-gpio = <&gpio4 RK_PA7 GPIO_ACTIVE_HIGH>;

rockchip,pre-power-on-delay-ms = <30>;

rockchip,post-power-down-delay-ms = <40>;

rockchip,format = "i2s";

rockchip,mclk-fs = <256>;

rockchip,cpu = <&i2s0_8ch>;

rockchip,codec = <&es8388>;

rockchip,audio-routing =

"Headphone", "LOUT1",

"Headphone", "ROUT1",

"Speaker", "LOUT2",

"Speaker", "ROUT2",

"Headphone", "Headphone Power",

"Headphone", "Headphone Power",

"Speaker", "Speaker Power",

"Speaker", "Speaker Power",

"LINPUT1", "Main Mic",

"LINPUT2", "Main Mic",

"RINPUT1", "Headset Mic",

"RINPUT2", "Headset Mic";

pinctrl-names = "default";

pinctrl-0 = <&hp_det>;

play-pause-key {

label = "playpause";

linux,code = <KEY_PLAYPAUSE>;

press-threshold-microvolt = <2000>;

};

};

fan: pwm-fan {

compatible = "pwm-fan";

#cooling-cells = <2>;

pwms = <&pwm3 0 50000 0>;

cooling-levels = <0 50 100 150 200 255>;

rockchip,temp-trips = <

50000 1

55000 2

60000 3

65000 4

70000 5

>;

};

hdmiin-sound {

compatible = "rockchip,hdmi";

rockchip,mclk-fs = <128>;

rockchip,format = "i2s";

rockchip,bitclock-master = <&hdmirx_ctrler>;

rockchip,frame-master = <&hdmirx_ctrler>;

rockchip,card-name = "rockchip,hdmiin";

rockchip,cpu = <&i2s7_8ch>;

rockchip,codec = <&hdmirx_ctrler 0>;

rockchip,jack-det;

};

pcie20_avdd0v85: pcie20-avdd0v85 {

compatible = "regulator-fixed";

regulator-name = "pcie20_avdd0v85";

regulator-boot-on;

regulator-always-on;

regulator-min-microvolt = <850000>;

regulator-max-microvolt = <850000>;

vin-supply = <&vdd_0v85_s0>;

};

pcie20_avdd1v8: pcie20-avdd1v8 {

compatible = "regulator-fixed";

regulator-name = "pcie20_avdd1v8";

regulator-boot-on;

regulator-always-on;

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

vin-supply = <&avcc_1v8_s0>;

};

pcie30_avdd0v75: pcie30-avdd0v75 {

compatible = "regulator-fixed";

regulator-name = "pcie30_avdd0v75";

regulator-boot-on;

regulator-always-on;

regulator-min-microvolt = <750000>;

regulator-max-microvolt = <750000>;

vin-supply = <&avdd_0v75_s0>;

};

pcie30_avdd1v8: pcie30-avdd1v8 {

compatible = "regulator-fixed";

regulator-name = "pcie30_avdd1v8";

regulator-boot-on;

regulator-always-on;

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

vin-supply = <&avcc_1v8_s0>;

};

sdio_pwrseq: sdio-pwrseq {

compatible = "mmc-pwrseq-simple";

clocks = <&hym8563>;

clock-names = "ext_clock";

pinctrl-names = "default";

pinctrl-0 = <&wifi_enable_h>;

/*

* On the module itself this is one of these (depending

* on the actual card populated):

* - SDIO_RESET_L_WL_REG_ON

* - PDN (power down when low)

*/

post-power-on-delay-ms = <200>;

reset-gpios = <&gpio0 RK_PC4 GPIO_ACTIVE_LOW>;

};

rk_headset: rk-headset {

status = "disabled";

compatible = "rockchip_headset";

headset_gpio = <&gpio1 RK_PD5 GPIO_ACTIVE_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&hp_det>;

io-channels = <&saradc 3>;

};

vcc_1v1_nldo_s3: vcc-1v1-nldo-s3 {

compatible = "regulator-fixed";

regulator-name = "vcc_1v1_nldo_s3";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <1100000>;

regulator-max-microvolt = <1100000>;

vin-supply = <&vcc5v0_sys>;

};

vcc3v3_lcd_n: vcc3v3-lcd0-n {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_lcd0_n";

regulator-boot-on;

enable-active-high;

gpio = <&gpio4 RK_PC2 GPIO_ACTIVE_HIGH>;

vin-supply = <&vcc_1v8_s0>;

};

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio2 RK_PC5 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

vcc5v0_host: vcc5v0-host {

compatible = "regulator-fixed";

regulator-name = "vcc5v0_host";

regulator-boot-on;

regulator-always-on;

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

enable-active-high;

gpio = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;

vin-supply = <&vcc5v0_usb>;

pinctrl-names = "default";

pinctrl-0 = <&vcc5v0_host_en>;

};

// 2025/8/21 9:39 close for LCD POWER

// vcc_mipicsi0: vcc-mipicsi0-regulator {

// compatible = "regulator-fixed";

// gpio = <&gpio1 RK_PD2 GPIO_ACTIVE_HIGH>;

// pinctrl-names = "default";

// pinctrl-0 = <&mipicsi0_pwr>;

// regulator-name = "vcc_mipicsi0";

// enable-active-high;

// };

// 2025/8/20 20:21 close for LCD0 pwm1m1

// vcc_mipicsi1: vcc-mipicsi1-regulator {

// compatible = "regulator-fixed";

// gpio = <&gpio1 RK_PD3 GPIO_ACTIVE_HIGH>;

// pinctrl-names = "default";

// pinctrl-0 = <&mipicsi1_pwr>;

// regulator-name = "vcc_mipicsi1";

// enable-active-high;

// };

vcc_mipidcphy0: vcc-mipidcphy0-regulator {

compatible = "regulator-fixed";

gpio = <&gpio2 RK_PC4 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&mipidcphy0_pwr>;

regulator-name = "vcc_mipidcphy0";

enable-active-high;

};

vcc_3v3_sd_s0: vcc-3v3-sd-s0-regulator {

compatible = "regulator-fixed";

gpio = <&gpio0 RK_PB7 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&sd_s0_pwr>;

regulator-name = "vcc_3v3_sd_s0";

enable-active-high;

};

wireless_bluetooth: wireless-bluetooth {

compatible = "bluetooth-platdata";

clocks = <&hym8563>;

clock-names = "ext_clock";

uart_rts_gpios = <&gpio4 RK_PC4 GPIO_ACTIVE_LOW>;

pinctrl-names = "default", "rts_gpio";

pinctrl-0 = <&uart9m0_rtsn>, <&bt_reset_gpio>, <&bt_wake_gpio>, <&bt_irq_gpio>;

pinctrl-1 = <&uart9_gpios>;

BT,reset_gpio = <&gpio0 RK_PC6 GPIO_ACTIVE_HIGH>;

BT,wake_gpio = <&gpio0 RK_PC5 GPIO_ACTIVE_HIGH>;

BT,wake_host_irq = <&gpio0 RK_PA0 GPIO_ACTIVE_HIGH>;

status = "okay";

};

wireless_wlan: wireless-wlan {

compatible = "wlan-platdata";

wifi_chip_type = "ap6398s";

pinctrl-names = "default";

pinctrl-0 = <&wifi_host_wake_irq>;

WIFI,host_wake_irq = <&gpio0 RK_PB2 GPIO_ACTIVE_HIGH>;

WIFI,poweren_gpio = <&gpio0 RK_PC4 GPIO_ACTIVE_HIGH>;

status = "okay";

};

};

&backlight {

pwms = <&pwm1 0 25000 0>;

status = "okay";

};

&combphy0_ps {

status = "okay";

};

&combphy1_ps {

status = "okay";

};

&combphy2_psu {

status = "okay";

};

&dp0 {

pinctrl-names = "default";

pinctrl-0 = <&vga_hpdin_l>;

hpd-gpios = <&gpio3 RK_PA6 GPIO_ACTIVE_HIGH>;

status = "okay";

};

&dp0_in_vp2 {

status = "okay";

};

&dp1 {

pinctrl-names = "default";

pinctrl-0 = <&dp1m0_pins>;

status = "okay";

};

&dp1_in_vp2 {

status = "okay";

};

/*

* mipi_dcphy0 needs to be enabled

* when dsi0 is enabled

*/

&dsi0 {

status = "okay";

};

&dsi0_in_vp2 {

status = "disabled";

};

&dsi0_in_vp3 {

status = "okay";

};

&dsi0_panel {

power-supply = <&vcc3v3_lcd_n>;

reset-gpios = <&gpio4 RK_PC6 GPIO_ACTIVE_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&lcd_rst_gpio>;

};

/*

* mipi_dcphy1 needs to be enabled

* when dsi1 is enabled

*/

&dsi1 {

status = "disabled";

};

&dsi1_in_vp2 {

status = "disabled";

};

&dsi1_in_vp3 {

status = "disabled";

};

&dsi1_panel {

power-supply = <&vcc3v3_lcd_n>;

/*

* because in hardware, the two screens share the reset pin,

* so reset-gpios need only in dsi1 enable and dsi0 disabled

* case.

*/

//reset-gpios = <&gpio0 RK_PD3 GPIO_ACTIVE_LOW>;

//pinctrl-names = "default";

//pinctrl-0 = <&lcd_rst_gpio>;

};

&gmac1 {

/* Use rgmii-rxid mode to disable rx delay inside Soc */

phy-mode = "rgmii-rxid";

clock_in_out = "output";

snps,reset-gpio = <&gpio3 RK_PB7 GPIO_ACTIVE_LOW>;

snps,reset-active-low;

/* Reset time is 20ms, 100ms for rtl8211f */

snps,reset-delays-us = <0 20000 100000>;

pinctrl-names = "default";

pinctrl-0 = <&gmac1_miim

&gmac1_tx_bus2

&gmac1_rx_bus2

&gmac1_rgmii_clk

&gmac1_rgmii_bus>;

tx_delay = <0x43>;

/* rx_delay = <0x3f>; */

phy-handle = <&rgmii_phy>;

status = "okay";

};

&hdmi0 {

enable-gpios = <&gpio4 RK_PB1 GPIO_ACTIVE_HIGH>;

status = "okay";

};

&hdmi0_in_vp0 {

status = "okay";

};

&hdmi0_sound {

status = "okay";

};

&hdmi1 {

enable-gpios = <&gpio4 RK_PB2 GPIO_ACTIVE_HIGH>;

status = "okay";

};

&hdmi1_in_vp1 {

status = "okay";

};

&hdmi1_sound {

status = "okay";

};

/* Should work with at least 128MB cma reserved above. */

&hdmirx_ctrler {

status = "okay";

#sound-dai-cells = <1>;

/* Effective level used to trigger HPD: 0-low, 1-high */

hpd-trigger-level = <1>;

hdmirx-det-gpios = <&gpio1 RK_PD5 GPIO_ACTIVE_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&hdmim1_rx &hdmirx_det>;

};

&hdptxphy_hdmi0 {

status = "okay";

};

&hdptxphy_hdmi1 {

status = "okay";

};

&i2c0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&i2c0m2_xfer>;

vdd_cpu_big0_s0: vdd_cpu_big0_mem_s0: rk8602@42 {

compatible = "rockchip,rk8602";

reg = <0x42>;

vin-supply = <&vcc5v0_sys>;

regulator-compatible = "rk860x-reg";

regulator-name = "vdd_cpu_big0_s0";

regulator-min-microvolt = <550000>;

regulator-max-microvolt = <1050000>;

regulator-ramp-delay = <2300>;

rockchip,suspend-voltage-selector = <1>;

regulator-boot-on;

regulator-always-on;

regulator-state-mem {

regulator-off-in-suspend;

};

};

vdd_cpu_big1_s0: vdd_cpu_big1_mem_s0: rk8603@43 {

compatible = "rockchip,rk8603";

reg = <0x43>;

vin-supply = <&vcc5v0_sys>;

regulator-compatible = "rk860x-reg";

regulator-name = "vdd_cpu_big1_s0";

regulator-min-microvolt = <550000>;

regulator-max-microvolt = <1050000>;

regulator-ramp-delay = <2300>;

rockchip,suspend-voltage-selector = <1>;

regulator-boot-on;

regulator-always-on;

regulator-state-mem {

regulator-off-in-suspend;

};

};

};

&i2c1 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&i2c1m2_xfer>;

vdd_npu_s0: vdd_npu_mem_s0: rk8602@42 {

compatible = "rockchip,rk8602";

reg = <0x42>;

vin-supply = <&vcc5v0_sys>;

regulator-compatible = "rk860x-reg";

regulator-name = "vdd_npu_s0";

regulator-min-microvolt = <550000>;

regulator-max-microvolt = <950000>;

regulator-ramp-delay = <2300>;

rockchip,suspend-voltage-selector = <1>;

regulator-boot-on;

regulator-always-on;

regulator-state-mem {

regulator-off-in-suspend;

};

};

};

&i2c4 {

status = "okay";

pinctrl-0 = <&i2c4m1_xfer>;

ls_stk3332: light@47 {

compatible = "ls_stk3332";

status = "disabled";

reg = <0x47>;

type = <SENSOR_TYPE_LIGHT>;

irq_enable = <0>;

als_threshold_high = <100>;

als_threshold_low = <10>;

als_ctrl_gain = <2>; /* 0:x1 1:x4 2:x16 3:x64 */

poll_delay_ms = <100>;

};

ps_stk3332: proximity@47 {

compatible = "ps_stk3332";

status = "disabled";

reg = <0x47>;

type = <SENSOR_TYPE_PROXIMITY>;

//pinctrl-names = "default";

//pinctrl-0 = <&gpio3_c6>;

//irq-gpio = <&gpio3 RK_PC6 IRQ_TYPE_LEVEL_LOW>;

//irq_enable = <1>;

ps_threshold_high = <0x200>;

ps_threshold_low = <0x100>;

ps_ctrl_gain = <3>; /* 0:x1 1:x2 2:x5 3:x8 */

ps_led_current = <4>; /* 0:3.125mA 1:6.25mA 2:12.5mA 3:25mA 4:50mA 5:100mA*/

poll_delay_ms = <100>;

};

icm42607_acc: icm_acc@68 {

status = "okay";

compatible = "icm42607_acc";

reg = <0x68>;

irq-gpio = <&gpio4 RK_PC2 IRQ_TYPE_EDGE_RISING>;

irq_enable = <0>;

poll_delay_ms = <30>;

type = <SENSOR_TYPE_ACCEL>;

layout = <0>;

};

icm42607_gyro: icm_gyro@68 {

status = "okay";

compatible = "icm42607_gyro";

reg = <0x68>;

poll_delay_ms = <30>;

type = <SENSOR_TYPE_GYROSCOPE>;

layout = <0>;

};

};

&i2c5 {

status = "okay";

gt1x: gt1x@14 {

compatible = "goodix,gt1x";

reg = <0x14>;

pinctrl-names = "default";

pinctrl-0 = <&touch_gpio>;

goodix,rst-gpio = <&gpio3 RK_PC1 GPIO_ACTIVE_HIGH>;

goodix,irq-gpio = <&gpio3 RK_PC0 IRQ_TYPE_LEVEL_LOW>;

power-supply = <&vcc3v3_lcd_n>;

};

};

&i2c6 {

status = "okay";

hym8563: hym8563@51 {

compatible = "haoyu,hym8563";

reg = <0x51>;

#clock-cells = <0>;

clock-frequency = <32768>;

clock-output-names = "hym8563";

pinctrl-names = "default";

pinctrl-0 = <&hym8563_int>;

interrupt-parent = <&gpio0>;

interrupts = <RK_PB0 IRQ_TYPE_LEVEL_LOW>;

wakeup-source;

};

};

&i2c7 {

status = "okay";

es8388: es8388@11 {

status = "okay";

#sound-dai-cells = <0>;

compatible = "everest,es8388", "everest,es8323";

reg = <0x11>;

clocks = <&mclkout_i2s0>;

clock-names = "mclk";

assigned-clocks = <&mclkout_i2s0>;

assigned-clock-rates = <12288000>;

pinctrl-names = "default";

pinctrl-0 = <&i2s0_mclk>;

};

};

&i2s2_2ch {

pinctrl-0 = <&i2s2m0_sclk &i2s2m0_lrck &i2s2m0_sdi &i2s2m0_sdo>;

status = "disabled";

};

&i2s5_8ch {

status = "okay";

};

&i2s6_8ch {

status = "okay";

};

&i2s7_8ch {

status = "okay";

};

&mdio1 {

rgmii_phy: phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0x1>;

};

};

&mipi_dcphy0 {

status = "okay";

};

&mipi_dcphy1 {

status = "disabled";

};

&pcie2x1l0 {

reset-gpios = <&gpio1 RK_PB4 GPIO_ACTIVE_HIGH>;

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = <PHY_MODE_PCIE_AGGREGATION>;

status = "disabled";

};

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB3 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

pinctrl-names = "default";

pinctrl-0 = <&pcie30x4_clkreqn_m1>;

status = "disabled";

};

&pinctrl {

cam {

// 2025/8/21 9:39 close for LCD POWER

// mipicsi0_pwr: mipicsi0-pwr {

// rockchip,pins =

// /* camera power en */

// <1 RK_PD2 RK_FUNC_GPIO &pcfg_pull_none>;

// };

// 2025/8/20 20:21 close for LCD0 pwm1m1

// mipicsi1_pwr: mipicsi1-pwr {

// rockchip,pins =

// /* camera power en */

// <1 RK_PD3 RK_FUNC_GPIO &pcfg_pull_none>;

// };

mipidcphy0_pwr: mipidcphy0-pwr {

rockchip,pins =

/* camera power en */

<2 RK_PC4 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

vga {

vga_hpdin_l: vga-hpdin-l {

rockchip,pins = <3 RK_PA6 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

hdmi {

hdmirx_det: hdmirx-det {

rockchip,pins = <1 RK_PD5 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

headphone {

hp_det: hp-det {

rockchip,pins = <1 RK_PC4 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

hym8563 {

hym8563_int: hym8563-int {

rockchip,pins = <0 RK_PB0 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

lcd {

lcd_rst_gpio: lcd-rst-gpio {

rockchip,pins = <4 RK_PC6 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

pcie30x4 {

pcie30x4_clkreqn_m1: pcie30x4-clkreqn-m1 {

rockchip,pins = <4 RK_PB4 RK_FUNC_GPIO &pcfg_pull_down>;

};

};

sdio-pwrseq {

wifi_enable_h: wifi-enable-h {

rockchip,pins = <0 RK_PC4 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

sdmmc {

sd_s0_pwr: sd-s0-pwr {

rockchip,pins = <0 RK_PB7 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

touch {

touch_gpio: touch-gpio {

rockchip,pins =

<3 RK_PC1 RK_FUNC_GPIO &pcfg_pull_down>,

<3 RK_PC0 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

usb {

vcc5v0_host_en: vcc5v0-host-en {

rockchip,pins = <4 RK_PB0 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

wireless-bluetooth {

uart9_gpios: uart9-gpios {

rockchip,pins = <4 RK_PC4 RK_FUNC_GPIO &pcfg_pull_none>;

};

bt_reset_gpio: bt-reset-gpio {

rockchip,pins = <0 RK_PC6 RK_FUNC_GPIO &pcfg_pull_none>;

};

bt_wake_gpio: bt-wake-gpio {

rockchip,pins = <0 RK_PC5 RK_FUNC_GPIO &pcfg_pull_none>;

};

bt_irq_gpio: bt-irq-gpio {

rockchip,pins = <0 RK_PA0 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

wireless-wlan {

wifi_host_wake_irq: wifi-host-wake-irq {

rockchip,pins = <0 RK_PB2 RK_FUNC_GPIO &pcfg_pull_down>;

};

};

};

&pwm1 {

status = "okay";

pinctrl-0 = <&pwm1m1_pins>;

};

&pwm3 {

pinctrl-0 = <&pwm3m1_pins>;

status = "okay";

};

&route_dsi0 {

status = "okay";

connect = <&vp3_out_dsi0>;

};

&route_dsi1 {

status = "disabled";

connect = <&vp3_out_dsi1>;

};

&route_hdmi0 {

status = "okay";

};

&route_hdmi1 {

status = "okay";

};

&sata0 {

status = "okay";

};

&sdio {

max-frequency = <150000000>;

no-sd;

no-mmc;

bus-width = <4>;

disable-wp;

cap-sd-highspeed;

cap-sdio-irq;

keep-power-in-suspend;

mmc-pwrseq = <&sdio_pwrseq>;

non-removable;

pinctrl-names = "default";

pinctrl-0 = <&sdiom0_pins>;

sd-uhs-sdr104;

status = "okay";

};

&sdmmc {

status = "okay";

vmmc-supply = <&vcc_3v3_sd_s0>;

};

&uart9 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&uart9m0_xfer &uart9m0_ctsn>;

};

&u2phy0_otg {

status = "okay";

};

&u2phy1_otg {

phy-supply = <&vcc5v0_host>;

};

&u2phy2_host {

phy-supply = <&vcc5v0_host>;

};

&u2phy3_host {

phy-supply = <&vcc5v0_host>;

};

&usbdp_phy0 {

rockchip,dp-lane-mux = <2 3>;

status = "okay";

};

&usbdp_phy0_dp {

status = "okay";

};

&usbdp_phy0_u3 {

status = "okay";

};

&usbdp_phy1 {

maximum-speed = "high-speed";

rockchip,dp-lane-mux = <3 2 1 0>;

status = "okay";

};

&usbdp_phy1_dp {

status = "okay";

};

&usbdp_phy1_u3 {

status = "okay";

};

&usbdrd_dwc3_0 {

dr_mode = "otg";

extcon = <&u2phy0>;

status = "okay";

};

&usbdrd_dwc3_1 {

dr_mode = "host";

maximum-speed = "high-speed";

status = "okay";

};