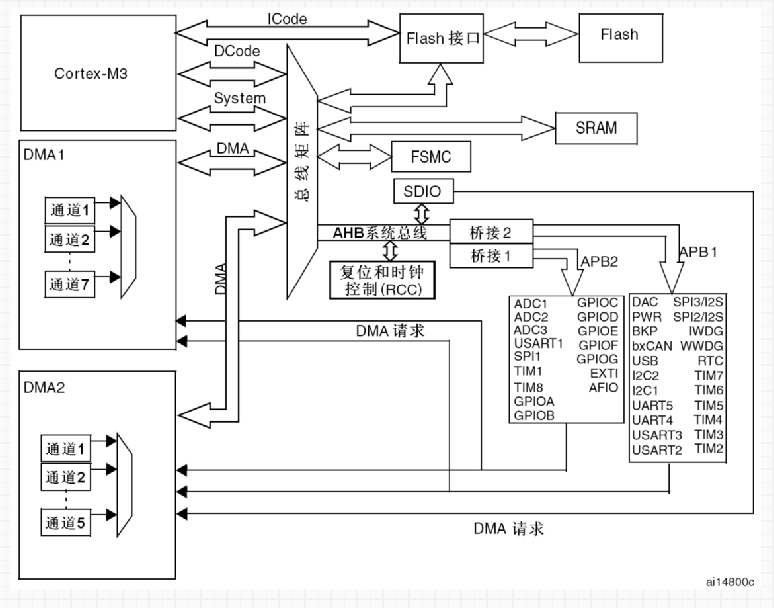

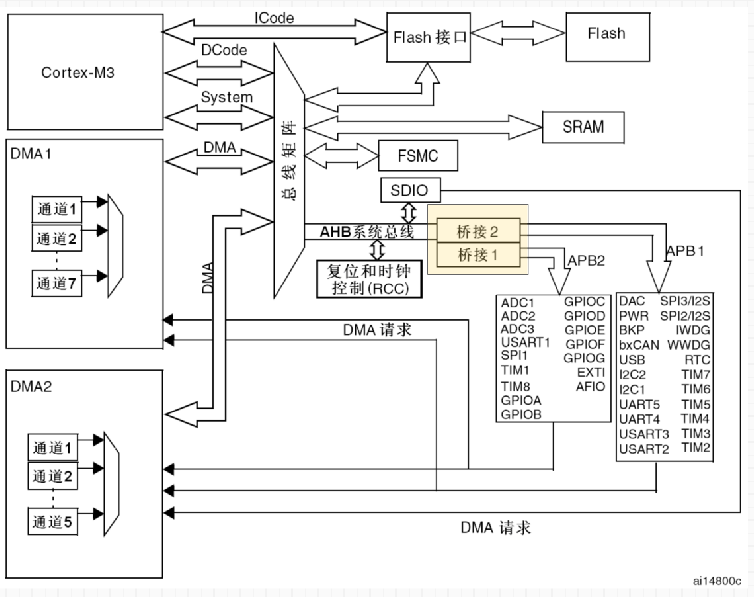

1. 总体架构

从宏观上了解下STM32的系统架构、各个模块之间的层级关系以及相互的影响

STM32架构核心:总线矩阵和多层AHB总线

STM32(基于ARM Cortex-M内核)采用了一种叫做总线矩阵(Bus Matrix) 和多层AHB(Advanced High-performance Bus) 的互联结构。你可以把它想象成一个城市复杂的道路系统:

主设备(Master):像CPU、DMA控制器这些能够发起读写操作的"车辆"。它们说:"我要去这个地方拿点东西(读)或者送点东西(写)"。

从设备(Slave):像Flash内存、SRAM、各种外设(GPIO, USART, SPI等)这些"目的地"或"仓库"。它们存储数据或等待被配置。

总线(Bus):连接主设备和从设备的"道路"。STM32内部有多条道路,让多辆车可以同时行驶而不堵塞。

核心问题 :CPU(一条高速路)想访问Flash(一个仓库),而DMA(另一条高速路)同时想访问SRAM(另一个仓库)。如果只有一条路,它们就会堵死。所以STM32用了多层总线矩阵 ,允许多个主设备同时访问不同的从设备,极大提高了效率。

在这个道路系统中,不同"等级"的道路速度不同:

高速路(AHB Bus):连接着核心(Cortex-M)、主要内存(Flash, SRAM)和DMA。速度最快。

普通公路(APB Bus):连接大部分外设,如UART, I2C, SPI等。速度相对较慢。

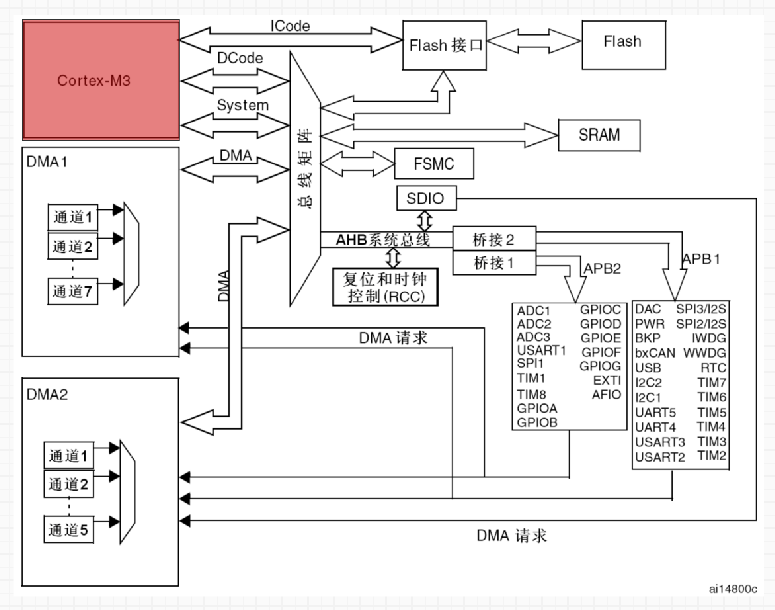

核心 Cortex-M Processor

角色:城市的"大脑"和"最高指挥中心"。

功能 :这是ARM公司设计的CPU核心,负责执行指令、计算、逻辑判断和控制整个芯片的运行。它通过I-Code, D-Code, System 等总线与外部连接。

I-Code总线:专门用于从Flash中取指令。

D-Code总线:专门用于从Flash中取数据(常量、查表等)。

System总线:用于访问内存(SRAM)和外设。

关联外设 :内核本身还包含一些内部外设,如NVIC(嵌套向量中断控制器) 和 SysTick(系统定时器)。

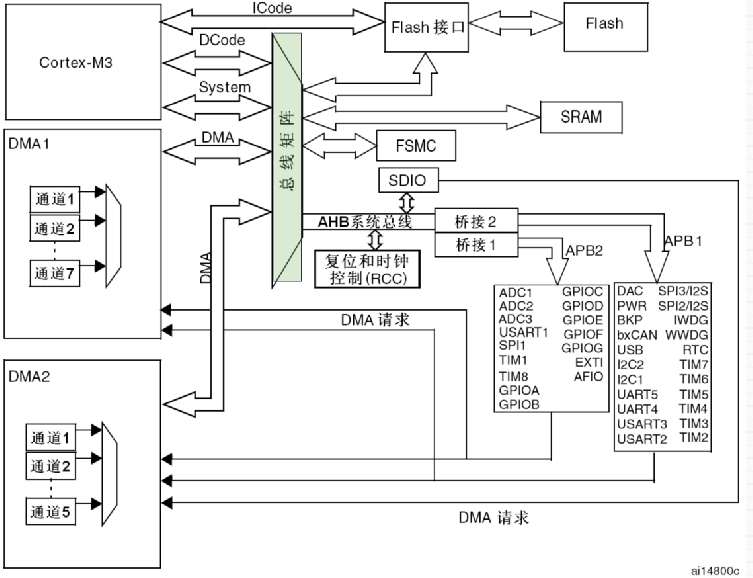

总线矩阵 (Bus Matrix) / 多层AHB总线 (Multi-Layer AHB Bus)

角色:城市的"智能交通枢纽"或"立交桥系统"。

功能 :这是STM32架构的核心。它连接了多个主设备(如CPU、DMA)和多个从设备(如Flash、SRAM、总线桥)。它的智能之处在于仲裁机制:

当多个主设备(如CPU和DMA1)同时想访问同一个从设备(如SRAM)时,仲裁器会根据优先级决定谁先谁后。

当多个主设备访问不同的从设备时(如CPU读Flash,DMA写SRAM),总线矩阵允许这两个传输同时进行,极大提升了并行效率和系统性能。

关联主设备:Cortex-M内核(通过其多条总线)、DMA控制器等。

关联从设备:Flash内存接口、SRAM控制器、AHB-APB桥等。

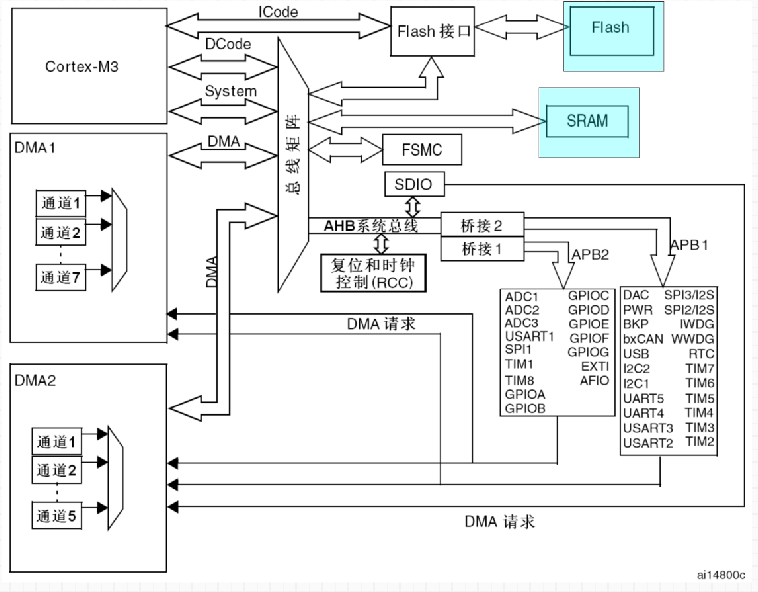

存储单元

主存储器 (Main Memory)

这是位于芯片内部的存储单元,速度最快,分为两大类:

Flash Memory (闪存)

作用 :用于存储程序代码(Code) 、常量数据(const) 以及中断向量表等。CPU通过I-Code总线 和D-Code总线访问它来取指和读取常量。

特点 :非易失性 ,断电后数据不丢失。读写速度比SRAM慢,因此CPU通常有指令预取队列 和ART加速器(F4/F7/H7系列)来缓冲和加速指令读取。

SRAM (静态随机存取存储器)

作用 :用于存放变量(全局变量、局部变量堆栈)、堆 以及运行时数据。CPU通过系统总线访问它。

特点 :易失性 ,断电后数据丢失。读写速度极快,可以与CPU时钟同步运行。

发展:高性能系列(如F7/H7)会有多块SRAM(如ITCM, DTCM, AXI SRAM, AHB SRAM),用于不同的数据路径,进一步优化性能。

CPU有专门的总线(I-Code, D-Code)直连Flash,保证了取指效率;同时通过系统总线访问SRAM。

桥接单元

桥接单元主要就是连接AHB高速总线 和APB低速总线的接口。它主要有两大功能:

协议转换:将AHB总线的通信协议转换为APB总线能理解的协议,反之亦然。就像是一个翻译官。

速度匹配:AHB总线通常运行在系统最高时钟频率(如72MHz, 168MHz),而APB总线可以分频运行在较低频率。桥接单元会处理好不同时钟域之间的同步,防止数据出错。

AHB to APB Bridge (AHB-APB桥)

APB2桥 :连接的是高速外设。

工作时钟:通常与AHB同频或分频比很小(如72MHz系统时钟下,APB2也是72MHz)。

挂载的外设:通常包括GPIOA-G, SPI1, TIM1, USART1, ADC1等对性能要求较高的外设。

APB1桥 :连接的是低速外设。

工作时钟:最大频率通常有限制(如72MHz系统时钟下,APB1最大36MHz)。

挂载的外设:通常包括TIM2-TIM7, SPI2/I2S2, SPI3/I2S3, USART2/3/4/5, I2C1/2, CAN, USB, DAC等。

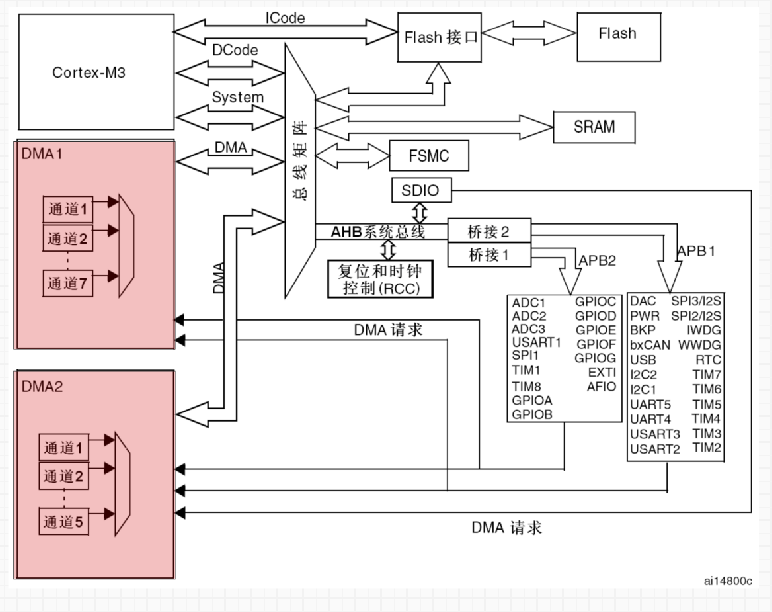

直接存储器访问控制器 (DMA Controller)

角色:高效的"物流搬运队"或"数据传送带"。

功能 :可以在不占用CPU的情况下,直接在"外设"和"内存"之间或"内存"与"内存"之间搬运大量数据。CPU只需要初始化好DMA,就可以去执行其他任务,等DMA搬运完成后再通过中断通知CPU。这极大地解放了CPU,是高效能处理(如音频流、ADC采样阵列、图像数据传输)的关键。

工作流程:DMA作为主设备,向总线矩阵发起请求,直接读写SRAM或外设的数据寄存器。

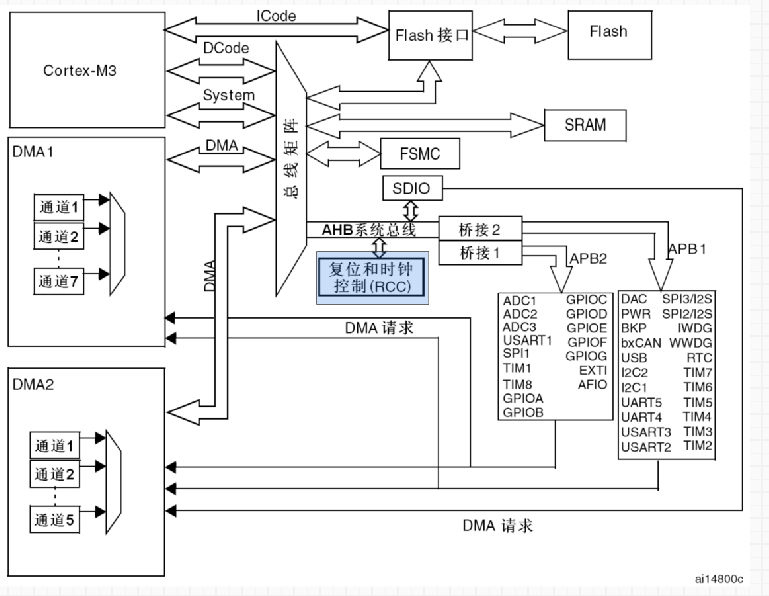

复位和时钟控制 (RCC)

角色:整个城市的"电力公司和节奏控制中心"。

功能:

复位控制:管理上电复位、欠压复位、看门狗复位等。

时钟控制 :这是它的核心功能。它包含振荡器(HSI, HSE, LSI, LSE)、PLL锁相环等。RCC负责选择和分配时钟源,并为系统内核、各个总线和所有外设提供所需的时钟信号。你可以通过配置RCC寄存器来开启/关闭各个外设的时钟,以达到节能的目的(未使用的模块不供电不给时钟),这也是低功耗设计的基础。

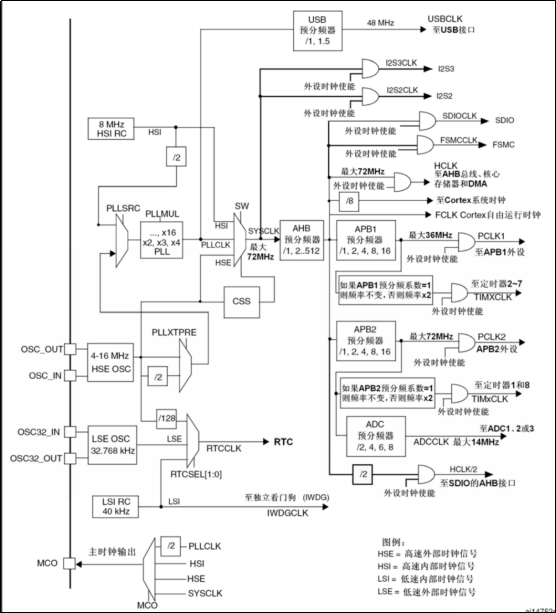

2. 时钟系统

可以把STM32的时钟系统想象成一个现代化的城市供水系统:

时钟源:像是不同的水源(江河、水库、地下水)。

PLL :像是水处理厂和加压泵站,能把水源加工成更高压力(频率)的水。

分频器 :像是减压阀,给不同需求的区域(外设)提供合适水压(频率)。

时钟树 :就像是错综复杂的城市水管网络。

使能控制 :就像是每个建筑门口的水阀,不用水就关上,节约资源。

核心框图:时钟树 (Clock Tree)

时钟系统的组成部分

1. 时钟源 (Water Sources) - 系统的源头

STM32有多个时钟源,分为高速和低速两类,提供了灵活性和冗余备份。

| 时钟源 | 缩写 | 类型 | 频率 | 特点与用途 |

|---|---|---|---|---|

| 高速外部时钟 | HSE | 外部 | 4-26MHz (通常8MHz) | 高精度 。由外部晶振/陶瓷谐振器提供,是系统主时钟 的首选,稳定可靠。 |

| 高速内部时钟 | HSI | 内部 | 8MHz (RC振荡器) | 芯片内置,成本低,启动快 ,但精度相对较差。可作为HSE的备份时钟,或用于不需要高精度的场合。 |

| 低速外部时钟 | LSE | 外部 | 32.768kHz | 高精度,低功耗 。通常连接32.768kHz手表晶振,专为实时时钟(RTC) 和低功耗模式设计。 |

| 低速内部时钟 | LSI | 内部 | ~32kHz (RC振荡器) | 芯片内置,精度低,但功耗很低 。主要用于独立看门狗(IWDG) 和自动唤醒单元(AWU),确保即使主时钟故障也能工作。 |

2. PLL (Water Treatment Plant & Pump Station) - 动力核心

-

角色 :锁相环。它是整个系统的"动力引擎"。

-

功能 :接受一个频率较低的时钟源(如HSE的8MHz或HSI的8MHz),通过倍频将其提升到一个非常高的频率,然后输出给系统内核和外设使用。

-

举例:这是STM32F103能"超频"到72MHz的关键。它接收8MHz的HSE,通过9倍频(8MHz x 9 = 72MHz),产生出72MHz的系统时钟(SYSCLK)。

3. 系统时钟 (SYSCLK) (Main Water Pipeline) - 主干道

-

角色 :所有时钟中最重要的一个,相当于城市的"主供水管道"。

-

来源:可由HSI、HSE或PLL输出直接提供。

-

去向:SYSCLK会被分派到各个地方,最主要的是送给:

-

AHB总线:通过AHB预分频器。

-

Cortex-M内核:内核的工作频率就等于SYSCLK。

-

4. 分频器 (Pressure Reducing Valves) - 分配与调节

系统时钟(SYSCLK)速度很快,但并非所有外设都需要这么高的速度。分频器负责"降压",为不同总线上的外设提供合适的时钟。

-

AHB Prescaler (AHB预分频器) :负责对SYSCLK进行分频,产生HCLK。

- HCLK :是送给Cortex-M内核、内存(Flash/SRAM)和DMA 的时钟。它的频率就是我们常说的"主频"(如72MHz)。

-

APB1 Prescaler (APB1预分频器) :对HCLK进行分频,产生PCLK1。

- PCLK1 :送给低速外设 (挂在APB1总线上的设备,如I2C, UART2/3/4/5, SPI2等)。它的频率最高为36MHz(在72MHz系统下通常分频为36MHz)。

-

APB2 Prescaler (APB2预分频器) :对HCLK进行分频,产生PCLK2。

- PCLK2 :送给高速外设 (挂在APB2总线上的设备,如GPIO, SPI1, ADC1, USART1, TIM1等)。它的频率最高为72MHz。

为什么TIM的时钟会翻倍?

这是一个重要知识点:虽然APB1的时钟PCLK1只有36MHz,但如果你看到定时器(如TIM2-TIM7)的时钟是72MHz,那是因为当APBx的分频系数不为1时,定时器连接的时钟会自动x2,以保证定时器的性能。

5. 时钟输出 (MCO) (Water Monitoring Outlet)

-

角色 :主时钟输出。

-

功能 :STM32可以将内部的某个时钟(如HSI、HSE、PLL、SYSCLK)通过一个特定的引脚(PA8)输出到芯片外部,用于同步其他设备 或使用示波器测量系统时钟频率,非常方便调试。

6. 时钟安全系统 (CSS) (Water Quality Monitor)

-

角色:一个安全卫士。

-

功能 :如果使能了HSE,CSS会监视HSE时钟是否失效。一旦检测到HSE失败(比如晶振损坏),它会自动将系统时钟切换到HSI,并产生一个中断,让程序有机会进行错误处理,防止系统死机。这是高可靠性应用的关键功能。