简介:PCI是一种旨在提升计算机外设交互速度的局部总线标准。本工程涉及从设计到测试的全流程,包括硬件组件、接口协议和信号传输。设计工程师需深入了解PCI的物理层、数据链路层和事务层,处理硬件设计图和驱动程序代码,并确保兼容性和扩展性。学习者通过分析图纸和代码,能够掌握PCI技术的各个方面。

1. PCI局部总线标准概述

PCI(Peripheral Component Interconnect,外围组件互连)局部总线标准是由PCI Special Interest Group(PCISIG)组织制定的一系列规范,它允许不同的外围设备与计算机系统的中央处理器(CPU)直接通信。自1992年首次推出以来,PCI已经发展成为计算机硬件架构中不可或缺的组成部分,尤其是在桌面电脑和服务器领域。

PCI标准的发展历程

在个人计算机和服务器领域,PCI标准经历了多个版本的演进,其中包括32位的PCI 2.0、64位的PCI 2.1以及后来的PCI-X。每一代标准的更新都伴随着总线宽度和时钟频率的提升,以此来满足不断增长的数据传输需求。

PCI的特点与优势

PCI局部总线标准的主要特点包括其总线无关性、即插即用(Plug and Play)特性以及统一的配置空间。这些特点极大地简化了硬件扩展设备的安装过程,并增强了系统的可靠性和扩展性。此外,PCI总线支持多总线主控器,允许多个组件同时进行数据传输,从而有效提高了数据处理效率。

PCI的应用范围

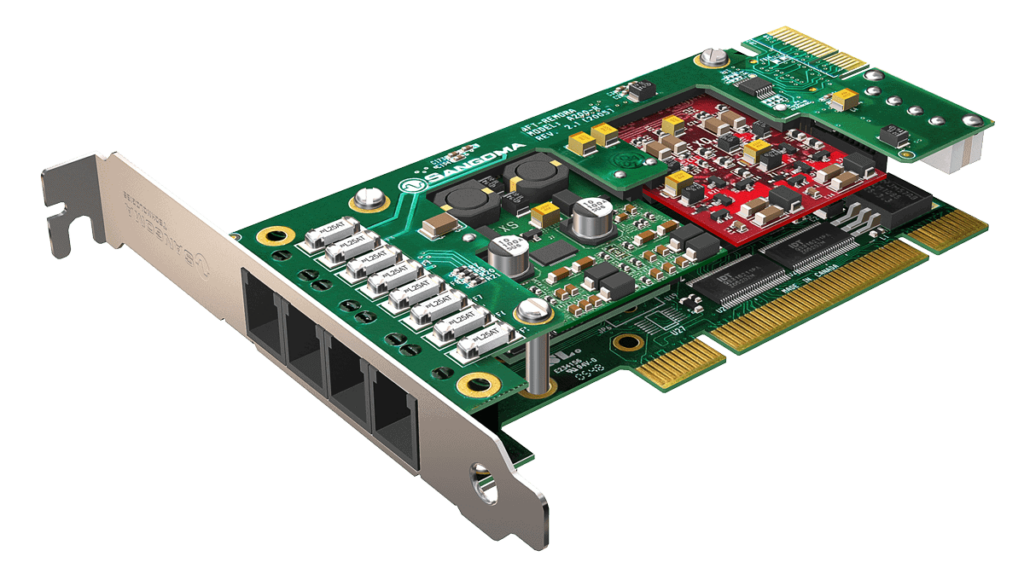

PCI技术被广泛应用于各种硬件设备中,例如显卡、声卡、网络适配器、SCSI控制器、RAID卡和多串口卡等。随着PCI Express(PCIe)技术的出现,PCI标准的某些应用领域开始逐渐被后者所取代,但PCI标准在一些特定场合和遗留系统中仍然具有其不可替代的作用。

2. PCI硬件工程设计流程

在IT行业中,硬件设计是一个复杂但至关重要的过程。PCI(Peripheral Component Interconnect)作为一种局部总线技术,其硬件设计流程自然也不例外。本章节将深入探讨PCI硬件设计的细节,涵盖从准备工作到设计实施的每一个步骤。

2.1 设计前的准备工作

在深入设计的细节之前,有两件关键的准备工作必须完成:市场调研与需求分析,以及硬件平台的选择与确定。

2.1.1 市场调研与需求分析

首先,深入的市场调研是设计流程中的基础。团队需要对目标市场进行全面的分析,了解当前市场中PCI相关产品的竞争状态、目标用户群体以及潜在的市场需求。调研可以通过多种方式进行,例如,发放问卷、竞品分析和用户访谈等。

参数说明:

-

竞品分析的范围:需要包括主要的竞争对手产品特点、定价策略、市场占有率等。

-

用户访谈的目标群体:应当覆盖不同行业、不同经验级别的用户,以获得更全面的需求信息。

进行市场调研的目的在于确定设计的方向和目标,制定符合市场需求的产品规格。例如,如果是为高性能计算设计PCI硬件,则可能需要更高的数据传输速率和更大的带宽。

2.1.2 硬件平台的选择与确定

在市场调研和需求分析的基础上,硬件工程师接下来的任务是选择合适的硬件平台。选择硬件平台需要考虑多个因素,包括但不限于性能要求、成本预算、功耗限制以及扩展性需求。

参数说明:

-

性能要求:需针对预期的数据吞吐量和处理能力来选择CPU、内存和存储设备。

-

成本预算:决定了设计的上限,并影响到组件和材料的选择。

-

功耗限制:与设备的供电需求和散热设计直接相关。

-

扩展性需求:考虑未来技术升级和功能扩展的可能。

例如,对于要求高速数据处理能力的应用,选择具有高速PCI插槽的主板和高速处理器是十分必要的。硬件平台的选择对后续的设计流程有着决定性的影响。

2.2 PCI硬件设计的具体步骤

在完成准备工作之后,硬件设计可以进入具体实施阶段,包括设计方案的制定与评估、硬件组件的选择与采购以及设计过程中的文档编制。

2.2.1 设计方案的制定与评估

设计方案的制定是整个硬件设计流程的核心。它需要综合考虑技术实现的可行性、成本效益比以及用户需求等因素。工程师需拟定多个设计方案,并对它们进行全面评估。

参数说明:

-

技术实现的可行性:分析各种设计方案的技术难度和实现复杂度。

-

成本效益比:对成本和性能进行估算,选取性价比最高的方案。

在评估过程中,可以使用决策矩阵法,通过打分系统来量化比较不同设计方案在各方面的表现。这样可以客观地选出最适合的方案。

2.2.2 硬件组件的选择与采购

一旦设计方案确定,接下来就是选择并采购相应的硬件组件。这包括主芯片、存储器、接口芯片和其他相关组件。选择组件时,需确保它们的兼容性和性能满足设计方案的要求。

参数说明:

-

兼容性:组件间的接口和协议需相互匹配。

-

性能:组件应达到设计所要求的性能指标。

为了保证采购的硬件组件符合设计标准,工程师应进行详尽的测试。此外,考虑采购成本、供应商的可靠性以及交货时间等因素也是必要的。

2.2.3 设计过程中的文档编制

硬件设计过程中,文档编制是一个经常被忽视但又极为重要的环节。良好的文档可以记录设计的每个细节,便于后期的维护和升级。

参数说明:

- 文档应包含设计的详细流程、组件规格说明、电路图和测试报告等。

在设计过程中,文档的编制应与设计活动同步进行,及时更新和维护。文档可以采取多种形式,如纸质记录、电子文档和在线协作平台等。

以上是第二章的内容概述,详细的设计流程和要点将在后续的章节中逐一展开,并配以相关的图表和代码示例,以便于理解。

3. PCI规范的深入理解

3.1 PCI规范的技术细节

3.1.1 总线操作与数据传输机制

PCI总线在数据传输方面采用了一系列机制以确保数据的高效准确传输。在总线操作中,PCI协议采用的是一种多主控制的总线仲裁机制,允许多个设备同时请求总线的控制权。当数据传输需求产生时,请求优先级最高的设备将获得总线控制权,并执行数据传输操作。此外,PCI协议通过使用地址和数据的分时复用技术,仅用一组信号线传输地址信息和数据信息,这种设计极大地减少了所需信号线的数量,同时优化了数据传输的效率。

PCI总线在数据传输时,采用突发传输模式,这种模式下,一旦确定了传输的起始地址,后续的数据可以连续传输,无需每次都重新指明地址。突发模式可以大幅度提升数据传输速率,尤其是在传输大量连续数据时效果尤为明显。

在数据传输中,还必须考虑到数据的对齐问题。PCI总线要求32位数据线上的数据必须按4字节对齐,64位数据线上的数据必须按8字节对齐,这样可以保证数据传输的快速与一致。任何不按对齐规则进行的传输都可能导致总线效率的降低或者系统错误。

3.1.2 中断和配置空间的管理

PCI设备通过中断机制与系统处理器进行通信。PCI规范定义了两种中断模式:INTx#和MSI(Message Signaled Interrupts)。INTx#是最传统的中断方式,使用特定的中断线发送中断信号,而MSI则通过写入特定的内存地址来通知中断,这种方法可以更好地适应多处理器系统和减轻中断控制器的负担。

PCI设备的配置空间是一组256字节的寄存器,用于设备的识别和初始化。配置空间的前64字节是标准化的,包含了设备制造商ID、设备ID、版本号、修订ID、类代码和子类代码等信息。通过这些信息,操作系统可以识别设备,并加载正确的驱动程序。剩下的192字节是可选的,用于设备特定的配置信息。

配置空间的管理通过一系列的读写操作来完成,这些操作在物理地址空间内被映射。在启动时,操作系统会扫描PCI总线,读取配置空间信息,以识别和初始化系统中的所有PCI设备。这种初始化过程是PCI总线的重要组成部分,为设备的正常运行打下基础。

3.2 PCI规范的实现要点

3.2.1 设备驱动程序的开发标准

PCI设备驱动程序的开发遵循特定的标准和规范,这使得驱动程序可以更容易地在不同的操作系统间迁移,同时保证了与硬件的兼容性。在开发PCI驱动程序时,通常会涉及到几个核心的概念,包括总线驱动程序、设备驱动程序和功能驱动程序。

- 总线驱动程序:负责总线的枚举和PCI设备的发现过程。

- 设备驱动程序:负责处理与特定PCI设备相关的操作。

- 功能驱动程序:负责设备的具体功能实现。

设备驱动程序的开发通常需要使用特定的开发包(SDK)或软件开发套件,这些开发包内含API(应用程序接口)供开发者调用,以便于与硬件进行交互。驱动程序开发者需要熟悉Windows Driver Kit (WDK)、Linux内核API或其他平台相关的开发工具。

c

// 示例代码:PCI设备驱动程序中的初始化函数

void InitializePciDevice() {

// 枚举PCI总线和设备

PciEnumerateDevices();

// 设置中断处理函数

PciSetInterruptHandler(MyInterruptHandler);

// 读取设备配置空间

PciReadConfigSpace(&config);

// 映射设备内存到用户空间

void* deviceMemory = PciMapDeviceMemory();

// 其他初始化操作...

}在上述代码示例中,我们能够看到初始化PCI设备的一些基本步骤,包括设备枚举、中断处理函数的设置、配置空间的读取以及设备内存的映射。

3.2.2 性能优化与兼容性测试

为了实现最佳性能并确保硬件的兼容性,PCI设备的驱动程序和固件需要经过彻底的优化和测试。性能优化包括但不限于:

- 减少中断响应时间。

- 优化数据缓存和预取策略。

- 使用DMA(直接内存访问)提升数据传输效率。

- 精确控制PCI设备的电源管理。

兼容性测试则涉及到跨平台和跨系统的测试,确保设备在不同版本的操作系统、不同硬件配置以及不同的软件环境中均能正常工作。这通常会使用自动化测试框架,如Windows的Driver Verifier工具和Linux下的LTP(Linux Test Project)。

markdown

| 测试类别 | 测试项目 | 说明 |

| --------------- | ----------------------------- | -------------------------------------------- |

| 功能性测试 | 设备枚举与配置 | 验证系统能否识别并正确配置PCI设备 |

| 性能测试 | 数据传输速率 | 通过基准测试,检测数据传输的最大吞吐量 |

| 兼容性测试 | 操作系统兼容性 | 确认设备在不同版本的Windows/Linux系统中工作正常 |

| 稳定性测试 | 连续运行测试 | 长时间运行设备以检测潜在的稳定性问题 |通过进行详尽的性能优化和兼容性测试,开发团队能够识别并解决驱动程序中的潜在问题,进一步提升系统整体的性能和稳定性。

4. 硬件组件与接口协议

4.1 硬件组件的作用与功能

4.1.1 PCI插槽与适配器的交互原理

PCI插槽为PCI设备提供了与计算机主板之间互连的物理接口。它是位于主板上的一组插槽,其设计允许各种适配器卡插入,从而实现特定的扩展功能。一个典型的PCI适配器卡可能包括网络接口卡(NIC),声卡,显卡,SCSI卡等等。适配器卡通过插槽与主板连接,进而接入到PCI总线中。

适配器卡与PCI插槽的交互涉及以下几个关键技术点:

-

电气连接 :适配器卡与PCI插槽的物理接触确保了电气连接的稳定性。金手指部分的引脚不仅传输数据,还提供电源和地线连接。

-

初始化 :计算机启动时,PCI总线上的适配器卡会被识别并初始化。BIOS或UEFI固件会执行一系列的PCI枚举过程,来识别所有连接的设备并分配资源。

-

数据交换 :适配器卡与主板间的数据交换通过PCI总线协议进行,利用地址线、数据线、控制线等实现数据的传输。

-

中断与DMA :适配器卡可以配置为使用特定的中断请求(IRQ)和直接内存访问(DMA)通道,来提高数据传输效率并减少处理器的负载。

在设计过程中,需要确保适配器卡的电气特性和机械尺寸与所选择的插槽完全匹配。同时,设计者也需留意信号的完整性和接口的耐久性。

4.1.2 电源管理与信号完整性要求

在现代计算机系统中,电源管理显得尤为重要,因为电源效率直接影响到设备的能耗表现和热管理。对于PCI硬件组件,电源管理涉及到为适配器卡提供稳定且准确的电压和电流。

-

电压要求 :PCI设备在正常工作模式下通常需要3.3V或5V电源,设计时必须确保电源提供的电压在规定范围内,并对电压变化有一定的容错能力。

-

电流供应 :适配器卡的最大电流需求必须在电源的供应能力范围内。另外,热设计功耗(TDP)也需考虑,确保系统散热设计能够应对最坏情况下的热量产生。

-

信号完整性 :PCI信号需要保持高速传输下的完整性和可靠性。为了达到这一点,需要对信号线进行阻抗匹配设计,减少信号反射,降低噪声干扰,并通过使用去耦电容等措施来稳定电源。

-

电磁兼容性(EMC) :电子设备在工作时不可避免地会产生电磁干扰(EMI),因此在设计阶段要充分考虑EMC标准,确保PCI硬件不会干扰其他电子设备的正常工作,同时自身也能在复杂电磁环境中稳定运行。

以上电源管理与信号完整性的要求需要硬件工程师仔细规划,并通过多次的原型测试和迭代,才能确保硬件组件能够满足PCI规范的技术要求。

4.2 接口协议的技术实现

4.2.1 接口协议的电气特性与信号要求

PCI接口协议定义了电气特性和信号传输的规则,这对于保证硬件组件能够正确无误地进行通信至关重要。PCI的电气规范包括了对信号线的最大电压摆幅、上拉和下拉电阻值、信号上升/下降时间、以及信号间的干扰容忍度等电气特性的规定。

信号线的电气特性:

-

电压摆幅 :PCI信号在逻辑"0"和逻辑"1"之间变化时允许的最大电压范围。

-

阻抗匹配 :信号线和接收端的输入阻抗需要匹配,以最小化信号反射。

-

时序要求 :信号的时序要求非常严格,比如最小的时钟周期、建立时间和保持时间等。

信号要求方面,PCI总线采用并行传输数据的方式,保证了数据传输的高速度。但是,并行传输同样也带来了信号间串扰和同步问题。因此,在电气设计上必须使用高质量的走线、终端匹配、差分信号等技术来确保信号传输的质量。

4.2.2 数据封装与传输控制机制

PCI总线的数据封装和传输控制机制是其核心设计之一,涉及了如何有效地将数据打包,并在多个设备之间进行高速传输。

数据封装在PCI中主要包含地址、数据、控制和状态信息等。传输前,数据被封装到符合PCI协议的数据包中。PCI使用事务(Transaction)来表示一个数据交换的全部过程,包括地址阶段、数据阶段和终止阶段。

-

地址阶段 :在地址阶段,发送设备会把目标地址放到总线上,以及指明数据传输方向(读或写)。

-

数据阶段 :数据阶段是实际数据传输的阶段,数据会根据地址阶段指示的方向在总线上被传输。

-

终止阶段 :传输完成后,发送设备会释放总线,并且结束当前事务。

在传输控制方面,PCI总线使用了一套复杂的总线仲裁机制,确保多个设备可以公平地使用总线资源。总线仲裁包括了对优先级的管理、请求与授权机制等。

-

仲裁机制 :设备通过发出总线请求信号(REQ#)和接收到总线授权信号(GNT#)来进行仲裁。

-

设备选择 :系统仲裁器根据预设的优先级规则来选择下一个占用总线的设备。

-

事务完成 :一旦事务被授权,请求设备即可控制总线,直到事务完成。

总体上,接口协议的技术实现需要硬件设计师对PCI的电气特性、信号要求、数据封装和传输控制机制有深入的理解,并且能够把这些技术细节融入到硬件设计中,以确保最终的产品能够与现有的计算机系统无缝兼容,同时具备高性能和高可靠性。

5. 信号传输与电气特性

信号传输和电气特性是PCI总线设计的核心组成部分,它们直接关系到系统能否稳定高效地工作。本章将深入探讨信号传输的基本原理、电气特性规范要求以及它们如何影响整体设计。

5.1 信号传输的基本原理

在PCI总线中,信号传输涉及到的是高速数字信号在导线上的传播。这个过程会受到多种因素的影响,比如线路阻抗、信号反射、串扰以及电磁干扰等。

5.1.1 高速数字信号的传播问题

随着技术的进步,PCI总线速度已从早期的33MHz提升至如今的数GHz,信号传输的速度也相应提高。高速信号在传输线上传播时会出现诸多问题:

- 信号延迟: 由于导线具有电阻和电感,信号通过时会有时间延迟。

- 信号衰减: 高频信号通过导线时,信号幅度会随着距离的增加而减小。

- 信号反射: 当信号遇到阻抗不匹配点时,部分信号会反射回源端,导致波形失真。

- 串扰: 由于电磁场的相互作用,信号之间的相互影响,造成噪声。

5.1.2 信号完整性与电磁兼容性分析

信号完整性 关注的是信号在传输过程中是否保持了其原始特性,这涉及到信号的时序,完整性以及信号质量的评估。

- 时序分析: 检查信号的上升时间、下降时间以及信号到达的时间是否在规定的范围内。

- 完整性分析: 确保信号在传输过程中没有过分的失真。

- 电磁兼容性(EMC): 考虑产品在电磁环境中能否正常工作且不对该环境中的其它设备产生干扰。这需要设计时对PCB布局、接地以及屏蔽进行精心设计。

5.2 电气特性的规范要求

电气特性是PCI总线中规定的一系列参数,包括电压、电流、阻抗、时序等,它们定义了信号如何在硬件组件之间传输。

5.2.1 PCI总线的电气规格标准

PCI总线电气规格标准定义了信号线的电压水平、负载能力、信号上升和下降时间等。例如,PCI标准定义了3.3V和5V两种信号电压版本,每种版本有其对应的电气特性要求。

- 电压规格: PCI总线的电压规格分为3.3V和5V,这影响了信号电平的定义。

- 时序规格: 规定了信号的最大传输延时和信号在不同状态下的持续时间。

- 负载能力: 对信号线上允许的最大负载(即电容性负载和电阻性负载)有明确限制。

5.2.2 热设计功耗与供电要求

PCI设备的热设计功耗(TDP)和供电要求是保证硬件稳定运行的重要条件。

- 热设计功耗: 是指设备在典型工作条件下长时间运行所需的平均功率,这对散热系统设计有直接影响。

- 供电要求: 包括电压水平、电流容量以及供电的稳定性,确保设备可以得到稳定可靠的电力供应。

电气特性的精确控制是确保PCI设备正常工作的关键。下一节,我们将详细分析如何通过PCB设计来解决信号完整性问题,以及如何解读信号波形图以进一步优化设计。

6. PCB设计、封装图和信号波形图的解读

6.1 PCB设计的关键要素

6.1.1 多层板设计与布线策略

多层板设计是现代电子设备中的关键组成部分,尤其是对于高速数据传输和高密度集成的设备。在设计多层板时,设计师需要考虑信号层、电源层、地层以及它们之间的分布和连接方式。多层板的主要目的是提高信号完整性,减少信号干扰,并且提供更好的电源管理。

在布线策略方面,关键在于最小化信号走线长度,并采用适当的线宽来匹配信号的特性阻抗。高速信号传输时,应避免90度折角走线,应采用圆滑的45度走线或者弧线走线。同时,应合理布局电源和地平面,以形成良好的回流路径,并减少电磁干扰。

6.1.2 信号完整性和高速设计技术

信号完整性(Signal Integrity, SI)关注的是信号在传输过程中保持其质量和准确性的能力。高速设计技术包括阻抗控制、差分信号设计、串扰最小化以及定时问题的管理。设计者需对高速信号进行适当的去耦、终结,确保信号在传输过程中不发生失真。

为了保证信号完整性,设计师通常需要运用一些专业工具来模拟和分析信号行为,如使用信号完整性分析软件。在布局布线阶段,应遵循以下原则:

- 确保高速信号线的等长,特别是在时钟线和差分线对中。

- 尽量在信号层和地层之间保持一致性,以减少信号反射。

- 使用V形缝技术来控制高速信号走线的特性阻抗。

6.2 封装图与信号波形图的分析

6.2.1 封装图的解读与应用

封装图是指电子元件的物理包装以及引脚分布图。在PCB设计中,了解封装图是非常重要的,因为它直接关系到元件是否能正确地放置并连接在PCB板上。封装图通常包括了元件的外形尺寸、焊盘尺寸、引脚排列等信息。

解读封装图时,应该注意以下方面:

- 确认封装的类型,如QFN、BGA或者SOP等。

- 了解封装的尺寸和引脚间距,以避免在布板时发生错误。

- 对于具有复杂引脚布局的封装,如BGA,需要特别注意信号的分配和布线策略。

封装图可以应用在以下几个方面:

- 用于选择和采购适合的电子元件。

- 在布线阶段作为参考,确保元件能够正确放置并连接。

- 对于需要手动焊接或表面贴装的组件,封装图是必要的工艺指导。

6.2.2 信号波形图的测试与分析方法

信号波形图是指信号在时间轴上随时间变化的图形表示。波形图通常用于调试和测试电路,以确保信号的准确性和稳定性。波形图的测试和分析涉及到捕捉信号、解读波形并据此优化设计。

测试信号波形图可以采用示波器等设备,分析时要关注波形的幅度、上升沿和下降沿时间、周期、占空比等参数。例如,高速数字信号在传输中可能会出现过度的振铃(ringing)、过冲(overshoot)或下冲(undershoot),这些都是波形图分析中需要特别注意的信号失真现象。

信号波形图分析方法包括:

- 使用频谱分析仪来观察信号的频率内容,判断是否存在不必要的噪声或干扰。

- 通过逻辑分析仪来检查数字信号的逻辑电平,并确保它们满足时序要求。

- 使用信号源和探针组合进行信号注入,观察在特定条件下信号的响应。

分析信号波形图时,可以使用下面的代码块进行逻辑分析。这里以一个模拟信号波形的数据分析为例,展示如何在Python中使用matplotlib进行波形图的绘制和分析。

python

import matplotlib.pyplot as plt

import numpy as np

# 假设数据是通过示波器捕获的信号波形

time = np.linspace(0, 1, 1000) # 时间轴,从0到1秒

signal = np.sin(2 * np.pi * 10 * time) # 生成10Hz的正弦波形信号

# 绘制信号波形图

plt.figure(figsize=(10, 5))

plt.plot(time, signal)

plt.title('Signal Waveform')

plt.xlabel('Time [s]')

plt.ylabel('Amplitude')

plt.grid(True)

plt.show()上述代码使用 matplotlib 库来绘制一个正弦波形图,通过 plot 函数将时间和信号数据绘制在图表中。通过这种方式,我们可以将实际测量得到的信号波形数据导入并进行视觉化分析,进而在设计PCB时做出相应的调整。

7. 驱动程序与固件代码编写

驱动程序与固件代码是确保PCI设备正常工作和高效运行的关键组件。在这部分内容中,我们将深入了解驱动程序的设计与实现过程,以及固件代码编写的重要性及其相关注意事项。

7.1 驱动程序的设计与实现

驱动程序(Driver)是操作系统与硬件设备之间的一个桥梁,它负责将操作系统的调用转换为对硬件设备的具体操作。在PCI技术中,驱动程序的编写遵循特定的架构和API(Application Programming Interface)。

7.1.1 驱动架构与API的使用

编写PCI设备驱动程序时,通常需要使用特定的驱动架构,例如在Linux操作系统中,常见的驱动架构是WDM(Windows Driver Model)或Linux内核模块。开发者需要利用操作系统提供的API来操作硬件,如使用 io_read 和 io_write 函数来读写设备的I/O空间。

c

#include <linux/ioport.h>

// 申请I/O端口资源

unsigned long base_addr = 0x300; // 假设设备基地址为0x300

if (!request_region(base_addr, 0x20, "MyPCIDevice")) {

printk(KERN_ERR "Failed to acquire I/O region\n");

return -EBUSY;

}

// 读取设备的I/O端口

unsigned char data = inb(base_addr);

// 释放I/O端口资源

release_region(base_addr, 0x20);7.1.2 错误处理与性能调试

驱动程序在开发过程中必须重视错误处理机制,确保设备在遇到异常情况时能够安全地进行恢复。性能调试则涉及到优化设备与操作系统的交互,减少中断延迟和提升数据传输效率。

c

void handle_error(struct my_pci_device *device) {

// 处理设备错误情况

// ...

// 日志记录错误信息

dev_err(&device->dev, "Device error occurred\n");

}

// 性能调试时可能需要的代码片段

unsigned long start_time, end_time;

unsigned long elapsed;

start_time = jiffies; // 获取开始时间

// 进行设备操作...

end_time = jiffies; // 获取结束时间

elapsed = end_time - start_time;

// 分析操作耗时,进行性能优化

printk(KERN_DEBUG "Operation took %lu ms\n", elapsed);7.2 固件代码的重要性与编写

固件代码(Firmware)通常是指嵌入到硬件设备中的软件,比如一个嵌入式控制器的程序。固件代码的编写对设备的稳定性和安全性有着决定性的影响。

7.2.1 固件代码的作用与开发环境配置

固件代码的编写需要使用适合的开发环境,例如使用Keil MDK进行ARM处理器的固件开发,或者使用GCC编译器进行x86架构的固件编程。固件代码的作用包括初始化硬件设备、设置设备的工作模式、提供设备升级和维护功能等。

7.2.2 代码编写中的安全与稳定性考虑

在编写固件代码时,安全和稳定性是最重要的两个考虑因素。需要确保固件能够处理各种异常情况,如内存溢出、非法访问、硬件故障等,并且在出现异常时能够安全地引导设备进入安全模式或执行恢复操作。

c

// 代码片段展示固件中的异常处理

void firmware_init() {

// 初始化硬件...

if (is_hardware_error()) {

// 处理硬件错误

firmware_error_recovery();

}

}

// 硬件错误恢复函数

void firmware_error_recovery() {

// 执行恢复操作...

// ...

}在编写固件代码时,开发者还需要考虑代码的可维护性和可测试性,以确保固件在长期使用过程中能够持续提供稳定的支持。通过模块化编程、版本控制和持续集成等软件工程实践,可以有效地提高固件代码的质量和可靠性。

简介:PCI是一种旨在提升计算机外设交互速度的局部总线标准。本工程涉及从设计到测试的全流程,包括硬件组件、接口协议和信号传输。设计工程师需深入了解PCI的物理层、数据链路层和事务层,处理硬件设计图和驱动程序代码,并确保兼容性和扩展性。学习者通过分析图纸和代码,能够掌握PCI技术的各个方面。