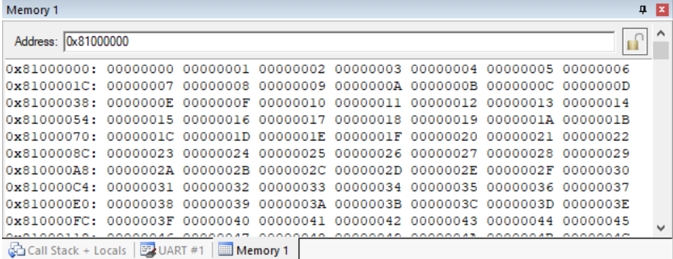

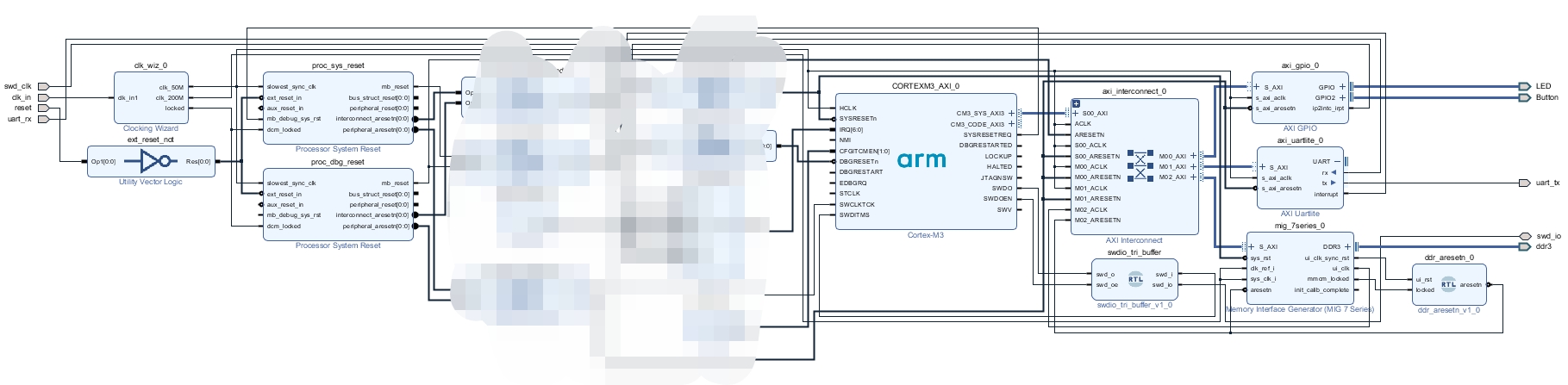

基于FPGA的Cortex-M3软核DDR读写工程 实现基于FPGA的Cortex-M3软核基本SOC,系统外设包括GPIO和UART串口,且实现对DDR的读写。 开发基于vivado2019.2和vitis,理论上可适用于任何版本的vivado,软件工程基于Keil设计,并且附详细开发文档,能够快速完成工程的移植。 在该工程基础上可进一步开发更多的功能。 !

最近在搞一个超有意思的项目------基于FPGA的Cortex-M3软核DDR读写工程,今天来和大家分享一下其中的奥秘。

一、工程概览

这个工程旨在实现基于FPGA的Cortex-M3软核基本SOC 。这里面涉及到的系统外设包括GPIO(通用输入输出端口)和UART串口,而且还得实现对DDR的读写。这就好比搭建一个小的数字王国,各个组件各司其职。

二、开发工具与环境

开发基于vivado2019.2和vitis 。虽然说是基于2019.2版本,但理论上它能适用于任何版本的vivado 。软件工程这边则是基于Keil设计。这种工具组合可以说是优势互补,vivado和vitis负责硬件描述和综合等底层工作,Keil则专注于软件代码的开发与调试。

三、代码示例与分析

先来说说GPIO部分代码示例(这里以简单的GPIO初始化代码为例,假设是C语言代码):

c

#include "gpio.h"

void gpio_init(void) {

// 设置GPIO方向为输出

GPIO_DIR = 0xFFFF;

// 初始化GPIO输出电平为低

GPIO_DATA = 0x0000;

}分析:在这段代码里,首先通过 GPIO*DIR = 0xFFFF;*将所有GPIO引脚设置为输出方向。0xFFFF 是十六进制表示,意味着每一位对应一个GPIO引脚,全为1即全设置为输出。接着 GPIO DATA = 0x0000; 将输出电平初始化为低电平,这里是对GPIO初始状态的一个设定,方便后续的操作。

再看看UART串口相关代码(同样是C语言):

c

#include "uart.h"

void uart_init(void) {

// 设置波特率

UART_BAUD = 9600;

// 使能UART发送和接收

UART_CONTROL = UART_TX_EN | UART_RX_EN;

}分析:UART*BAUD = 9600;*设定了串口通信的波特率为9600,这是一个常见的串口通信速率,决定了数据传输的快慢。UART CONTROL = UARTTX EN | UARTRXEN; 则是通过按位或操作,同时使能了UART的发送和接收功能,这样串口就能正常收发数据啦。

基于FPGA的Cortex-M3软核DDR读写工程 实现基于FPGA的Cortex-M3软核基本SOC,系统外设包括GPIO和UART串口,且实现对DDR的读写。 开发基于vivado2019.2和vitis,理论上可适用于任何版本的vivado,软件工程基于Keil设计,并且附详细开发文档,能够快速完成工程的移植。 在该工程基础上可进一步开发更多的功能。 !

对于DDR读写部分,代码相对复杂一些,这里简单示意一下(以伪代码为例):

text

// 初始化DDR控制器

ddr_controller_init();

// 定义要写入的数据

data_to_write = 0x12345678;

// 写入DDR指定地址

ddr_write(ddr_address, data_to_write);

// 从DDR指定地址读取数据

read_data = ddr_read(ddr_address); 分析:首先通过 ddrcontrollerinit(); 对DDR控制器进行初始化,这是后续读写操作的基础。然后定义了要写入的数据 datatowrite 。ddrwrite(ddr address, datatowrite); 这个操作就是将数据写入到DDR的指定地址 ddraddress*。读取操作 read* data = ddrread(ddraddress); 则是从相同的地址把数据读出来。

四、开发文档与移植便利性

工程还附带详细开发文档,这可太重要了。文档里从环境搭建到代码说明,再到工程的移植步骤,都写得清清楚楚。有了这份文档,就能够快速完成工程的移植。对于不同的项目需求,只要按照文档里的步骤,修改一些参数或者配置,就能把这个工程移植到新的环境中,简直不要太方便。

五、未来拓展

在这个工程基础上,还可以进一步开发更多的功能。比如添加更多类型的外设,像SPI接口、I2C接口等,或者优化DDR读写算法,提高数据传输效率。这就像给建好的数字王国不断添加新的建筑,让它变得更加丰富多彩。

总之,这个基于FPGA的Cortex-M3软核DDR读写工程有着很大的潜力和趣味性,无论是对于学习FPGA开发还是实际项目应用,都有着很高的价值。希望大家也能从中找到自己感兴趣的点,一起探索更多的可能性。