文章目录

-

- [GIC 中断分类](#GIC 中断分类)

-

- [SGI(Software Generated Interrupts)](#SGI(Software Generated Interrupts))

- [PPI(Per-Processor Interrupts)](#PPI(Per-Processor Interrupts))

- [SPI(Shared Peripheral Interrupts)](#SPI(Shared Peripheral Interrupts))

- 中断检测流程

-

- 物理中断生命周期

- [SPI 中断检测流程](#SPI 中断检测流程)

- [PPI 和SGI中断检测流程](#PPI 和SGI中断检测流程)

- LPI中断检测流程:

- 小结

GIC 中断分类

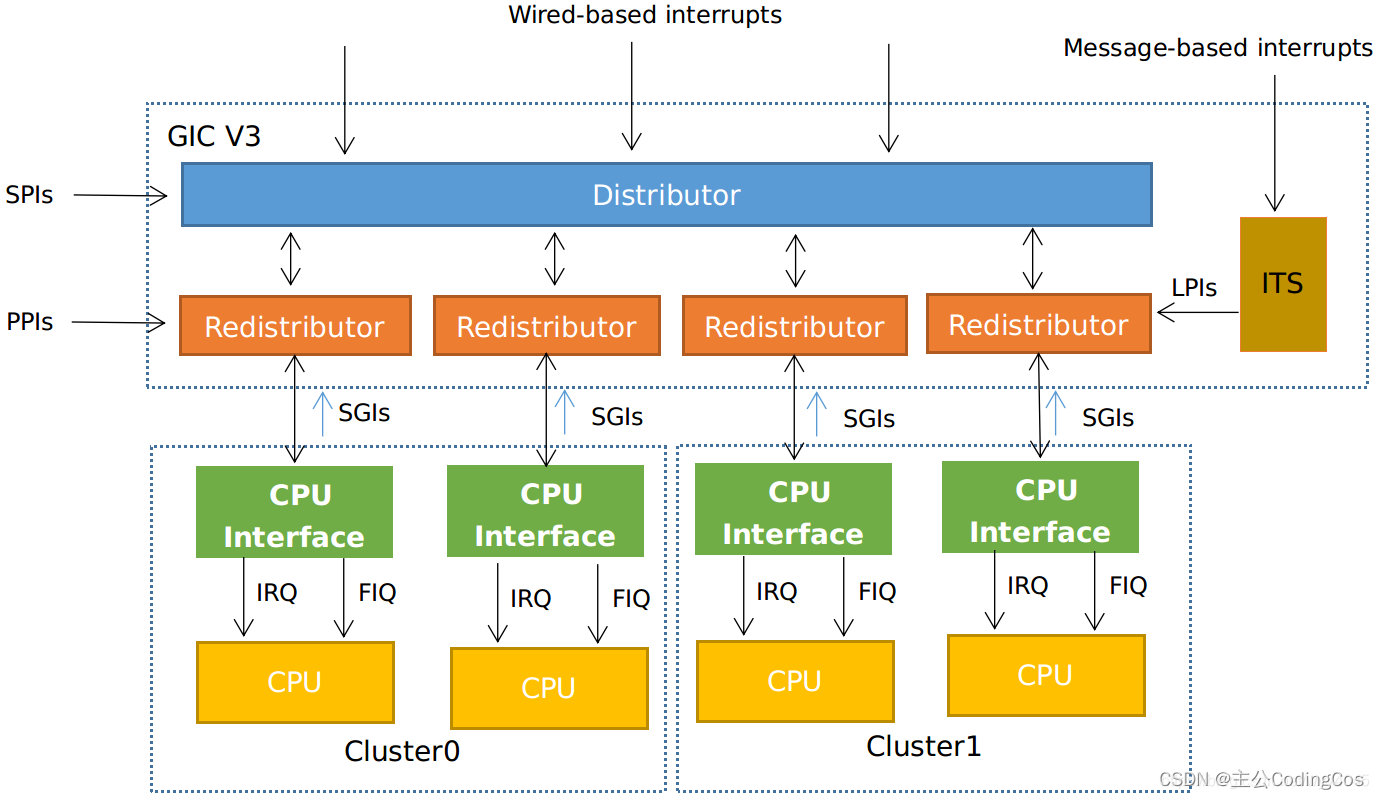

ARMv9架构继续支持ARMv8引入的中断管理机制,包括SPI(共享外设中断)、PPI(每处理器中断)和SGI(软件生成的中断)。这些中断类型为不同的应用场景提供了灵活性和高效的中断处理方式。此外,GIC V3中断控制器的组成部分包括:distributor,Redistributor,cpu interface,ITS。

GIC V3中断控制器和处理器核心之间的关系图如下:

图 1-1

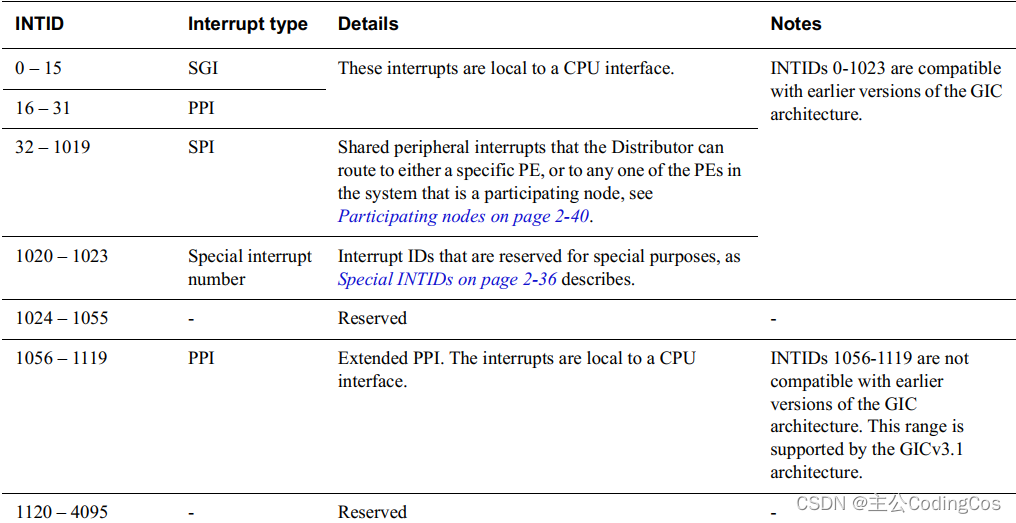

SGI(Software Generated Interrupts)

- 定义 :SGIs是从

0到15的中断编号,为软件生成的中断,主要用于处理器间的通信(IPC)。ARM架构允许软件触发这些中断,以便一个处理器可以向一个或多个处理器发送信号。 - 应用举例 :

- 操作系统调度:操作系统可以使用SGI来实现任务或线程的调度。例如,当一个处理器上的任务需要迁移到另一个处理器时,OS可以通过SGI来触发目标处理器的调度代码。

- 同步机制:在多核处理器系统中,SGI可用于实现锁或屏障等同步机制。例如,当所有处理器都必须在继续之前达到某个执行点时,可以使用SGI来通知所有处理器。

PPI(Per-Processor Interrupts)

- 定义 :PPIs是从

16到31的中断编号,这类中断是每个处理器专有的。这意味着每个处理器都有自己的一组 PPI ,而这组PPI仅对该处理器可见。 - 应用举例 :

- 定时器中断:系统定时器会为每个处理器生成定时器中断,这类中断作为PPI处理,确保每个处理器可以基于自己的定时需求独立触发和处理定时器中断。

- IPI(Inter-Processor Interrupts):当一个处理器需要与另一个处理器通信时(例如,通知它处理一些任务或数据),可以通过发送IPI来实现,IPI是一种特殊的PPI。

SPI(Shared Peripheral Interrupts)

- 定义 :SPIs是从

32开始的中断编号,用于系统中的外设共享中断。这意味着SPI可以被系统中的任何处理器接收。 - 应用举例 :

- 网络控制器中断:当网络控制器接收到一个新的网络包并且需要处理器进行处理时,会触发一个SPI来通知处理器。

- 磁盘I/O中断:在磁盘操作完成时,磁盘控制器会通过SPI通知处理器数据已经准备好。

中断检测流程

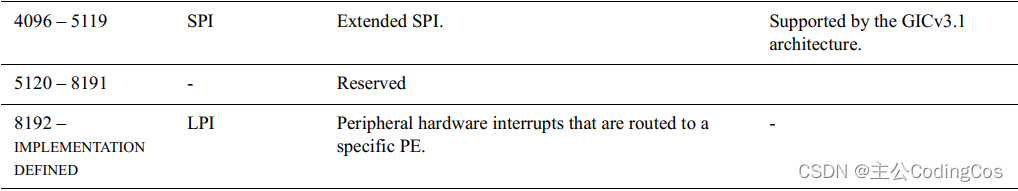

GICv3中断号分配对于每个中断,从产生到处理再到结束,是有一个完整的生命周期的。

图 1-2

物理中断生命周期

generate:外设或软件发起一个中断;distribute:中断经过分组,优先级仲裁等,发送给对应的 CPU interface;deliver:CPU interface将中断发送给 core;activate:当CPU core 开始响应中断,GIC将最高激活优先级的中断设置为激活;priority drop: core发信号给GIC,通知最高优先级中断,GIC可以重置优先级;deactivation:清除中断.

SPI 中断检测流程

- 外设发起SPI中断,GIC检测到这个中断,并标记为 Pending状态

- Distributor对所有处于Pending状态的中断确定目标CPU

- 对每个CPU,Distributor会从众多Pending状态的中断中,选择优先级高的发送到对应的Redistributor

- Redistributor将中断发送到目标CPU的CPU Interface上

- CPU Interface将满足要求的中断发送给CPU

- CPU进入中断异常后,内核中断处理程序读取

GICC_IAR寄存器来响应该中断,寄存器返回硬件中断号 - CPU处理完中断服务后,通过写

GICC_EOIR寄存器,来给GIC发送一个EOI完成信号

PPI 和SGI中断检测流程

- GIC检测到PPI或者SGI中断,并标记为Pending状态

- Redistributor选择优先级高的中断发送到对应的CPU Interface

- CPU Interface将满足要求的中断发送给CPU

- CPU进入中断异常后,内核中断处理程序读取

GICC_IAR寄存器来响应该中断,寄存器返回硬件中断号 - CPU处理完中断服务后,通过写

GICC_EOIR寄存器,来给GIC发送一个EOI完成信号

LPI中断检测流程:

forwarding方式,由以下寄存器实现

GICR_SERLPIR:将指定的LPI中断,设置为Pending状态GICR_INVLPIR:将指定的LPI中断,清除Pending状态。寄存器内容和GICR_SERLPIR一致GICR_INVLPIR:将缓存中,指定LPI的缓存给无效掉,使GIC重新从memory中载入LPI的配置GICR_INVALLR:将缓存中,所有LPI的缓存给无效掉,使GIC重新从memory中,载入LPI中断的配GICR_SYNCR:对Redistributor的操作是否完成

小结

- SPI 主要用于外设与处理器间的通信,是共享的,意呅着任何处理器都可以接收和处理SPI中断。

- PPI 是处理器专用的中断,用于处理每个处理器独有的事件,如定时器中断。

- SGI 用于处理器间直接的通信,支持软件触发,适合于实现快速的任务调度或同步机制。

这些不同类型的中断为ARMv9架构提供了灵活而强大的中断管理能力,支持复杂的多核处理器系统和高效的硬件资源利用。

推荐阅读 :

https://blog.csdn.net/wyy4045/article/details/104827111

https://www.sohu.com/a/771753252_121124377