USB(全称:Universal Serial Bus)是一种串口总线标准,也是一种输入输出接口的技术规范,广泛应用于个人电脑和移动设备等信息通讯产品,并扩展至摄影器材、数字电视(机顶盒)、游戏机等相关领域。模组应用时,USB接口通常作为4G、5G模组与CPU的通信和固件升级的重要接口,其性能直接影响通信数据传输的成功率。本文讲解了USB接口设计、差分阻抗控制以及固件下载的常见问题。

一、USB接口设计

1.USB概念及速率

USB是一种外部总线标准,用于规范电脑与外部设备的连接和通讯。USB各版本的速率及功率见表1。

表1 1USB版本及特点

USB 2.0物理接口采用4针脚设计(D+,D-,Vbus,GND),D+与D-是一对差分线。USB 3.0物理接口采用9针脚设计,增加了两对超高速差分信号SSTX+与SSTX-、SSRX+与SSRX-,共3对差分线。

2.一般设计原则

模组仅能作为设备(Device)工作,无法作为主机(Host)工作,不支持OTG模式。5G模组最高可支持USB 3.1 Gen2速率,其余模组最高支持USB 2.0的高速模式,均向下兼容。

在原理图设计中,建议对USB接口进行防静电保护,并预留用于滤除共模和差模干扰的元件位置。不贴实际值,仅贴0R短接即可。预留元件位置便于在测试中如果发现干扰,可以快速贴上电感电容进行调试。这是硬件设计中的一种兼容策略,有助于避免改板问题。

在PCB设计时,为保证数据传输的稳定性及可靠性,必须遵循差分线一般的设计原则:

- 根据PCB层叠关系,利用阻抗计算工具,控制差分90Ω阻抗

- 参考平面完整,不能出现跨分割

- 走线不能走90°直角,且需进行良好的包地处理

- 差分对走线等长,尽量避免过孔。如果必须使用过孔,则应在附近放置回流地过孔

- 尽量减少布线长度

- 远离边沿陡峭的信号或高开关速率器件

- USB数据线上的ESD防护器件的寄生电容不能超过22pF

- 若USB仅用于固件下载预留,不用于数据传输,设计时可放宽要求

二、USB差分阻抗控制

USB差分走线阻抗需控制90Ω,设计时需保持阻抗连续,阻抗控制方式与射频的单端50Ω类似,通过阻抗计算软件SI9000选择合适的差分阻抗模型,计算出差分走线的线宽线距,实现90Ω阻抗控制。

阻抗的不连续会导致信号发生反射和衰减、通信速率降低,控制好高速信号的走线阻抗,是布线成功的关键。

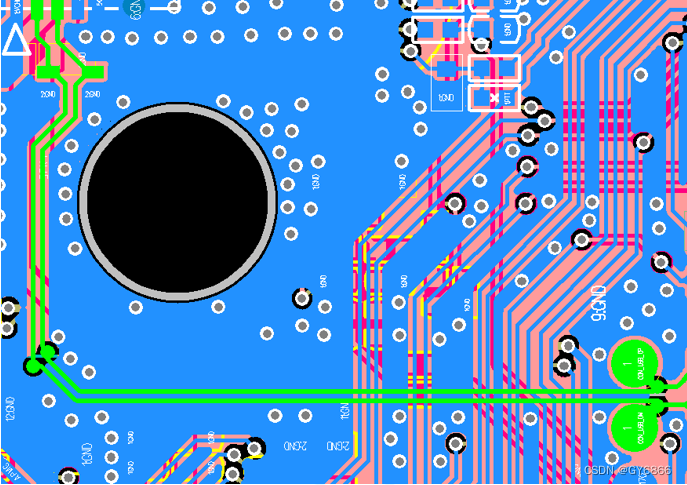

图1 USB布线示例

三、USB固件升级下载

此问题主要出现在ML307系列模组的固件升级中。由于ML307系列模组强制进入下载模式需要把BOOT引脚拉低到地,如客户前期使用其他模组未注意兼容性,会将BOOT预留上拉至VDD_EXT,从而导致固件下载失败。

1.BOOT上拉问题

问题:用户将BOOT错误上拉到VDD_EXT引脚。

解决方法:参考上述方法进行修改。

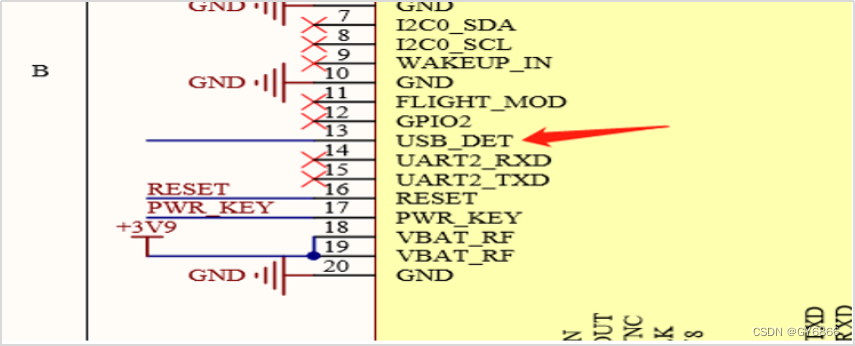

2.VBUS问题

问题:用户使用了USB功能,却没接USB_DET。

解决方法:需将USB_DET接至VBUS。

图2 VBUS设计问题

- 总结

在模组固件下载和模组调试的关键环节中,USB接口的使用频率极高。为了确保操作的便捷性和高效性,强烈建议在电路设计时明确将模组的USB接口引出,并严格遵循文档中的建议进行相关的电路设计,以确保接口的稳定性和兼容性。