随着电源类管理芯片向大功率(集成功率器件)、多功能(数模混合)方向发展,噪声干扰越来越严重,成为了一个无法忽视的新问题。对高精度的模拟部分,当敏感电路需要接受微弱信号进行计算,而诸如时钟信号、逻辑控制信号等频繁变换的信号在它旁边时,敏感电路的精度可能受到严重干扰,甚至于影响功能。数模混合设计中,数字电路与模拟电路都制作在同一衬底中,或采用重掺杂埋层加深阱进行隔离,但寄生的结电容和 BJT 晶体管以及共用电源、地等,都有可能将数字部分高频下门电路的周期性转换噪声传播到衬底。这些串入衬底的噪声影响模拟电路,形成虚假信号,干扰模拟电路正常工作。而功率器件的集成使得干扰噪声达到无法忍受的地步,版图上放置再多的常规多子、少子保护环,设置更宽的物理隔离带等等都无法有效的隔离噪声。

串扰

串扰(Cross talk)是指由于两条信号线之间耦合,信号线之间的互感和互容引发的线上噪声。容性耦合会引起不希望的耦合电流,感性耦合会引发耦合电压。这类耦合与相邻连线之间的尺寸、距离、连线材料以及相互间的介质层等因素有关。串扰带来额外的电流或电压与其本省的模拟量叠加,影响模拟部分运算精度;在数字部分,干扰信号如果超出数字门的噪声容限,导致误翻转,则会得出错误的结果。在亚微米和深亚微米集成电路制程中,金属层数不断增多,0.25μm~0.5μm BCD工艺有3到4层金属,0.18μm BCD工艺有超过5层金属布线。另外,集成电路设计越来越复杂,电路门数的剧增使得互连线更多也更长,空间越来越狭小;而工艺上为弥补线宽减小导致走线电阻的增加,将金属加工得又高又窄,侧壁耦合电容明显增加,大部分BCD工艺提供20KÅ 到30KÅ 的加厚顶层金属,甚至次顶层也可以加工为厚金属以期提高针电源类芯片的竞争力。随着线间距的减小,金属层此增多,金属间寄生电容增大,串扰的危害变得越来越大。

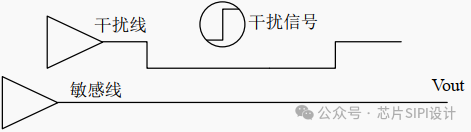

在对芯片内部信号传输建模和分析中,比较精确的模型需要对寄生电阻、电容和电感同时考虑(称为 RCL 互连模型)。在BCD工艺的实际电源管理芯片中,以CMOS 逻辑为主, CMOS电路中的驱动门电阻通常都不大,负载门是一个高阻抗的容性负载,因此在对CMOS 电路的串扰分析中,往往忽略电感耦合的噪声。下图显示了两条信号线之间的串扰现象。

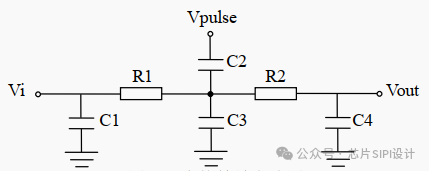

下图显示了忽略电感后的等效电路图:

由此可知,芯片中的大部分串扰是信号间的电容耦合产生的。平行信号线甚至交错的信号线之间都有寄生电容,而电容对频率越高的信号,拦截效率越低。随着频率的提升,电容耦合的能量越来越多,在足够高频率下,或许低频安全的物理交叠也会产生无法接受的串扰。有研究表明,当信号频率超过1MHz的情况下就需要关注电容耦合噪声。

对于芯片内部信号线可以大致划分为三类:噪声信号、敏感信号和普通信号。具体电源类芯片而言,噪声信号包括振荡器时钟信号、数字门产生的周期性信号或高频信号、功率管的输出信号或它的电源和地(因功率管的电源和地有大量外接电感产生的电感电流形成的纹波)等;敏感信号包括精确的电压基准源、电流镜、 高增益放大器和精确比较器的输入、模数转换器的输入、高精度电路的模拟地线、高精度的电阻网络、非常小的信号和任何类型的小电流电路等。而普通信号是指除以上两者的信号线,它们所连接的器件敏感度级别不高,较难受到影响。通常具有一定电路知识的版图工程师可以识别大部分的噪声线和敏感线,在绘制版图过程中采取正确的措施减小串扰现象。

衬底噪声

衬底噪声是由于同一芯片中的不同模块工作时产生的噪声累积并串入衬底形成。噪声通过共用衬底传播,被其它模块吸收,形成虚假信号,干扰其它模块正常工作。在数模混合芯片中,模拟部分和数字部分都是做在同一衬底上的,其分别通过各种方式对衬底注入噪声。如数字部分内大部分门电路周期性的转换,通过有源区结电容串入衬底,同样模拟部分的二极管、三极管等也会通过这种方式传播噪声;功率MOSFET导通时沟道中的碰撞电离也是一个强噪声源;电源和地通过网络中电阻和电感的耦合也会将电源电压降或地弹噪声传播到衬底。

电源电压降和地弹噪声

电源电压降是指由于电源网络存在的寄生电阻,使得供电电压在传输过程中产生损耗的情况。随着供电网络越长寄生电阻累积越多,最后加在终端器件上的供电电压差损失就越大。电源电压降落会导致终端电路的噪声容限降低,加剧时钟偏斜,电路时序发生改变,进而影响芯片的性能、功能和可靠性。当工作电压变化10%时,电路的性能约有7%~9%的退化。

电源电压降对深亚微米工艺下的高速集成电路的影响要严重得多;其工艺线宽更小,导线的单位电阻率更大,传输损耗增加;同时电源电压大幅降低,对电压损失更敏感,如0.18 um工艺数字部分供电电压通常为1.8V,而 100nm以下器件供电电压在1V左右。相对而言,电源电压降落对电源管理类芯片的影响要小。电源管理芯片大部分是模拟电路,数字电路不多,深亚微米工艺下的器件很难满足模拟电路对精度和稳定性的要求。因此当今电源类管理芯片仍以0.25um到0.5um工艺为主,甚至有些产品还在使用1um工艺,其电源电压为5~6V,电源电压容差大,金属层厚度大导线单位电阻率小,互连线延迟远小于门延迟等等特点,都有利于电路设计者设计高精度的模拟电路。从约 2015 年至今,各大工艺厂商在积极开发和推进0.18um BCD工艺,但其主要特点是提供更小线宽的数字部分(如使用 1.8V供电的数字电路等),而模拟器件的沟道长度和电源电压相对于0.25um~0.5um BCD 工艺并没有明显改变。

地弹噪声是指芯片内部地与芯片外部PCB地,在电流变化时,由于压焊引线或其他金属布线的寄生电感产生电压涨落,从而引起芯片内部地电位发生涨落的电路谐振现象。这个寄生电感是地弹产生的根源,同时地弹也与芯片的负载情况密切相关。