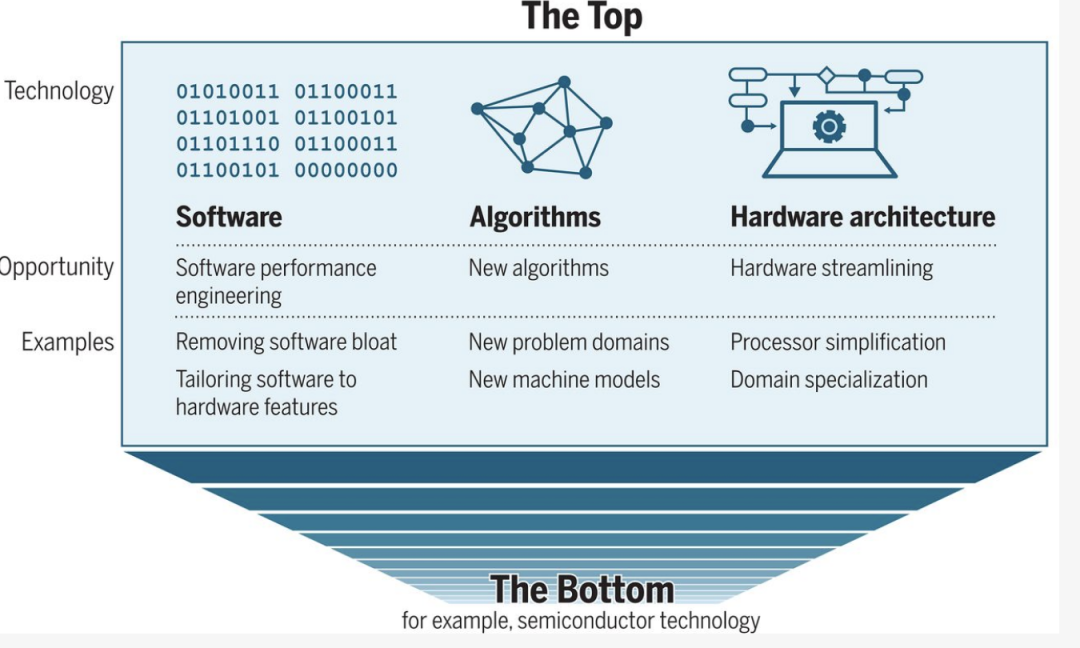

在摩尔定律时代,每两年芯片上的晶体管数量就会翻一番,这一看似不可避免的趋势被称为摩尔定律,它极大地促进了计算机性能的提高。然而,硅基晶体管不可能一直小下去,半导体晶体管的微型化推动了计算机性能的提升,但是这种提升已经持续了 50 多年。随着微型化接近极限,摩尔定律将走向终结,我们应该探索其他方法来保持性能的增长,这些方向主要包括:软件、算法和硬件架构。

1

如何让代码跑得更快?

我认为主要有 2 个方面

首先要计算机编程语言要适配硬件,现代计算机提供了旨在让代码运行得更快的架构特性。例如:同时执行多个操作的能力,代码可以多核并行执行;缓存的局部性,即计算机在内存中共置数据元素(空间局部性)或最近被访问过数据元素(时间局部性)时能够有效地访问数据元素。为了提高性能,程序需要暴露更多的并行性和局部性、甚至底层指令供上层编程利用。这就需要计算机编程语言充分利用硬件特性,如:如同步多线程、动态电压和频率调整、直接映射缓存和各种专用指令。提供简单而引人注目的抽象,使硬件的红利尽可能被利用。不出意外的话,未来 10 年,特定场景的计算机编程语言将出现井喷式的发展。

然后推行性能工程,简化软件膨胀问题,特别是一些编程语言和底层框架,简化的思想是这样的。假设你是一名程序员,被分配了一个问题 A 需要解决。你可以编写专门的代码直接解决 A,但你可能会注意到相关问题 B 已经得到解决。通过将 A 转换为可以使用 B 的现有代码解决的问题(相当于稍微修改一下 B,使其适配 A),即通过将 A 简化为 B ,你将花费更少的精力来解决 A 问题。

效率低下既可能来自归并本身(将 A 转换为 B ),也可能来自 B 的通用性(B 的解决方案并非专门针对 A 而定制)。但最大的膨胀来自不相干的复合:将 A 归并到 B,将 B 归并到 C,将 C 归并到 D。即使每次归并都能实现令人印象深刻的 80% 开发效率,但两次独立归约的序列只能实现 80% × 80% = 64%。再复合 20 次,效率将低于 1%,膨胀倍数为 100 倍,其效率不敢想象。

因为只考虑了功能的完整性,没有考虑性能,所以这种快速开发完成的代码往往很慢,再加上过去很少有用火焰图、全链路追踪等指标去衡量一段代码是否慢,到底慢在哪里.... 所以为了创造一个可以轻松编写快速代码的世界,程序编写者必须具备性能设计的知识和技能,并且必须大大改进辅助生产力工具。

从抽象角度来看,软件性能工程可以看作是一个涉及单个循环的简单过程,其中衡量指标主要包括耗时和资源占用:

(i)测量程序 A 的性能。

(ii)对程序 A 进行更改,以生成有望更快的程序 A ′。

(iii)测量程序 A ′的性能。

(iv)如果 A ′ 优于 A,则设置 A = A ′。

(v)如果 A 仍然不够快,则转到 (ii)。

由于摩尔时代多年的简化设计造成的累积膨胀,有很大的机会让程序运行得更快。不幸的是,使用专门的软件直接解决问题 A,需要 A 领域和性能工程方面的专业知识,这使得该过程比简单地修改 B 更昂贵且风险更大,所以解决 A 的最终专用软件通常比将 A 简化为 B 的软件更复杂。

2

算法

常规的性能优化的都是时间换空间,比如离线运行,懒加载等,代码运行速度变慢了,资源节约了;空间换时间,比如缓存、多线程等,代码运行速度变快了,同时资源消耗增加了。唯独算法优化,它是凌驾在常规性能优化之上,一个斐波那契数列从递归优化到普通循环,复杂度可以从 O(2^n)次方优化到 O(n)。随着问题规模增加至数十亿或万亿个数据点时,就平均年改进率而言,算法改进的重要性比硬件或摩尔定律重要得多。特别是在拥有大规模数据集的数据分析和机器学习领域,算法改进尤为重要。

3

硬件架构

从历史上看,计算机硬件架构师使用越来越多的晶体管来加快串行计算的速度,从而大大增加了处理核心的复杂性,尽管随着时间的推移,性能的提升收益逐渐减少。在后摩尔时代,架构师需要采取相反的策略,专注于硬件精简:使用更少的晶体管和更少的硅片面积来实现硬件功能。我们将看到,硬件精简的主要优势在于为更多电路提供额外的芯片面积,以便并行运行。因此,具有足够并行性的应用程序将获得最大的好处。事实上,对于没有太多并行性的应用程序,硬件的性能已经停滞不前。但在许多新兴应用领域,如机器学习、图形、视频和图像处理、传感计算和信号处理,都存在大量并行性。计算机架构师应该能够设计精简的架构,以便在摩尔定律结束后的许多年里为这些领域和其他领域提供更高的性能。

推荐

原创不易,随手关注或者"在看",诚挚感谢!