文章目录

-

- [PCIe Refclk](#PCIe Refclk)

- [Refclk 时钟架构](#Refclk 时钟架构)

-

- [Common Clock Architecture](#Common Clock Architecture)

- [Separate Clock Architecture](#Separate Clock Architecture)

- [Data Clock Architecture](#Data Clock Architecture)

PCIe Refclk

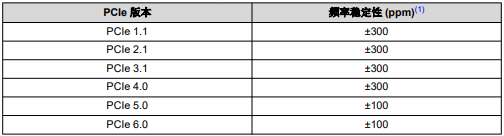

在 PCIe 系统中,为发送器和接收器器件提供了参考时钟 ,称为 REFCLK 。对于所有 PCIe 版本,REFCLK 都是

100MHz HCSL 时钟 ,下表 展示了通用时钟架构按版本列出的最大频率稳定性要求。

Refclk 时钟架构

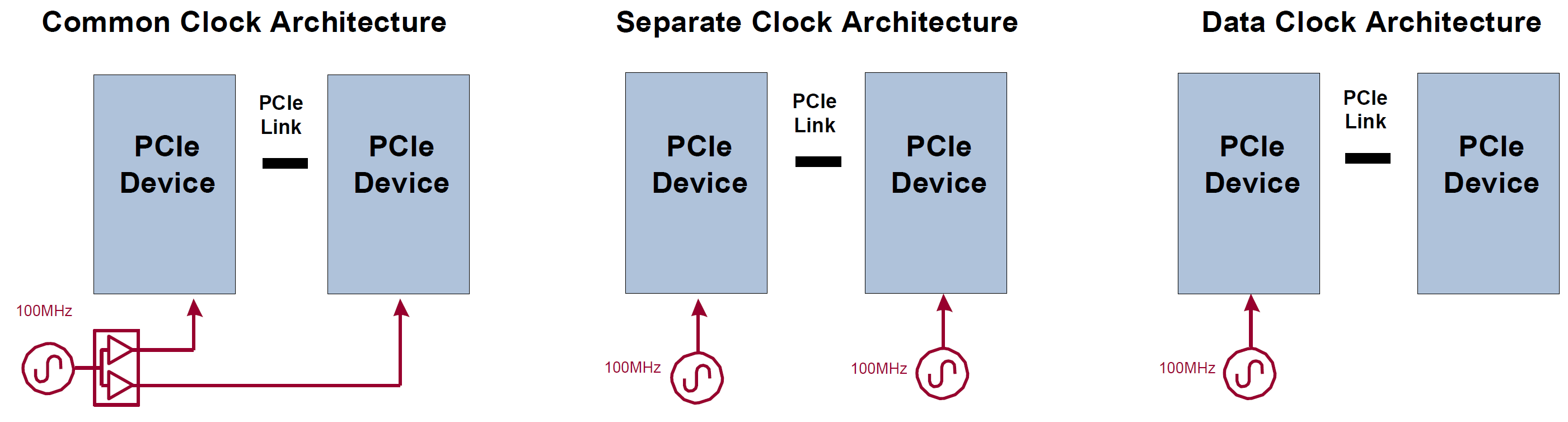

PCIe 主要有 3 种时钟架构(如下图),分别为:

- Common Clock Architecture (CC);

- Separate Clock Architecture ;

- Data Clock Architecture。

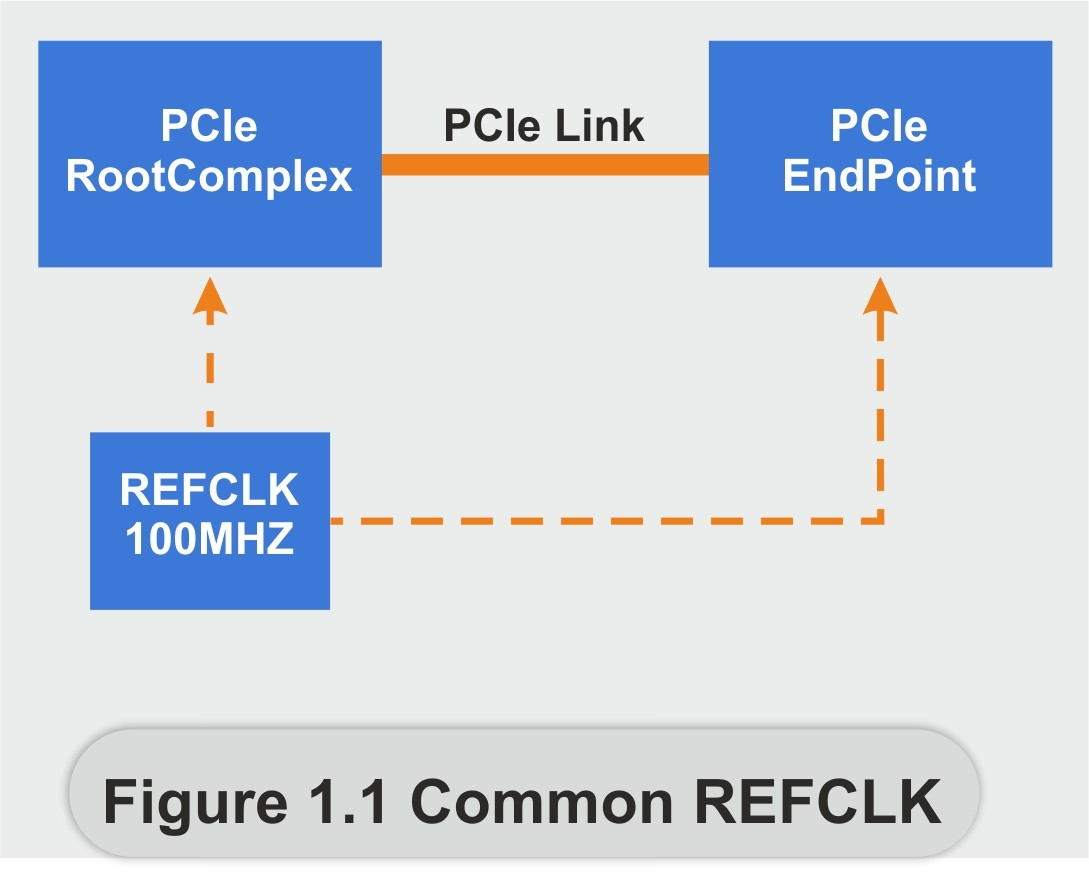

Common Clock Architecture

Common Clock Architecture (CC),通用参考时钟架构,收发端共享同一个参考时钟 。三种 PCIe 参考时钟架构中,Common Clock 是最为常用的一种时钟架构,采用 Common Clock 支持时钟扩频(SSC, Spread Spectrum Clock) 且对参考时钟的要求不如 Separate Clock 方案严苛。

Common Clock 对于频率稳定性的要求是 ±300 ppm。对于适用同一 Common Clock 作为参考时钟的 PCIe 设备,所有设备间的时钟偏斜(Clock Skew)必须保持在 12 ns 以内,这无疑对大型电路板上或跨板的 PCIe 设备间布局布线形成巨大挑战。

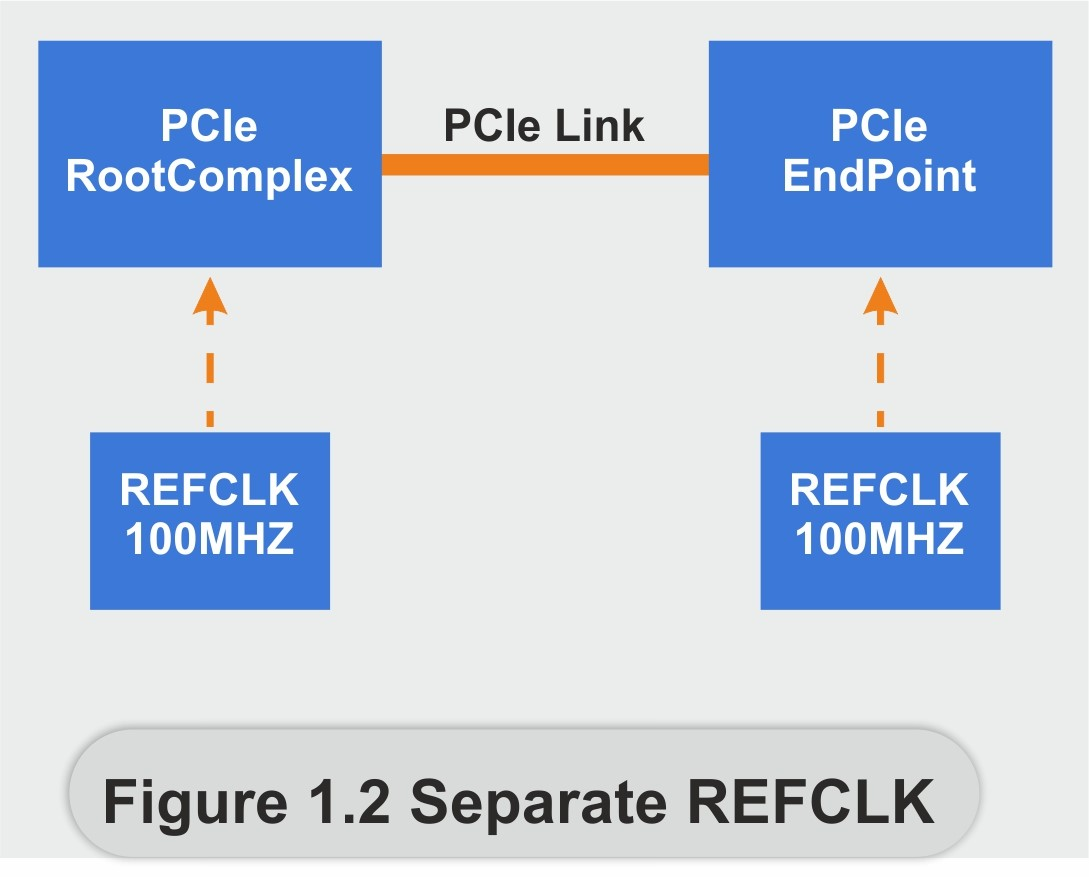

Separate Clock Architecture

Separate Clock Architecture ,收发端采用独立的参考时钟 ,根据有无 SSC 可进一步分为 SRNS ( Separate Refclk with No SSC) 及 SRIS (Separate Refclk with Independent SSC)。

对于收发端采用独立参考时钟的方案,其收发端独立使用不同的参考时钟源,无需单独传递时钟,对布局布线的要求更宽松。SRNS 允许 ±300 ppm (600ppm),而 SRIS 允许 ±2800 ppm (5600 ppm,其中SSC允许 5000ppm,TX/RX允许 600 ppm)。

若 PCIe 设备开启了 SRIS,其发生 SKP 的频率应该加大,同时加大弹性缓存(Elastic Buffer)的深度。弹性缓存加大使得延时更大,在一定程度上降低了 performance。对于一条 PCIe 链路,如何知道要不要采用 SRIS 呢?遗憾的是,目前尚没有机制实现收发端之间的 SRIS 协商。

Data Clock Architecture

Data Clock Architecture,仅发送端需要 Refclk,接收端无需外部 RefClk ,其 CDR (Clock Data Recovery,时钟数据恢复)的 Refclk 参考时钟从数据流中恢复出来。

Data Clock 时钟方案是三种方案中最易实现的方案,其无需外部参考时钟,在数据流中携带有时钟信息,接收端接收数据流并从中恢复出时钟供给其 CDR 作参考时钟。Data Clock 时钟方案仅适用于 Gen2 及 Gen3,单 lane 单向最高速率 8GT/s。

推荐阅读 :

https://www.ti.com.cn/cn/lit/an/zhcade7/zhcade7.pdf?ts

https://blog.csdn.net/weixin_40357487/article/details/123267953