ARM A64 LDR指令

- [1 LDR (immediate)](#1 LDR (immediate))

-

- [1.1 Post-index](#1.1 Post-index)

- [1.2 Pre-index](#1.2 Pre-index)

- [1.3 Unsigned offset](#1.3 Unsigned offset)

- [2 LDR (literal)](#2 LDR (literal))

- [3 LDR (register)](#3 LDR (register))

- [4 其他LDR指令变体](#4 其他LDR指令变体)

-

- [4.1 LDRB (immediate)](#4.1 LDRB (immediate))

-

- [4.1.1 Post-index](#4.1.1 Post-index)

- [4.1.2 Pre-index](#4.1.2 Pre-index)

- [4.1.3 Unsigned offset](#4.1.3 Unsigned offset)

- [4.2 LDRB (register)](#4.2 LDRB (register))

- [4.3 LDRH (immediate)](#4.3 LDRH (immediate))

-

- [4.3.1 Post-index](#4.3.1 Post-index)

- [4.3.2 Pre-index](#4.3.2 Pre-index)

- [4.3.3 Unsigned offset](#4.3.3 Unsigned offset)

- [4.4 LDRH (register)](#4.4 LDRH (register))

- [4.5 LDRSB (immediate)](#4.5 LDRSB (immediate))

-

- [4.5.1 Post-index](#4.5.1 Post-index)

- [4.5.2 Pre-index](#4.5.2 Pre-index)

- [4.5.3 Unsigned offset](#4.5.3 Unsigned offset)

- [4.6 LDRSB (register)](#4.6 LDRSB (register))

- [4.7 LDRSH (immediate)](#4.7 LDRSH (immediate))

-

- [4.7.1 Post-index](#4.7.1 Post-index)

- [4.7.2 Pre-index](#4.7.2 Pre-index)

- [4.7.3 Unsigned offset](#4.7.3 Unsigned offset)

- [4.8 LDRSH (register)](#4.8 LDRSH (register))

- [4.9 LDRSW (immediate)](#4.9 LDRSW (immediate))

-

- [4.9.1 Post-index](#4.9.1 Post-index)

- [4.9.2 Pre-index](#4.9.2 Pre-index)

- [4.9.3 Unsigned offset](#4.9.3 Unsigned offset)

- [4.10 LDRSW (literal)](#4.10 LDRSW (literal))

- [4.11 LDRSW (register)](#4.11 LDRSW (register))

Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile

1 LDR (immediate)

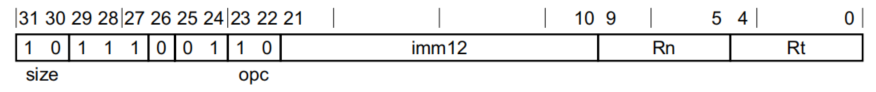

Load Register (immediate) loads a word or doubleword from memory and writes it to a register. The address that is used for the load is calculated from a base register and an immediate offset. The Unsigned offset variant scales the immediate offset value by the size of the value accessed before adding it to the base register value.

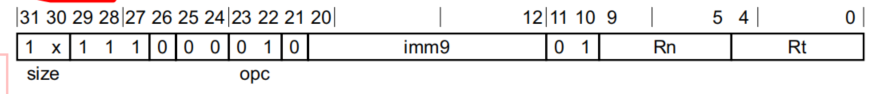

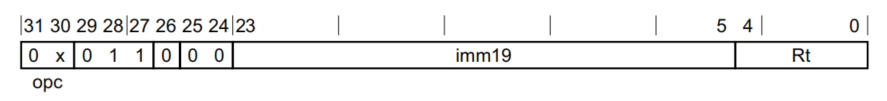

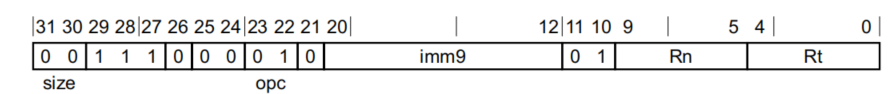

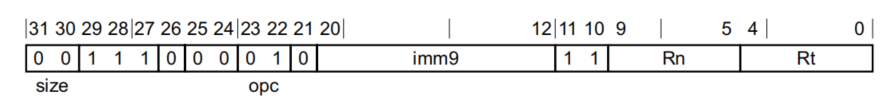

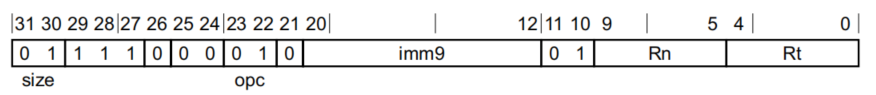

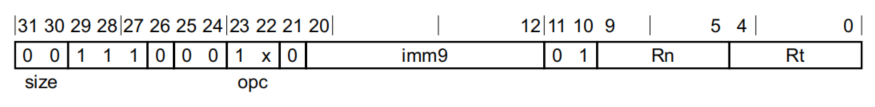

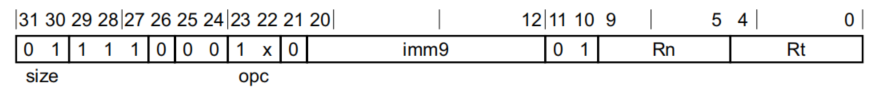

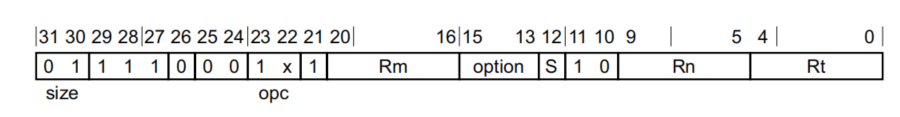

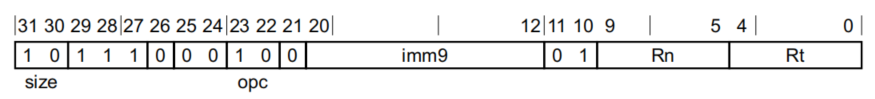

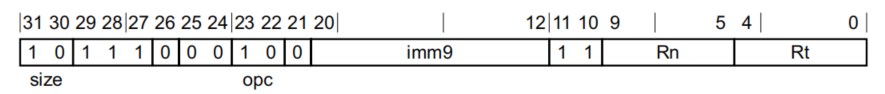

1.1 Post-index

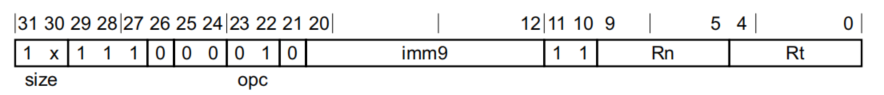

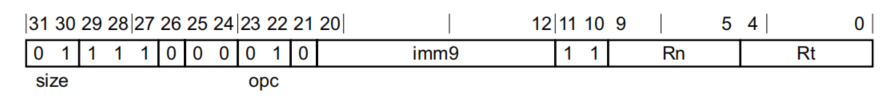

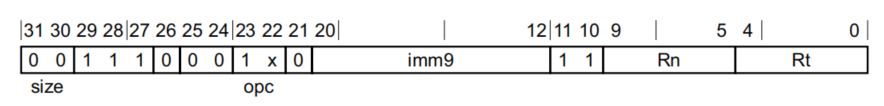

1.2 Pre-index

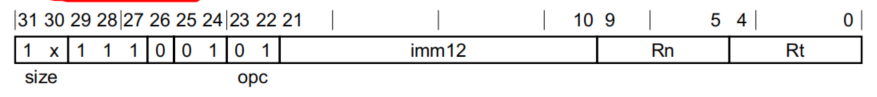

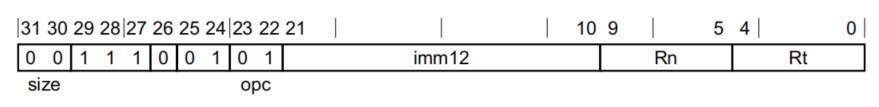

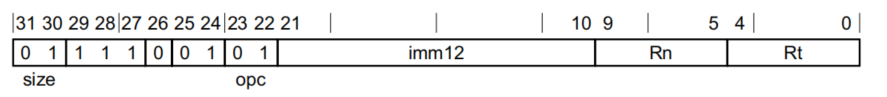

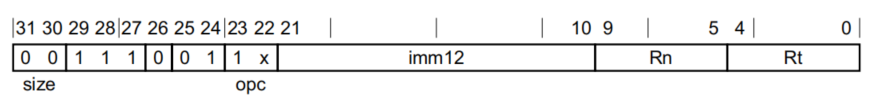

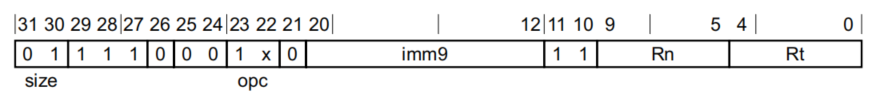

1.3 Unsigned offset

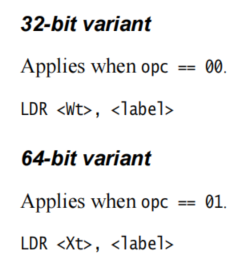

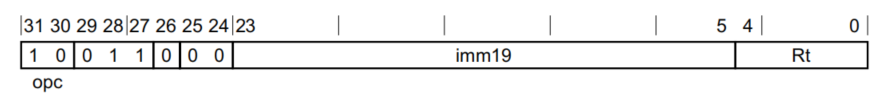

2 LDR (literal)

Load Register (literal) calculates an address from the PC value and an immediate offset, loads a word from memory, and writes it to a register.

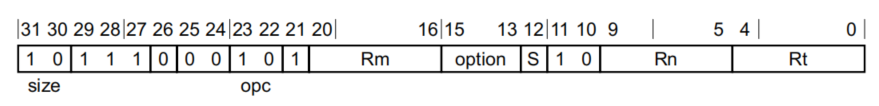

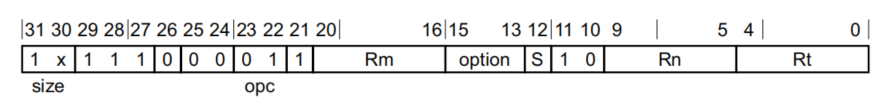

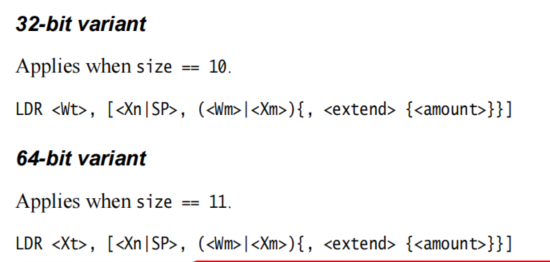

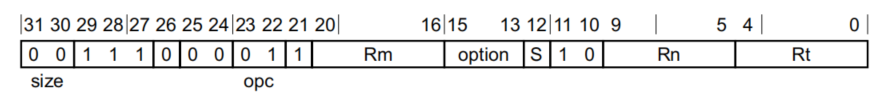

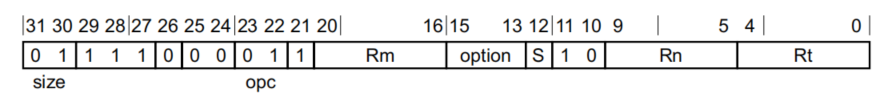

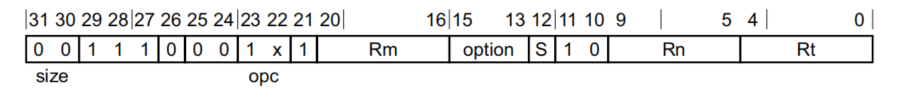

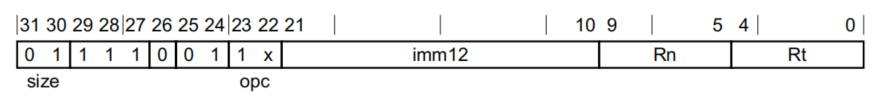

3 LDR (register)

Load Register (register) calculates an address from a base register value and an offset register value, loads a word from memory, and writes it to a register. The offset register value can optionally be shifted and extended.

4 其他LDR指令变体

4.1 LDRB (immediate)

4.1.1 Post-index

4.1.2 Pre-index

4.1.3 Unsigned offset

4.2 LDRB (register)

4.3 LDRH (immediate)

4.3.1 Post-index

4.3.2 Pre-index

4.3.3 Unsigned offset

4.4 LDRH (register)

4.5 LDRSB (immediate)

4.5.1 Post-index

4.5.2 Pre-index

4.5.3 Unsigned offset

4.6 LDRSB (register)

4.7 LDRSH (immediate)

4.7.1 Post-index

4.7.2 Pre-index

4.7.3 Unsigned offset

4.8 LDRSH (register)

4.9 LDRSW (immediate)

4.9.1 Post-index

4.9.2 Pre-index

4.9.3 Unsigned offset

4.10 LDRSW (literal)

4.11 LDRSW (register)