目录

[Chapter9 Exception and Interrupt Handling](#Chapter9 Exception and Interrupt Handling)

[9.1 Exception Handling](#9.1 Exception Handling)

[9.2 Interrupts](#9.2 Interrupts)

[9.3 Interrupt Handling Schemes](#9.3 Interrupt Handling Schemes)

[9.4 Summary](#9.4 Summary)

[Chapter10 Firmware](#Chapter10 Firmware)

[10.1 Firmware and Bootloader](#10.1 Firmware and Bootloader)

[10.2 Example: Sandstone](#10.2 Example: Sandstone)

[10.3 Summary](#10.3 Summary)

[Chapter11 Embedded Operating Systems](#Chapter11 Embedded Operating Systems)

[11.1 Fundamental Components](#11.1 Fundamental Components)

[11.2 Example: Simple Little Operating System](#11.2 Example: Simple Little Operating System)

[11.3 Summary](#11.3 Summary)

[Chapter12 Caches](#Chapter12 Caches)

[12.1 The Memory Hierarchy and Cache Memory](#12.1 The Memory Hierarchy and Cache Memory)

[12.2 Cache Architecture](#12.2 Cache Architecture)

[12.3 Cache Policy](#12.3 Cache Policy)

[12.4 Coprocessor 15 and Caches](#12.4 Coprocessor 15 and Caches)

[12.5 Flushing and Cleaning Cache Memory](#12.5 Flushing and Cleaning Cache Memory)

[12.6 Cache Lockdown](#12.6 Cache Lockdown)

[12.7 Caches and Software Performance](#12.7 Caches and Software Performance)

[12.8 Summary](#12.8 Summary)

[Chapter13 Memory Protection Units](#Chapter13 Memory Protection Units)

[13.1 Protected Regions](#13.1 Protected Regions)

[13.2 Initializing the MPU, Caches, and Write Buffer](#13.2 Initializing the MPU, Caches, and Write Buffer)

[13.3 Demonstration of an MPU system](#13.3 Demonstration of an MPU system)

[13.4 Summary](#13.4 Summary)

[Chapter14 Memory Management Units](#Chapter14 Memory Management Units)

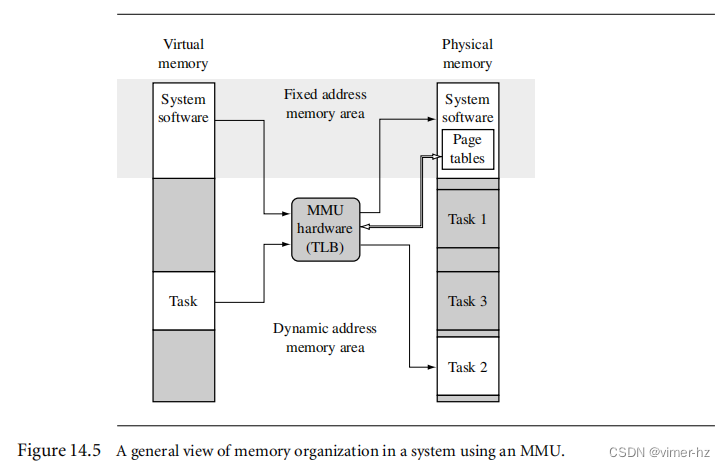

[14.1 Moving from an MPU to an MMU](#14.1 Moving from an MPU to an MMU)

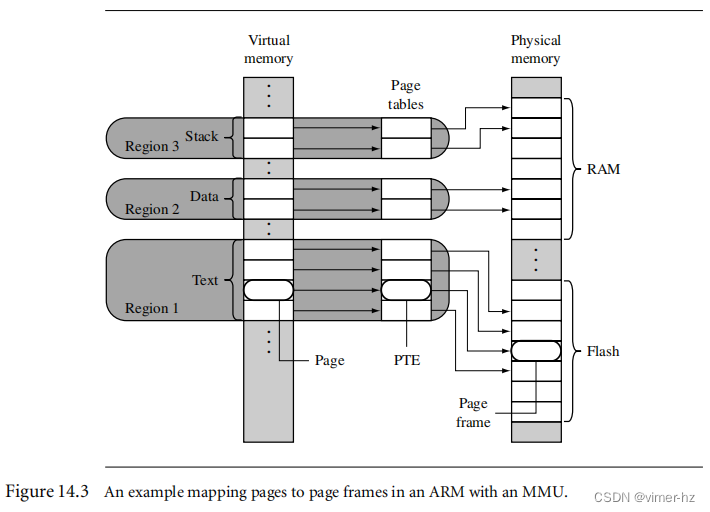

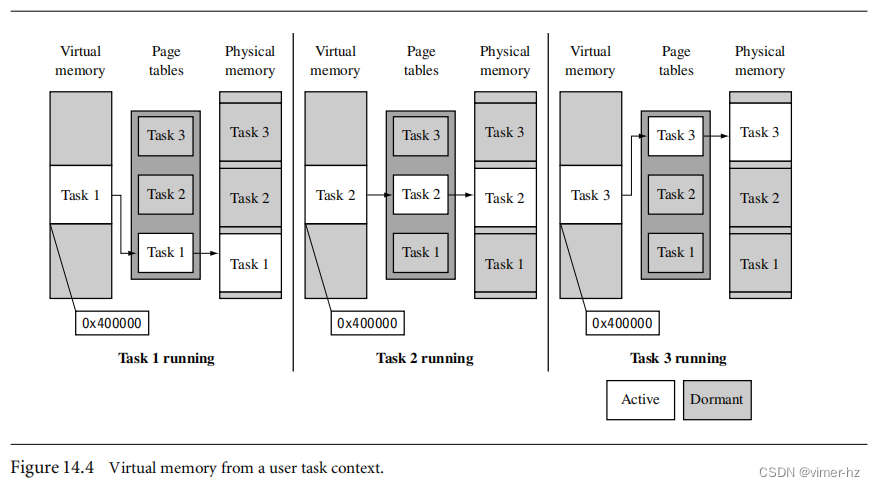

[14.2 How Virtual Memory Works](#14.2 How Virtual Memory Works)

[14.3 Details of the ARM MMU](#14.3 Details of the ARM MMU)

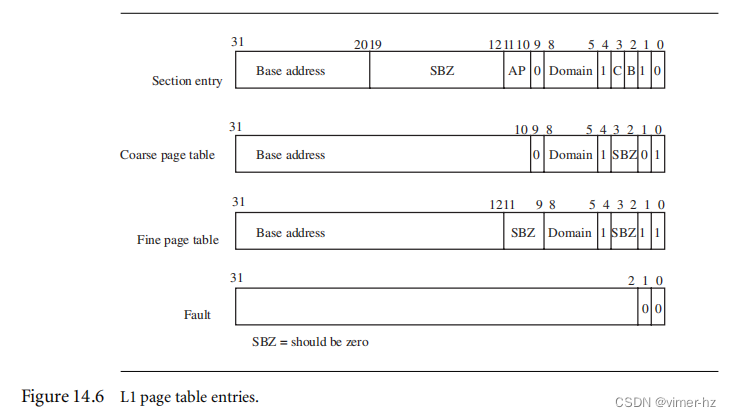

[14.4 Page Tables](#14.4 Page Tables)

[14.5 The Translation Lookaside Buffer](#14.5 The Translation Lookaside Buffer)

[14.6 Domains and Memory Access Permission](#14.6 Domains and Memory Access Permission)

[14.7 The Caches and Write Buffer](#14.7 The Caches and Write Buffer)

[14.8 Coprocessor 15 and MMU Configuration](#14.8 Coprocessor 15 and MMU Configuration)

[14.9 The Fast Context Switch Extension](#14.9 The Fast Context Switch Extension)

[14.10 Demonstration: A Small Virtual Memory System](#14.10 Demonstration: A Small Virtual Memory System)

[14.11 The Demonstration as mmuSLOS](#14.11 The Demonstration as mmuSLOS)

[14.12 Summary](#14.12 Summary)

[Chapter15 The Future of the Architecture](#Chapter15 The Future of the Architecture)

[15.1 Advanced DSP and SIMD Support in ARMv6](#15.1 Advanced DSP and SIMD Support in ARMv6)

[15.2 System and Multiprocessor Support Additions to ARMv6](#15.2 System and Multiprocessor Support Additions to ARMv6)

[15.3 ARMv6 Implementations](#15.3 ARMv6 Implementations)

[15.4 Future Technologies beyond ARMv6](#15.4 Future Technologies beyond ARMv6)

[15.5 Summary](#15.5 Summary)

[Suggested Reading](#Suggested Reading)

Chapter9 Exception and Interrupt Handling

嵌入式系统的核心是异常处理程序。它们负责处理外部系统产生的错误、中断和其他事件。高效的处理程序可以显著提高系统性能。确定一个良好的处理方法的过程可能会复杂、具有挑战性,但也是有趣的。

在本章中,我们将介绍异常处理的理论和实践,特别是在ARM处理器上处理中断的方法。ARM处理器有七种异常类型,可以中止正常的指令顺序执行:数据中止、快速中断请求、中断请求、预取中止、软件中断、复位和未定义指令。

本章分为三个主要部分:

■ 异常处理。异常处理涵盖了ARM处理器处理异常的具体细节。

■ 中断。ARM将中断定义为一种特殊类型的异常。本节讨论了中断请求的使用,以及介绍了与中断处理相关的一些常见术语、特性和机制。

■ 中断处理方案。最后一节提供了一组中断处理方法。每种方法都附带了一个示例实现。

9.1 Exception Handling

异常是指任何需要中止正常顺序执行指令的条件。例如,当ARM核心复位时,当指令获取或内存访问失败时,当遇到未定义指令时,当执行软件中断指令时,或者当外部中断被触发时。异常处理是处理这些异常的方法。

大多数异常都有一个关联的软件异常处理程序------当异常发生时执行的软件例程。例如,数据中止异常将有一个数据中止处理程序。处理程序首先确定异常的原因,然后处理异常。处理可以在处理程序内部进行,也可以通过跳转到特定的服务例程来进行。复位异常是一个特殊情况,因为它用于初始化嵌入式系统。

本节涵盖以下异常处理主题:

■ ARM处理器模式和异常

■ 向量表

■ 异常优先级

■ 链接寄存器偏移量

9.1.1 ARM Processor Exceptions and Modes

表9.1列出了ARM处理器的异常。每个异常都会导致核心进入特定的模式。此外,通过更改cpsr,可以手动进入ARM处理器的任何模式。用户模式和系统模式是唯一不由相应异常进入的两种模式,换句话说,要进入这些模式,必须修改cpsr。当异常引起模式改变时,核心会自动执行以下操作:

■ 将cpsr保存到异常模式的spsr中

■ 将pc保存到异常模式的lr中

■ 将cpsr设置为异常模式

■ 将pc设置为异常处理程序的地址

图9.1显示了异常及其关联模式的简化视图。请注意,当异常发生时,ARM处理器总是切换到ARM状态。

9.1.2 Vector Table

第2章介绍了向量表------一张地址表,ARM核心在引发异常时会跳转到其中的地址。这些地址通常包含以下形式的分支指令:

■ B <address>---此分支指令相对于pc提供一个分支。

■ LDR pc, [pc, #offset]---此加载寄存器指令将处理程序地址从内存加载到pc。该地址是一个存储在向量表附近的绝对32位值。加载这个绝对字面值会导致在分支到特定处理程序时稍微延迟,因为需要额外的内存访问。但是,您可以分支到内存中的任何地址。

■ LDR pc, [pc, #-0xff0]---此加载寄存器指令从地址0xfffff030加载特定的中断服务例程地址到pc。当存在向量中断控制器(VIC PL190)时,才会使用此特定指令。

■ MOV pc, #immediate---此移动指令将立即值复制到pc。它允许您跨越整个地址空间,但受限于对齐方式。地址必须是通过右移偶数位得到的8位即时数。

向量表还可以包含其他类型的指令。例如,FIQ处理程序可能从偏移量 +0x1c 处开始。因此,FIQ处理程序可以立即从FIQ向量位置开始,因为它位于向量表的末尾。分支指令使pc跳转到可以处理特定异常的特定位置。

表9.2显示了每个异常的异常、模式和向量表偏移量。

Example 9.1

图9.2展示了一个典型的向量表。未定义指令项是一个分支指令,用于跳转到未定义处理程序。其他向量使用带有LDR加载到pc指令的间接地址跳转。

请注意,FIQ处理程序也使用了LDR加载到pc指令,并没有利用处理程序可以放置在FIQ向量入口位置的优势。

9.1.3 Exception Priorities

异常可以同时发生,因此处理器必须采用优先级机制。表9.3显示了在ARM处理器上发生的各种异常及其关联的优先级。例如,复位异常是最高优先级的异常,在处理器通电时发生。因此,当发生复位时,它优先于所有其他异常。同样,当发生数据中止异常时,它优先于除复位异常以外的所有其他异常。最低的优先级由两个异常共享,即软件中断和未定义指令异常。某些异常还通过在cpsr中设置I或F位来禁用中断,如表9.3所示。

每个异常的处理方式根据表9.3中列出的优先级来进行。以下是对异常及其处理方式的摘要,从最高优先级开始。

复位异常是最高优先级的异常,并且只要它被触发,就会始终被执行。复位处理程序初始化系统,包括设置内存和缓存。在启用IRQ或FIQ中断之前,应初始化外部中断源,以避免适当的处理程序设置之前出现虚假中断的可能性。复位处理程序还必须为所有处理器模式设置堆栈指针。在处理程序的前几条指令中,假定不会发生异常或中断。代码应设计成避免SWI、未定义指令和可能中止的内存访问,即要小心实现处理程序,以避免进一步触发异常。

当内存控制器或MMU指示已访问无效内存地址(例如,对于某个地址没有物理内存)或当前代码尝试读取或写入未具有正确访问权限的内存时,将发生数据中止异常。在数据中止处理程序内部可以引发FIQ异常,因为FIQ异常未被禁用。当完全服务于FIQ后,控制权将返回到数据中止处理程序。

当外部外设将FIQ引脚置为nFIQ时,将发生快速中断请求(FIQ)异常。FIQ异常是最高优先级的中断。核心在进入FIQ处理程序时禁用IRQ和FIQ异常。因此,除非软件重新启用IRQ和/或FIQ异常,否则没有外部源可以中断处理器。希望FIQ处理程序(以及中止、SWI和IRQ处理程序)经过精心设计以有效地处理异常。

当外部外设将IRQ引脚置为nIRQ时,将发生中断请求(IRQ)异常。IRQ异常是第二高优先级的中断。如果既没有FIQ异常也没有数据中止异常发生,则将进入IRQ处理程序。进入IRQ处理程序时,IRQ异常被禁用,并且应在当前中断源被清除之前保持禁用状态。

当尝试提取指令时发生预取中止异常,表示发生了内存错误。当指令在流水线的执行阶段且没有发生更高优先级的其他异常时,会引发此异常。进入处理程序时,IRQ异常将被禁用,但FIQ异常将保持不变。如果启用了FIQ并发生了FIQ异常,则在服务预取中止时可以采取该异常。

当执行SWI指令并且没有标记任何其他更高优先级的异常时,将发生软件中断(SWI)异常。进入处理程序时,cpsr将被设置为超级用户模式。

如果系统使用嵌套的SWI调用,则在跳转到嵌套SWI之前必须存储链接寄存器r14和spsr,以避免链接寄存器和spsr可能被破坏。

当ARM或Thumb指令集之外的指令达到流水线的执行阶段且没有标记任何其他异常时,将发生未定义指令异常。ARM处理器会向协处理器"询问"它们是否能够处理此作为协处理器指令的指令。由于协处理器遵循流水线,因此指令识别可以在核心的执行阶段进行。如果没有协处理器认领该指令,则会引发未定义指令异常。

由于SWI指令和未定义指令不能同时发生(换句话说,正在执行的指令不能同时是SWI指令和未定义指令),它们具有相同的优先级。

9.1.4 Link Register Offsets

当异常发生时,链接寄存器(LR)会根据当前PC设置为特定的地址。例如,当引发IRQ异常时,链接寄存器LR指向上一条已执行指令的地址加上8。必须小心确保异常处理程序不会破坏LR寄存器,因为LR用于从异常处理程序返回。IRQ异常只在当前指令执行后发生,因此返回地址必须指向下一条指令,即LR-4。表9.4提供了不同异常的一些有用地址。

接下来的三个示例展示了从IRQ或FIQ异常处理程序中返回的不同方法。

示例9.2

这个示例展示了从IRQ和FIQ处理程序中返回的典型方法是使用SUBS指令:

bash

handler

<handler code>

...

SUBS pc, r14, #4

; pc=r14-4由于SUB指令末尾有一个S,且PC是目标寄存器,所以CPSR将自动从SPSR寄存器中恢复。

示例9.3

这个示例展示了另一种方法,在处理程序开始时从链接寄存器R14中减去偏移量。

bash

handler

SUB r14, r14, #4

; r14-=4

...

<handler code>

...

MOVS pc, r14

; return服务完成后,通过将链接寄存器R14移动到PC并从SPSR中恢复CPSR来返回到正常执行。

示例9.4

最后一个示例使用中断栈来存储链接寄存器。这种方法首先从链接寄存器中减去一个偏移量,然后将其存储到中断栈中。

bash

handler

SUB r14, r14, #4

; r14-=4

STMFD r13!,{r0-r3, r14}

; store context

...

<handler code>

...

LDMFD r13!,{r0-r3, pc}ˆ

; return为了返回到正常执行,使用LDM指令来加载PC。指令中的^符号强制将CPSR从SPSR中恢复。

9.2 Interrupts

在ARM处理器上有两种类型的中断可用。第一种类型的中断是由外部外围设备引发的异常,即IRQ和FIQ。第二种类型是由特定指令引发的异常,即SWI指令。这两种类型都会暂停程序的正常流程。

在本节中,我们主要关注IRQ和FIQ中断。我们将涵盖以下内容:

■ 分配中断

■ 中断延迟

■ IRQ和FIQ异常

■ 基本中断栈设计和实现

9.2.1 Assigning Interrupts

系统设计人员可以决定哪个硬件外设可以产生哪个中断请求。这个决策可以在硬件或软件(或两者兼有)中实现,具体取决于使用的嵌入式系统。

中断控制器将多个外部中断连接到两个ARM中的一个中断请求。复杂的控制器可以编程,允许外部中断源引发IRQ或FIQ异常。

在分配中断方面,系统设计人员采用了标准的设计实践:

■ 软件中断通常保留用于调用特权操作系统例程。例如,可以使用SWI指令将正在用户模式下运行的程序切换到特权模式。关于SWI处理程序示例,请参阅第11章。

■ 中断请求通常分配给通用中断。例如,定期定时器中断用于强制进行上下文切换,往往是IRQ异常。IRQ异常的优先级较低,中断延迟较高(将在下一节中讨论),而FIQ异常则相反。

■ 快速中断请求通常保留给需要快速响应时间的单个中断源,例如专门用于移动内存块的直接内存访问。因此,在嵌入式操作系统设计中,FIQ异常用于特定应用,将IRQ异常用于更通用的操作系统活动。

9.2.2 Interrupt Latency

在基于中断驱动的嵌入式系统中,必须解决中断延迟的问题,即从外部中断请求信号被触发到特定中断服务例程(ISR)的第一条指令被获取的时间间隔。

中断延迟取决于硬件和软件的组合。系统架构师必须平衡系统设计,以处理多个同时发生的中断源,并尽量最小化中断延迟。如果中断没有及时处理,系统响应时间将变慢。

软件处理程序有两种主要方法来最小化中断延迟。第一种方法是使用嵌套中断处理程序,即使当前正在处理一个现有的中断,也允许进一步的中断发生(参见图9.3)。这通过在中断源得到服务后立即重新启用中断(以防止生成更多的中断),但在中断处理完成之前实现。一旦处理完嵌套中断,就会将控制权交还给原始的中断服务例程。

第二种方法涉及优先级设置。您可以编程中断控制器忽略与您正在处理的中断相同或较低优先级的中断,以便仅有优先级更高的任务才能中断您的处理程序。然后您可以重新启用中断。

处理器会在较低优先级的中断上花费时间,直到出现一个更高优先级的中断。因此,高优先级的中断比低优先级的中断具有更低的平均中断延迟,通过加速关键的时序敏感中断的完成时间来减少延迟。

9.2.3 IRQ and FIQ Exceptions

只有在cpsr中清除了特定中断屏蔽位时,IRQ和FIQ异常才会发生。ARM处理器在处理中断之前会继续执行当前流水线里的执行阶段的指令------这是设计确定性中断处理程序的一个重要因素,因为某些指令需要更多的周期来完成执行阶段。

当未屏蔽中断引起IRQ或FIQ异常时,处理器硬件会经过标准的过程:

-

处理器切换到特定的中断请求模式,这反映了所引发的中断。

-

上一个模式的cpsr保存到新的中断请求模式的spsr中。

-

pc保存在新的中断请求模式的lr中。

-

中断被禁用,即在cpsr中禁用IRQ或同时禁用IRQ和FIQ异常。 这立即停止引发相同类型的另一个中断请求。

-

处理器跳转到向量表中的特定入口。

该过程根据引发的中断类型略有不同。我们将以示例说明两种中断。第一个示例展示了当引发IRQ异常时会发生什么,而第二个示例展示了引发FIQ异常时会发生什么。

示例9.5

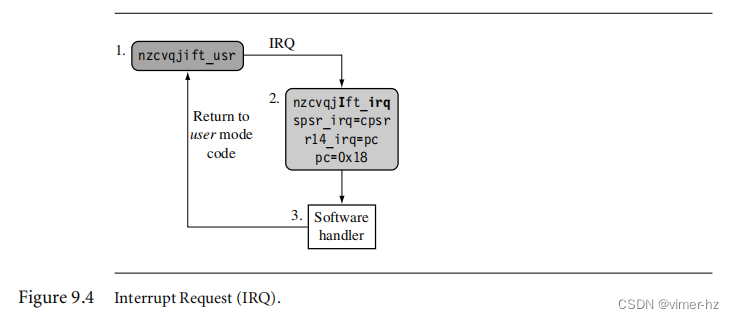

图9.4显示了当处理器处于用户模式时引发IRQ异常时会发生的情况。处理器从状态1开始。在这个示例中,cpsr中的IRQ和FIQ异常位都已启用。

当发生IRQ时,处理器进入状态2。这个转换会自动将IRQ位设置为1,禁止任何进一步的IRQ异常。然而,FIQ异常保持启用,因为FIQ具有更高的优先级,所以当引发低优先级的IRQ异常时,它不会被禁用。cpsr处理器模式切换到IRQ模式。用户模式cpsr会自动复制到spsr_irq中。

当中断发生时,寄存器r14_irq被赋予中断发生时的pc值。然后,pc被设置为向量表中的IRQ入口+0x18的地址。

在状态3中,软件处理程序接管并调用适当的中断服务例程来处理中断来源。完成后,处理器模式回退到状态1中的原始用户模式代码。

示例9.6

图9.5展示了一个FIQ异常的示例。处理器经历了与IRQ异常类似的过程,但是与只屏蔽进一步的IRQ异常不同,处理器还屏蔽了进一步的FIQ异常。这意味着在状态3中进入软件处理程序时,两个中断都被禁用了。

切换到FIQ模式意味着无需保存寄存器r8到r12,因为这些寄存器在FIQ模式下是分段的。这些寄存器可以用来保存临时数据,例如缓冲区指针或计数器。这使得FIQ非常适合处理单源、高优先级、低延迟的中断。

9.2.3.1 Enabling and Disabling FIQ and IRQ Exceptions

ARM处理器核心有一个简单的过程来手动启用和禁用中断,涉及到在处理器处于特权模式下修改cpsr。

表9.5展示了如何启用IRQ和FIQ中断。该过程使用了三条ARM指令。

第一条指令MRS将cpsr的内容复制到寄存器r1中。第二条指令清除IRQ或FIQ掩码位。第三条指令将更新后的内容从寄存器r1复制回cpsr,从而启用中断请求。后缀"_c"标识被更新的位域是cpsr的控制字段位[7:0]。(更多细节请参考第2章。)表9.6展示了禁用或屏蔽中断请求的类似过程。

重要的是要理解,在MSR指令完成流水线的执行阶段之后,中断请求才会被启用或禁用。在MSR完成这个阶段之前,中断仍然可以被触发或屏蔽。

要同时启用和禁用IRQ和FIQ异常,需要对第二条指令进行轻微修改。数据处理BIC或ORR指令上的立即数值必须更改为0xc0,以启用或禁用两个中断。

9.2.4 Basic Interrupt Stack Design and Implementation

异常处理程序广泛使用堆栈,每种模式都有一个专用的寄存器保存堆栈指针。异常堆栈的设计取决于以下因素:

-

操作系统要求:每个操作系统对堆栈设计都有自己的需求。

-

目标硬件:目标硬件为堆栈在内存中的大小和位置提供了物理限制。

对于堆栈,需要做两个设计决策:

-

位置决定了堆栈在内存映射中开始的位置。大多数基于ARM的系统设计中,堆栈向下扩展,堆栈的顶部位于较高的内存地址。

-

堆栈大小取决于处理程序的类型,是嵌套中断还是非嵌套中断。嵌套中断处理程序需要更多的内存空间,因为堆栈随着嵌套中断的数量而增长。

良好的堆栈设计试图避免堆栈溢出,即堆栈扩展到分配的内存之外,因为这会导致嵌入式系统不稳定。有软件技术可以识别溢出,并在不可修复的内存损坏发生之前采取纠正措施来修复堆栈。两种主要方法是:(1)使用内存保护和(2)在每个程序开始时调用堆栈检查函数。

在启用中断之前,必须设置IRQ模式堆栈,通常是在系统的初始化代码中完成。在简单的嵌入式系统中,了解堆栈的最大大小非常重要,因为在引导程序的初始阶段,固件会预留堆栈大小。

图9.6显示了线性地址空间中两种典型的内存布局。布局A显示了传统的堆栈布局,其中中断堆栈存储在代码段下方。布局B将中断堆栈放置在内存的顶部,用户堆栈上方。布局B相比于布局A的主要优点是,在发生堆栈溢出时不会破坏向量表,因此系统可以在识别到溢出后进行自我纠正。

每种处理器模式都需要设置一个堆栈。这是每次处理器重置时都要执行的操作。图9.7显示了使用布局A的实现方式。为了帮助设置内存布局,声明了一组定义,将内存区域名称映射到绝对地址。

例如,用户堆栈被赋予标签USR_Stack,并设置为地址0x20000。监管员堆栈设置在IRQ堆栈的下方128字节的地址处。

bash

USR_Stack EQU 0x20000

IRQ_Stack EQU 0x8000

SVC_Stack EQU IRQ_Stack-128为了帮助切换到不同的处理器模式,我们声明了一组定义,将每个处理器模式映射到特定的模式位模式。然后可以使用这些标签将cpsr设置为新的模式。

bash

Usr32md EQU 0x10

; User mode

FIQ32md EQU 0x11

; FIQ mode

IRQ32md EQU 0x12

; IRQ mode

SVC32md EQU 0x13

; Supervisor mode

Abt32md EQU 0x17

; Abort mode

Und32md EQU 0x1b

; Undefined instruction mode

Sys32md EQU 0x1f

; System mode为了安全起见,声明了一个定义来禁用cpsr中的IRQ和FIQ异常:

NoInt EQU 0xc0 ; 禁用中断

NoInt通过将屏蔽位设置为1来屏蔽两个中断。

初始化代码从为每个处理器模式设置堆栈寄存器开始。堆栈寄存器r13是在模式切换发生时始终会切换的寄存器之一。代码首先初始化IRQ堆栈。出于安全原因,最好使用NoInt和新模式之间的按位或运算来确保中断已禁用。

每种模式都必须设置堆栈。下面是在处理器内核从复位状态退出时如何设置三个不同堆栈的示例。请注意,由于这是一个基本示例,因此我们没有实现中止、FIQ和未定义指令模式的堆栈。如果需要这些堆栈,则使用非常相似的代码。

■ 监管者模式堆栈------处理器内核以监管者模式启动,因此SVC堆栈设置涉及将寄存器r13_svc加载到由SVC_NewStack指向的地址。对于此示例,该值为SVC_Stack。

bash

LDR r13, SVC_NewStack ; r13_svc

...

SVC_NewStack

DCD SVC_Stack■ IRQ模式堆栈------要设置IRQ堆栈,必须将处理器模式更改为IRQ模式。这是通过将cpsr位模式存储到寄存器r2中实现的。然后将寄存器r2复制到cpsr中,将处理器置于IRQ模式。此操作立即使寄存器r13_irq可见,并且可以将其分配给IRQ_Stack值。

bash

MOV r2, #NoInt|IRQ32md

MSR cpsr_c, r2

LDR r13, IRQ_NewStack ; r13_irq

...

IRQ_NewStack

DCD IRQ_Stack■ 用户模式堆栈------通常,用户模式堆栈是最后设置的,因为当处理器处于用户模式时,没有直接的方法来修改cpsr。另一种方法是强制处理器进入系统模式以设置用户模式堆栈,因为这两种模式共享相同的寄存器。

bash

MOV r2, #Sys32md

MSR cpsr_c, r2

LDR r13, USR_NewStack ; r13_usr

...

USR_NewStack

DCD USR_Stack对于每种模式使用单独的堆栈而不是使用单一堆栈进行处理有一个主要的优势:可以对错误的任务进行调试并与系统的其余部分隔离开来。这样可以更容易地定位和解决特定模式下的问题,同时保持其他模式的稳定性。

9.3 Interrupt Handling Schemes

在本节中,我们将介绍多种不同的中断处理方案,从简单的非嵌套中断处理程序到更复杂的分组优先级中断处理程序。每个方案都以一个通用描述和示例实现的形式呈现。

所涵盖的方案包括以下内容:

■ 非嵌套中断处理程序按顺序处理和服务各个中断。它是最简单的中断处理程序。

■ 嵌套中断处理程序处理多个中断,没有优先级分配。

■ 可重入中断处理程序处理可以优先级排序的多个中断。

■ 优先级简单中断处理程序处理优先级中断。

■ 优先级标准中断处理程序比低优先级中断更快地处理高优先级中断。

■ 优先级直接中断处理程序比低优先级中断更快地处理高优先级中断,并直接进入特定的服务例程。

■ 优先级分组中断处理程序是一种处理按不同优先级分组的中断的机制。

■ 基于VIC PL190的中断服务例程展示了向量中断控制器(VIC)如何改变中断服务例程的设计。

9.3.1 Nonnested Interrupt Handler

//非嵌套中断处理程序

最简单的中断处理程序是非嵌套方式,即在控制权返回到被中断的任务或进程之前,禁用中断。由于非嵌套中断处理程序一次只能处理一个中断,这种形式的处理程序不适用于需要处理多个具有不同优先级的中断的复杂嵌入式系统。

图9.8显示了在实现了简单非嵌套中断处理程序的系统中引发中断时发生的各个阶段:

-

禁用中断 - 当IRQ异常引发时,ARM处理器将禁止进一步发生IRQ异常。处理器模式设置为适当的中断请求模式,并将先前的cpsr复制到新可用的spsr_{interrupt request mode}中。然后,处理器将设置pc指向向量表中正确的条目,并执行指令。该指令将更改pc以指向特定的中断处理程序。

-

保存上下文 - 在进入处理程序代码时,它保存当前处理器模式的非银行寄存器的子集。

-

中断处理程序 - 处理程序然后识别外部中断源并执行适当的中断服务例程(ISR)。

-

中断服务例程 - ISR服务外部中断源并复位中断。

-

恢复上下文 - ISR返回到中断处理程序,中断处理程序恢复上下文。

-

启用中断 - 最后,为了从中断处理程序返回,将spsr_{interrupt request mode}恢复回cpsr。然后将pc设置为引发中断后的下一条指令。

在这个示例中,假设IRQ堆栈已经由初始化代码正确设置。

bash

interrupt_handler

SUB r14,r14,#4

; adjust lr

STMFD r13!,{r0-r3,r12,r14}

; save context

<interrupt service routine>

LDMFD r13!,{r0-r3,r12,pc}ˆ

; return第一条指令将链接寄存器r14_irq设置为返回到被中断的任务或进程的正确位置。根据第9.1.4节的描述,由于流水线的原因,在进入IRQ处理程序时,链接寄存器指向返回地址后四个字节,因此处理程序必须从链接寄存器减去四来补偿这个差异。链接寄存器存储在堆栈上。为了返回到被中断的任务,链接寄存器的内容从堆栈中恢复,并移动到pc寄存器。

注意,由于ATPCS(ARM Procedure Call Standard),也需要保留寄存器r0到r3和寄存器r12。这允许在处理程序内部调用符合ATPCS的子程序。

STMFD指令通过将一部分寄存器保存到堆栈上来保存上下文。为了减少中断延迟,我们只保存了最少数量的寄存器,因为执行STMFD或LDMFD指令的时间与传输的寄存器数量成比例。这些寄存器保存到由寄存器r13_{interrupt request mode}指向的堆栈中。

如果您在系统中使用高级语言,重要的是要了解编译器的过程调用约定,因为它会影响保存的寄存器及其保存顺序。例如,ARM编译器在子程序调用中保留了寄存器r4到r11,因此除非它们将被中断处理程序使用,否则没必要保留它们。如果没有调用C例程,则可能不需要保存所有寄存器。只有在寄存器已经保存到中断堆栈上时,才能安全地调用C函数。

在非嵌套中断处理程序中,不需要保存spsr,因为它不会被后续的中断破坏。

处理程序的最后,LDMFD指令将恢复上下文并从中断处理程序返回。LDMFD指令末尾的^表示cpsr将从spsr中恢复,这仅在同时加载了pc时有效。如果没有加载pc,则^将恢复用户银行寄存器。

在该处理程序中,所有处理都在中断处理程序内完成,并直接返回到应用程序。

一旦进入中断处理程序并保存了上下文,处理程序必须确定中断源。以下代码显示了如何简单确定中断源的示例。IRQStatus是中断状态寄存器的地址。如果无法确定中断源,则可以将控制权传递给另一个处理程序。在本示例中,我们将控制权传递给调试监视器。或者我们也可以忽略该中断。

bash

interrupt_handler

SUB r14,r14,#4

; r14-=4

STMFD sp!,{r0-r3,r12,r14} ; save context

LDR r0,=IRQStatus ; interrupt status addr

LDR r0,[r0]

; get interrupt status

TST r0,#0x0080

; if counter timer

BNE timer_isr

; then branch to ISR

TST r0,#0x0001

; else if button press

BNE button_isr

; then call button ISR

LDMFD sp!,{r0-r3,r12,r14} ; restore context

LDR pc,=debug_monitor ; else debug monitor在上述代码中,有两个中断服务程序(ISR):timer_isr和button_isr。它们分别映射到IRQStatus寄存器中的特定位,分别是0x0080和0x0001。

非嵌套中断处理程序的总结:

-

按顺序处理和服务各个中断。

-

中断延迟较高,在服务中断时无法处理其他发生的中断。

-

优点:相对容易实现和调试。

-

缺点:不能用于处理具有多个优先级中断的复杂嵌入式系统。

9.3.2 Nested Interrupt Handler

嵌套中断处理程序允许在当前调用的处理程序内发生另一个中断。这是通过在处理程序完全服务当前中断之前重新启用中断来实现的。

对于实时系统,这个特性增加了系统的复杂性,但也提高了性能。额外的复杂性引入了可能导致系统故障的微妙时间问题,而这些微妙问题可能极难解决。嵌套中断方法被精心设计,以避免这些类型的问题。这是通过保护上下文恢复不受中断干扰,以防止下一个中断填满堆栈(导致堆栈溢出)或破坏任何寄存器来实现的。

任何嵌套中断处理程序的首要目标是快速响应中断,使处理程序既不等待异步异常,也不强制它们等待处理程序。第二个目标是在处理各种中断的同时,不延迟常规同步代码的执行。

复杂性的增加意味着设计人员必须在效率和安全性之间取得平衡,采用一种防御性的编码风格,假设问题会发生。处理程序必须检查堆栈并在可能的情况下保护寄存器免受破坏。

图9.9展示了一个嵌套中断处理程序。从图中可以看出,与第9.3.1节中描述的简单非嵌套中断处理程序相比,处理程序要复杂得多。

嵌套中断处理程序的入口代码与简单非嵌套中断处理程序相同,只是在退出时,处理程序会测试一个由ISR更新的标志位。该标志位指示是否需要进一步处理。如果不需要进一步处理,则中断服务例程完成,处理程序可以退出。如果需要进一步处理,处理程序可能会执行以下几个操作:重新使能中断和/或进行上下文切换。

重新使能中断涉及从IRQ模式切换到SVC模式或系统模式。在IRQ模式下,不能简单地重新使能中断,因为这可能会导致链接寄存器r14_irq的破坏,特别是在执行BL指令后发生中断的情况下。这个问题将在第9.3.3节中更详细地讨论。

执行上下文切换意味着清空IRQ堆栈,因为只有当IRQ堆栈上有数据时,处理程序才不执行上下文切换。保存在IRQ堆栈上的所有寄存器必须转移到任务的堆栈上,通常是在SVC堆栈上。然后,剩余的寄存器必须保存在任务堆栈上。它们被转移到堆栈上的一个保留内存块,称为堆栈帧。

示例9.9

这个嵌套中断处理程序示例基于图9.9中的流程图。本节的其余部分将逐步介绍处理程序,并详细描述各个阶段。

bash

Maskmd

EQU 0x1f

; processor mode mask

SVC32md

EQU 0x13

; SVC mode

I_Bit

EQU 0x80

; IRQ bit

FRAME_R0

EQU 0x00

FRAME_R1

EQU FRAME_R0+4

FRAME_R2

EQU FRAME_R1+4

FRAME_R3

EQU FRAME_R2+4

FRAME_R4

EQU FRAME_R3+4

FRAME_R5

EQU FRAME_R4+4

FRAME_R6

EQU FRAME_R5+4

FRAME_R7

EQU FRAME_R6+4

FRAME_R8

EQU FRAME_R7+4

FRAME_R9

EQU FRAME_R8+4

FRAME_R10 EQU FRAME_R9+4

FRAME_R11 EQU FRAME_R10+4

FRAME_R12 EQU FRAME_R11+4

FRAME_PSR EQU FRAME_R12+4

FRAME_LR

EQU FRAME_PSR+4

FRAME_PC

EQU FRAME_LR+4

FRAME_SIZE EQU FRAME_PC+4

IRQ_Entry ; instruction

state : comment

SUB r14,r14,#4

; 2 :

STMDB r13!,{r0-r3,r12,r14} ; 2 : save context

<service interrupt>

BL read_RescheduleFlag ; 3 : more processing

CMP r0,#0

; 3 : if processing?

LDMNEIA r13!,{r0-r3,r12,pc}ˆ ; 4 : else return

MRS r2,spsr

; 5 : copy spsr_irq

MOV r0,r13

; 5 : copy r13_irq

ADD r13,r13,#6*4

; 5 : reset stack

MRS r1,cpsr

; 6 : copy cpsr

BIC r1,r1,#Maskmd

; 6 :

ORR r1,r1,#SVC32md

; 6 :

MSR cpsr_c,r1

; 6 : change to SVC

SUB r13,r13,#FRAME_SIZE-FRAME_R4;7: make space

STMIA r13,{r4-r11}

; 7 : save r4-r11

LDMIA r0,{r4-r9}

; 7 : restore r4-r9

BIC r1,r1,#I_Bit

; 8 :

MSR cpsr_c,r1

; 8 : enable IRA

STMDB r13!,{r4-r7}

; 9 : save r4-r7 SVC

STR r2,[r13,#FRAME_PSR] ; 9 : save PSR

STR r8,[r13,#FRAME_R12] ; 9 : save r12

STR r9,[r13,#FRAME_PC]

; 9 : save pc

STR r14,[r13,#FRAME_LR] ; 9 : save lr

<complete interrupt service routine>

LDMIA r13!,{r0-r12,r14}

; 11 : restore context

MSR spsr_cxsf,r14

; 11 : restore spsr

LDMIA r13!,{r14,pc}ˆ

; 11 : return这个示例使用了一个堆栈帧结构。除了堆栈寄存器r13之外,所有寄存器都保存在帧上。寄存器的顺序并不重要,只有FRAME_LR和FRAME_PC应该是帧中的最后两个寄存器,因为我们将使用一条指令返回:

LDMIA r13!, {r14, pc}

根据所使用的操作系统或应用程序的要求,可能还需要将其他寄存器保存到堆栈帧中。例如:

■ 当操作系统需要支持用户模式和SVC模式时,会保存寄存器r13_usr和r14_usr。

■ 当系统使用硬件浮点数时,会保存浮点寄存器。

这个示例中声明了一些预定义的宏。这些宏将cpsr/spsr的各种变化映射到特定的标签(例如I_Bit)。

还声明了一组预定义的宏,将各种帧寄存器引用映射到帧指针偏移量。当重新使能中断并且需要将寄存器存储到堆栈帧中时,这非常有用。在这个示例中,我们将堆栈帧存储在SVC堆栈上。

这个示例处理程序的入口点使用了与简单的非嵌套中断处理程序相同的代码。首先修改链接寄存器r14,使其指向正确的返回地址,然后将上下文和链接寄存器r14保存到IRQ堆栈上。

然后,中断服务例程对中断进行处理。当处理完成或部分完成时,控制权被传递回处理程序。处理程序然后调用一个名为read_RescheduleFlag的函数,该函数确定是否需要进一步处理。如果不需要进一步处理,它会在寄存器r0中返回一个非零值;否则返回零。请注意,我们没有包含read_RescheduleFlag的源代码,因为它是与实现相关的。

然后测试寄存器r0中的返回标志。如果寄存器不等于零,处理程序将恢复上下文并将控制权返回给挂起的任务。

将寄存器r0设置为零,表示需要进一步处理。首先保存spsr,将spsr_irq的副本移动到寄存器r2中。然后处理程序可以在后面的代码中将spsr存储在堆栈帧中。

将寄存器r13_irq指向的IRQ堆栈地址复制到寄存器r0中以备后用。下一步是将IRQ堆栈扁平化(清空)。这通过在栈顶添加6 * 4字节来实现,因为栈是向下增长的,可以使用ADD指令设置栈。

处理程序无需担心IRQ堆栈上的数据被另一个嵌套中断破坏,因为中断仍处于禁用状态,直到IRQ堆栈上的数据恢复完毕后,处理程序才会重新使能中断。

然后处理程序切换到SVC模式;中断仍处于禁用状态。将cpsr复制到寄存器r1并修改以将处理器模式设置为SVC。然后将寄存器r1写回cpsr,并将当前模式更改为SVC模式。新的cpsr的副本留在寄存器r1中供以后使用。

下一阶段是通过扩展栈来创建一个堆栈帧。寄存器r4到r11可以保存在堆栈帧中,这将释放足够的寄存器空间,以便从寄存器r0中还原IRQ堆栈中的其余寄存器。

此阶段,堆栈帧将包含表9.7中显示的信息。不在帧中的唯一寄存器是进入IRQ处理程序时存储的寄存器。

表9.8显示了与现有IRQ寄存器对应的SVC模式下的寄存器。现在处理程序可以从IRQ堆栈检索所有数据,并且可以安全地重新使能中断。

允许重新使能IRQ异常,处理程序已保存了所有重要的寄存器。现在可以完成堆栈帧。表9.9显示了一个完整的堆栈帧,可用于上下文切换或处理嵌套中断。

此阶段可以处理剩余的中断服务。通过将当前任务的控制块中的寄存器r13的当前值保存起来,并从新任务的控制块加载一个新值,可以执行上下文切换。

现在可以返回到被中断的任务/处理程序,或者如果发生了上下文切换,可以返回到另一个任务。

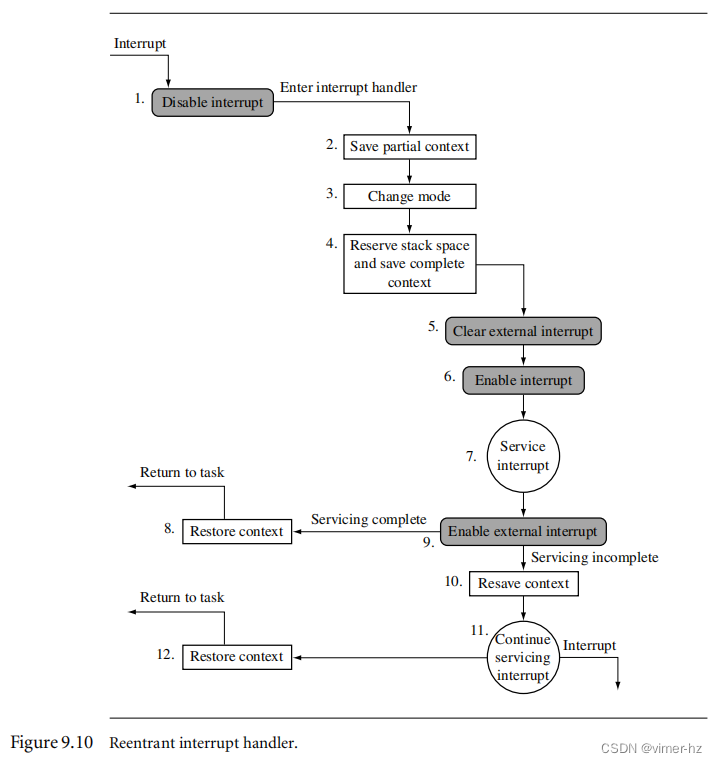

9.3.3 Reentrant Interrupt Handler

//可重入中断处理程序

可重入中断处理程序是一种处理多个中断的方法,其中中断根据优先级进行过滤,这对于要求具有较低延迟的高优先级中断非常重要。传统的嵌套中断处理程序无法实现这种优先级过滤。

可重入中断处理程序与嵌套中断处理程序的基本区别在于,可重入中断处理程序在早期阶段重新使能中断,这可以减少中断延迟。在稍后的部分中,将详细描述关于早期重新使能中断的一些问题。

在ARM处理器上,所有中断都必须在SVC、系统、未定义指令或中止模式下进行服务。

如果在中断模式下重新使能中断,并且中断例程执行了BL子程序调用指令,那么子程序的返回地址将设置在寄存器r14_irq中。该地址将随后被中断破坏,中断会覆盖返回地址到r14_irq中。为了避免这种情况,中断例程应该切换到SVC或系统模式。然后,BL指令可以使用寄存器r14_svc来存储子程序的返回地址。在通过cpsr重新使能中断之前,必须通过在中断控制器中设置一个位来禁用中断的源。

这样,可重入中断处理程序可以实现中断的优先级过滤,并且能够减少中断的延迟。这对于要求高可靠性和响应性的系统来说非常重要,特别是在嵌入式系统和实时操作系统中。

如果在处理完成之前在cpsr中重新使能中断,并且未禁用中断源,则会立即重新生成中断,从而导致无限中断序列或竞态条件。大多数中断控制器都有一个中断屏蔽寄存器,允许屏蔽一个或多个中断,但是其余的中断仍然是使能的。

由于中断在SVC模式下服务(例如,在任务的堆栈上),因此中断堆栈未被使用。相反,IRQ堆栈寄存器r13被用来指向一个12字节的数据结构,该结构将用于在中断进入时临时存储一些寄存器。

示例9.10

假设已经设置寄存器r13_irq以指向一个12字节的数据结构,并且不指向标准的IRQ堆栈。诸如IRQ_SPSR之类的偏移量用于指向数据结构内的位置。与所有中断处理程序一样,需要一些标准的定义来修改cpsr和spsr寄存器。

bash

IRQ_R0 EQU 0

IRQ_spsr EQU 4

IRQ_R14 EQU 8

Maskmd EQU 0x1f

; mask mode

SVC32md EQU 0x13

; SVC mode

I_Bit

EQU 0x80

; IRQ bit

ic_Base EQU 0x80000000

IRQStatus EQU 0x0

IRQRawStatus EQU 0x4

IRQEnable EQU 0x8

IRQEnableSet EQU 0x8

IRQEnableClear EQU 0xc

IRQ_Entry ; instruction

state : comment

SUB r14, r14, #4

; 2 : r14_irq-=4

STR r14, [r13, #IRQ_R14] ; 2 : save r14_irq

MRS r14, spsr

; 2 : copy spsr

STR r14, [r13, #IRQ_spsr] ; 2 : save spsr

STR r0, [r13, #IRQ_R0] ; 2 : save r0

MOV r0, r13

; 2 : copy r13_irq

MRS r14, cpsr

; 3 : copy cpsr

BIC r14, r14, #Maskmd ; 3 :

ORR r14, r14, #SVC32md ; 3 :

MSR cpsr_c, r14

; 3 : enter SVC mode

STR r14, [r13, #-8]!

; 4 : save r14

LDR r14, [r0, #IRQ_R14] ; 4 : r14_svc=r14_irq

STR r14, [r13, #4]

; 4 : save r14_irq

LDR r14, [r0, #IRQ_spsr] ; 4 : r14_svc=spsr_irq

LDR r0, [r0, #IRQ_R0] ; 4 : restore r0

STMDB r13!, {r0-r3,r8,r12,r14} ; 4 : save context

LDR r14, =ic_Base

; 5 : int crtl address

LDR r8, [r14, #IRQStatus] ; 5 : get int status

STR r8, [r14, #IRQEnableClear];5: clear interrupts

MRS r14, cpsr

; 6 : r14_svc=cpsr

BIC r14, r14, #I_Bit

; 6 : clear I-Bit

MSR cpsr_c, r14

; 6 : enable IRQ int

BL process_interrupt ; 7 : call ISR

LDR r14, =ic_Base

; 9 : int ctrl address

STR r8, [r14, #IRQEableSet] ; 9 : enable ints

BL read_RescheduleFlag ; 9 : more processing

CMP r0, #0

; 8 : if processing

LDMNEIA r13!, {r0-r3,r8,r12,r14} ; 8 : then load context

MSRNE spsr_cxsf, r14

; 8 : update spsr

LDMNEIA r13!, {r14, pc}ˆ

; 8 : return

LDMIA r13!, {r0-r3, r8} ; 10 : else load reg

STMDB r13!, {r0-r11}

; 10 : save context

BL continue_servicing ; 11 : continue service

LDMIA r13!, {r0-r12, r14} ; 12 : restore context

MSR spsr_cxsf, r14

; 12 : update spsr

LDMIA r13!, {r14, pc}ˆ

; 12 : return处理的开始包括一个普通的中断入口,其中从寄存器r14_irq中减去了4。

现在重要的是为由寄存器r13_irq指向的数据结构中的各个字段分配值。记录的寄存器包括r14_irq、spsr_irq和r0。寄存器r0用于在切换到SVC模式时传递指向数据结构的指针,因为寄存器r0不会被分组保存。这就是为什么不能使用寄存器r13_irq来进行此操作:它在SVC模式下不可见。

将指向数据结构的指针通过将寄存器r13_irq复制到r0中来保存。

处理程序将使用操作cpsr的标准过程将处理器设置为SVC模式。SVC模式下的链接寄存器r14被保存在SVC堆栈上。减去8为堆栈提供了两个32位字的空间。

然后,恢复并将寄存器r14_irq存储在SVC堆栈上。现在,IRQ和SVC的链接寄存器r14都存储在SVC堆栈上。

从传递到SVC模式的数据结构中恢复剩下的IRQ上下文。现在,寄存器r14_svc将包含IRQ模式的spsr。

然后,寄存器被保存到SVC堆栈上。寄存器r8用于保存在中断处理程序中被禁用的中断的中断屏蔽位。它们将在稍后重新启用。

然后禁用中断源。嵌入式系统此时会对中断进行优先级排序,并禁用低于当前优先级的所有中断,以防止低优先级中断锁定高优先级中断。中断优先级排序将在本章后面讨论。

由于中断源已经清除,现在可以安全地重新启用IRQ异常。通过清除cpsr中的i位来实现。请注意,中断控制器仍然禁用外部中断。

现在可以处理中断了。中断处理不应尝试进行上下文切换,因为外部源中断已被禁用。如果在中断处理过程中需要进行上下文切换,则应设置一个标志,稍后由中断处理程序接收。现在可以安全地重新启用外部中断。

处理程序需要检查是否需要进一步处理。如果寄存器r0中的返回值非零,则不需要进一步处理。如果为零,则处理程序恢复上下文,然后将控制权返回到挂起的任务。

现在必须创建一个堆栈帧,以便服务例程可以完成。这是通过恢复一部分上下文,然后将完整的上下文保存回SVC堆栈来实现的。

调用完成中断服务的子例程continue_servicing。此例程未提供,因为它与具体实现有关。

中断例程完成服务后,可以将控制权交还给挂起的任务。

总结: 可重入中断处理程序

■ 处理多个可以优先级排序的中断。

■ 中断延迟低。

■ 优点:处理具有不同优先级的中断。

■ 缺点:趋向于更复杂。

9.3.4 Prioritized Simple Interrupt Handler

非嵌套中断处理程序和嵌套中断处理程序都按先到先服务的顺序处理中断。相比之下,优先级中断处理程序将特定的中断源与优先级级别相关联。优先级级别用于确定中断的处理顺序。因此,较高优先级的中断将优先于较低优先级的中断,这在许多嵌入式系统中是一种特别理想的特性。

处理优先级的方法可以在硬件或软件中实现。对于硬件优先级,处理程序设计更简单,因为中断控制器将提供需要服务的当前最高优先级中断。这些系统在启动时需要更多的初始化代码,因为必须在系统启动之前构建中断和相关优先级级别表;另一方面,软件优先级需要额外的外部中断控制器的帮助。这个中断控制器必须提供一组最小功能,包括能够设置和取消屏蔽、读取中断状态和源。

本节的其余部分将介绍一个软件优先级技术,因为它是一种通用方法,并不依赖于专门的中断控制器。为了描述优先级中断处理程序,我们将介绍一个基于ARM标准中断控制器的虚构中断控制器。该控制器接收多个中断源,并根据特定中断源的使能状态生成IRQ和/或FIQ信号。

图9.11显示了基于可重入中断处理程序的简单优先级中断处理程序的流程图。

示例 9.11

中断控制器有一个寄存器(IRQRawStatus),用于保存原始中断状态-在被控制器屏蔽之前的中断信号状态。IRQEnable寄存器确定了哪些中断被从处理器屏蔽。只能使用IRQEnableSet和IRQEnableClear来设置或清除该寄存器。表9.10显示了中断控制器寄存器名称、与控制器基地址的偏移量、读/写操作以及寄存器的描述。

bash

I_Bit

EQU 0x80

PRIORITY_0 EQU 2

; Comms Rx

PRIORITY_1 EQU 1

; Comms Tx

PRIORITY_2 EQU 0

; Timer 1

PRIORITY_3 EQU 3

; Timer 2

BINARY_0 EQU 1 << PRIORITY_0 ; 1 << 2 0x00000004

BINARY_1 EQU 1 << PRIORITY_1 ; 1 << 1 0x00000002

BINARY_2 EQU 1 << PRIORITY_2 ; 1 << 0 0x00000001

BINARY_3 EQU 1 << PRIORITY_3 ; 1 << 3 0x00000008

MASK_3 EQU BINARY_3

MASK_2 EQU MASK_3+BINARY_2

MASK_1 EQU MASK_2+BINARY_1

MASK_0 EQU MASK_1+BINARY_0

ic_Base EQU 0x80000000

IRQStatus EQU 0x0

IRQRawStatus EQU 0x4

IRQEnable EQU 0x8

IRQEnableSet EQU 0x8

IRQEnableClear EQU 0xc

IRQ_Handler ; instruction

state : comment

SUB r14, r14, #4

; 2 : r14_irq -= 4

STMFD r13!, {r14}

; 2 : save r14_irq

MRS r14, spsr

; 2 : copy spsr_irq

STMFD r13!, {r10,r11,r12,r14} ; 2 : save context

LDR r14, =ic_Base

; 3 : int crtl addr

MOV r11, #PRIORITY_3

; 3 : default priority

LDR r10, [r14, #IRQStatus] ; 3 : load IRQ status

TST r10, #BINARY_3

; 4 : if Timer 2

MOVNE r11, #PRIORITY_3

; 4 : then P3(lo)

TST r10, #BINARY_2

; 4 : if Timer 1

MOVNE r11, #PRIORITY_2

; 4 : then P2

TST r10, #BINARY_1

; 4 : if Comm Tx

MOVNE r11, #PRIORITY_1

; 4 : then P1

TST r10, #BINARY_0

; 4 : if Comm Rx

MOVNE r11, #PRIORITY_0

; 4 : then P0(hi)

LDR r12, [r14,#IRQEnable] ; 4 : IRQEnable reg

ADR r10, priority_masks ; 4 : mask address

LDR r10, [r10,r11,LSL #2] ; 4 : priority value

AND r12, r12,r10

; 4 : AND enable reg

STR r12, [r14,#IRQEnableClear];4: disable ints

MRS r14, cpsr

; 4 : copy cpsr

BIC r14, r14, #I_Bit

; 4 : clear I-bit

MSR cpsr_c, r14

; 4 : enable IRQ ints

LDR pc, [pc, r11, LSL#2] ; 5 : jump to an ISR

NOP

;

DCD service_timer1

; timer1 ISR

DCD service_commtx

; commtx ISR

DCD service_commrx

; commrx ISR

DCD service_timer2

; timer2 ISR

priority_masks

DCD MASK_2

; priority mask 2

DCD MASK_1

; priority mask 1

DCD MASK_0

; priority mask 0

DCD MASK_3

; priority mask 3

...

service_timer1

STMFD r13!, {r0-r9}

; 6 : save context

<service routine>

LDMFD r13!, {r0-r10}

; 7 : restore context

MRS r11, cpsr

; 8 : copy cpsr

ORR r11, r11, #I_Bit

; 8 : set I-bit

MSR cpsr_c, r11

; 8 : disable IRQ

LDR r11, =ic_Base

; 8 : int ctrl addr

STR r12, [r11, #IRQEnableSet] ; 8 : enable ints

LDMFD r13!, {r11, r12, r14} ; 9 : restore context

MSR spsr_cxsf, r14

; 9 : set spsr

LDMFD r13!, {pc}ˆ

; 9 : return大多数中断控制器还具有相应的寄存器用于 FIQ 异常,并且甚至允许将个别中断源连接到发送到核心的特定中断信号上。因此,通过对控制器进行编程,可以使特定的中断源引发 IRQ 或 FIQ 异常。

这些寄存器相对于内存中的基地址进行偏移。表 9.10 显示了从中断控制器基地址 `ic_Base` 开始的各个寄存器的所有偏移量。请注意,偏移量 `0x08` 同时用于 `IRQEnable` 和 `IRQEnableSet`。

在中断控制器中,每个位与特定的中断源相关联(参见图 9.12)。例如,位 2 与串行通信的接收中断源相关联。

PRIORITY_x 定义了四个中断源的优先级,用于示例中,其中 PRIORITY_0 是最高优先级中断,PRIORITY_3 是最低优先级中断。

BINARY_x 定义了每个优先级级别的位模式。例如,对于 PRIORITY_0 中断,二进制模式将是 0x00000004(或 1 乘以 2)。对于每个优先级级别,都有一个相应的掩码,用于屏蔽与或低于该优先级的所有中断。例如,MASK_2 将屏蔽来自 Timer2(优先级为 3)和 CommRx(优先级为 2)的中断。

中断控制器寄存器的定义也已列出。ic_Base 是基地址,其余的定义(例如,IRQStatus)都是相对于该基地址的偏移量。

优先级中断处理程序从标准进入开始,但首先只存储 IRQ 链接寄存器到 IRQ 栈上。

接下来,处理程序获取 spsr 并将内容放入寄存器 r14_irq,并释放一组寄存器以用于处理优先级。

处理程序需要获取中断控制器的状态。这可以通过将中断控制器的基地址加载到寄存器 r14,并将寄存器 r10 加载为 ic_Base(寄存器 r14)偏移 IRQStatus(0x00)来实现。

然后,处理程序需要通过测试状态信息来确定最高优先级中断。如果特定的中断源与优先级级别匹配,则将优先级级别设置在寄存器 r11 中。该方法从最低优先级开始,依次比较中断源与所有设置的优先级级别,直到最高优先级。

在此代码片段之后,寄存器 r14_irq 将包含中断控制器的基地址,寄存器 r11 将包含最高优先级中断的位号。现在重要的是禁用低优先级和相等优先级中断,以便高优先级中断仍然可以中断处理程序。

请注意,这种方法更具确定性,因为发现优先级所需的时间始终相同。

要设置控制器中的中断屏蔽位,处理程序必须确定当前的 IRQ enable 寄存器,并获取优先级屏蔽表的起始地址。priority_masks 在处理程序末尾定义。

寄存器 r12 现在将包含当前的 IRQ enable 寄存器,寄存器 r10 将包含优先级表的起始地址。为了获取正确的掩码,将寄存器 r11 左移两位(使用移位器左移 #2)。这将使地址乘以四,并加上优先级表的起始地址。

寄存器 r10 包含新的掩码。下一步是使用掩码清除低优先级中断,通过将掩码与寄存器 r12(IRQEnable 寄存器)进行二进制 AND 运算,然后通过将新的掩码存储到 IRQEnableClear 寄存器中来清除位。

现在可以通过清除 cpsr 中的 i 位来启用 IRQ 异常。

最后,处理程序需要通过修改寄存器 r11(其中仍包含最高优先级中断)和 pc 来跳转到正确的服务例程。将寄存器 r11 左移两位(乘以四),并将其加到 pc 上,使处理程序可以通过直接加载服务例程的地址到 pc 中来跳转到正确的例程。

跳转表必须跟随加载PC指令。在跳转表和操作PC指令之间有一个NOP指令,因为PC将指向两条指令之后(或八个字节)。优先级屏蔽表按照中断源位的顺序排列。每个中断服务例程(ISR)都遵循相同的入口风格。下面是针对timer1中断服务例程的示例。

在上面的头部之后插入ISR。完成ISR后,必须重置中断源并将控制传递回被中断的任务。

处理程序在重新打开中断之前必须禁用IRQs。现在可以将外部中断恢复到其原始值,这是可能的,因为服务例程没有修改寄存器r12,所以它仍然包含原始值。

为了返回到被中断的任务,恢复上下文,并将原始SPSR复制回SPSR_IRQ。

优先级简单中断处理程序总结:

-

处理具有优先级的中断。

-

低中断延迟。

-

优点:确定性的中断延迟,因为首先确定优先级级别,然后在屏蔽较低优先级中断后调用服务例程。

-

缺点:处理低优先级服务例程的时间与处理高优先级服务例程的时间相同。

9.3.5 Prioritized Standard Interrupt Handler

延续优先级简单中断处理程序,下一个处理程序增加了一层复杂性。优先级简单中断处理程序通过测试所有中断来确定最高优先级,这是一种效率低下的确定优先级的方法,但它具有确定性,因为每个中断优先级确定所需的时间相同。

另一种方法是在确定最高优先级中断时尽早跳转(见图9.13),即在确定优先级后立即设置PC并进行跳转。这意味着针对优先级标准中断处理程序的代码中的识别部分比优先级简单中断处理程序更复杂。该识别部分将确定优先级,并立即跳转到一个处理低优先级中断屏蔽的例程,然后通过跳转表再次跳转到适当的ISR。

示例9.12:

优先级标准中断处理程序的起始部分与优先级简单中断处理程序相同,但是会更早地拦截具有更高优先级的中断。寄存器r14被赋予指向中断控制器基地址,并将中断控制器状态寄存器的值加载到寄存器r10中。为了使处理程序可以重定位,将PC指向的当前地址记录到寄存器r11中。

bash

I_Bit

EQU 0x80

PRIORITY_0 EQU 2

; Comms Rx

PRIORITY_1 EQU 1

; Comms Tx

PRIORITY_2 EQU 0

; Timer 1

PRIORITY_3 EQU 3

; Timer 2

BINARY_0

EQU 1 << PRIORITY_0 ; 1 << 2 0x00000004

BINARY_1

EQU 1 << PRIORITY_1 ; 1 << 1 0x00000002

BINARY_2

EQU 1 << PRIORITY_2 ; 1 << 0 0x00000001

BINARY_3

EQU 1 << PRIORITY_3 ; 1 << 3 0x00000008

MASK_3

EQU BINARY_3

MASK_2

EQU MASK_3+BINARY_2

MASK_1

EQU MASK_2+BINARY_1

MASK_0

EQU MASK_1+BINARY_0

ic_Base

EQU 0x80000000

IRQStatus EQU 0x0

IRQRawStatus EQU 0x4

IRQEnable EQU 0x8

IRQEnableSet EQU 0x8

IRQEnableClear EQU 0xc

IRQ_Handler ; instruction

state : comment

SUB r14, r14, #4

; 2 : r14_irq -= 4

STMFD r13!, {r14}

; 2 : save r14_irq

MRS r14, spsr

; 2 : copy spsr_irq

STMFD r13!,{r10,r11,r12,r14} ; 2 : save context

LDR r14, =ic_Base

; 3 : int crtl addr

LDR r10, [r14, #IRQStatus] ; 3 : load IRQ status

MOV r11, pc

; 4 : copy pc

TST r10, #BINARY_0

; 5 : if CommRx

BLNE disable_lower

; 5 : then branch

TST r10, #BINARY_1

; 5 : if CommTx

BLNE disable_lower

; 5 : then branch

TST r10, #BINARY_2

; 5 : if Timer1

BLNE disable_lower

; 5 : then branch

TST r10, #BINARY_3

; 5 : if Timer2

BLNE disable_lower

; 5 : then branch

disable_lower

SUB r11, r14, r11

; 5 : r11=r14-copy of pc

LDR r12,=priority_table ; 5 : priority table

LDRB r11,[r12,r11,LSR #3] ; 5 : mem8[tbl+(r11 >> 3)]

ADR r10, priority_masks ; 5 : priority mask

LDR r10, [r10,r11,LSL #2] ; 5 : load mask

LDR r14, =ic_Base

; 6 : int crtl addr

LDR r12, [r14,#IRQEnable] ; 6 : IRQ enable reg

AND r12, r12, r10

; 6 : AND enable reg

STR r12, [r14,#IRQEnableClear] ; 6 : disable ints

MRS r14, cpsr

; 7 : copy cpsr

BIC r14, r14, #I_Bit

; 7 : clear I-bit

MSR cpsr_c, r14

; 7 : enable IRQ

LDR pc, [pc, r11, LSL#2] ; 8 : jump to an ISR

NOP

;

DCD service_timer1

; timer1 ISR

DCD service_commtx

; commtx ISR

DCD service_commrx

; commrx ISR

DCD service_timer2

; timer2 ISR

priority_masks

DCD MASK_2

; priority mask 2

DCD MASK_1

; priority mask 1

DCD MASK_0

; priority mask 0

DCD MASK_3

; priority mask 3

priority_table

DCB PRIORITY_0

; priority 0

DCB PRIORITY_1

; priority 1

DCB PRIORITY_2

; priority 2

DCB PRIORITY_3

; priority 3

ALIGN现在可以通过比较最高优先级和最低优先级来测试中断源。第一个与中断源匹配的优先级确定传入中断的优先级,因为每个中断都有预设的优先级。一旦匹配成功,处理程序就可以跳转到屏蔽低优先级中断的例程。

为了禁用相同或更低优先级的中断,处理程序进入一个例程,首先使用寄存器r11和链接寄存器r14中的基地址计算优先级级别。在SUB指令之后,寄存器r11将包含值4、12、20或28。这些值对应于中断的优先级乘以8再加上4。然后将寄存器r11除以8并加上优先级表的地址。LDRB指令执行后,寄存器r11将等于其中一个优先级中断号(0、1、2或3)。

可以使用左移两位的技术将优先级掩码确定为寄存器r10加上的值,该值包含优先级掩码的地址。中断控制器的基地址被复制到寄存器r14_irq中,并用于获取控制器中的IRQEnable寄存器并将其放入寄存器r12中。寄存器r10包含新的掩码。下一步是使用此掩码清除低优先级中断,方法是对掩码和r12(IRQEnable寄存器)执行二进制AND并将结果存储到IRQEnableClear寄存器中。现在可以通过清除cpsr中的i位来启用IRQ异常。

最后,处理程序需要通过修改r11(仍包含最高优先级中断)和pc来跳转到正确的服务例程。将寄存器r11左移两位(将r11乘以4)并将其添加到pc中,使处理程序能够通过直接将服务例程的地址加载到pc中跳转到正确的例程。跳转表必须跟随加载pc的指令。跳转表和修改pc的LDR指令之间有一个NOP,因为pc指向前两个指令(或八个字节)。

请注意,优先级掩码表按照中断位顺序排列,优先级表按照优先级顺序排列。

总结:优先级标准中断处理程序

-

相对于低优先级中断,处理高优先级中断的时间更短。

-

中断延迟较低。

-

优点:对待高优先级中断更加紧急,无需重复设置外部中断掩码的代码。

-

缺点:由于该处理程序需要进行两次跳转,因此会有一定的时间损耗,每次跳转时都会清空流水线。

9.3.6 Prioritized Direct Interrupt Handler

优先级直接中断处理程序和优先级标准中断处理程序之间的一个区别是,一些处理过程被移到了各个中断服务例程(ISR)中。这些移动的代码用于屏蔽低优先级中断。每个ISR都必须根据特定优先级屏蔽低优先级中断,该优先级可以是一个固定的数字,因为优先级已经在之前确定过了。

第二个区别是,优先级直接中断处理程序直接跳转到相应的ISR。每个ISR在修改cpsr重新启用中断之前负责禁用低优先级中断。这种类型的处理程序相对简单,因为屏蔽是由各个ISR完成的,但是由于每个中断服务例程实际上执行相同的任务,会有一小部分代码重复。

例如,bit_x定义将中断源与中断控制器中的位位置相关联,在ISR内部帮助屏蔽低优先级中断。保存上下文后,需要将ISR表的基地址加载到寄存器r12中。一旦为中断源确定了优先级,该寄存器将用于跳转到正确的ISR。

bash

I_Bit

EQU 0x80

PRIORITY_0 EQU 2

; Comms Rx

PRIORITY_1 EQU 1

; Comms Tx

PRIORITY_2 EQU 0

; Timer 1

PRIORITY_3 EQU 3

; Timer 2

BINARY_0 EQU 1 << PRIORITY_0

; 1 << 2 0x00000004

BINARY_1 EQU 1 << PRIORITY_1

; 1 << 1 0x00000002

BINARY_2 EQU 1 << PRIORITY_2

; 1 << 0 0x00000001

BINARY_3 EQU 1 << PRIORITY_3

; 1 << 3 0x00000008

MASK_3 EQU BINARY_3

MASK_2 EQU MASK_3+BINARY_2

MASK_1 EQU MASK_2+BINARY_1

MASK_0 EQU MASK_1+BINARY_0

ic_Base EQU 0x80000000

IRQStatus EQU 0x0

IRQRawStatus EQU 0x4

IRQEnable EQU 0x8

IRQEnableSet EQU 0x8

IRQEnableClear EQU 0xc

bit_timer1 EQU 0

bit_commtx EQU 1

bit_commrx EQU 2

bit_timer2 EQU 3

IRQ_Handler ; instruction

comment

SUB r14, r14, #4

; r14_irq-=4

STMFD r13!, {r14}

; save r14_irq

MRS r14, spsr

; copy spsr_irq

STMFD r13!,{r10,r11,r12,r14} ; save context

LDR r14, =ic_Base

; int crtl addr

LDR r10, [r14, #IRQStatus] ; load IRQ status

ADR r12, isr_table

; obtain ISR table

TST r10, #BINARY_0

; if CommRx

LDRNE pc, [r12, #PRIORITY_0 << 2] ; then CommRx ISR

TST r10, #BINARY_1

; if CommTx

LDRNE pc, [r12, #PRIORITY_1 << 2] ; then CommTx ISR

TST r10, #BINARY_2

; if Timer1

LDRNE pc, [r12, #PRIORITY_2 << 2] ; then Timer1 ISR

TST r10, #BINARY_3

; if Timer2

LDRNE pc, [r12, #PRIORITY_3 << 2] ; then Timer2 ISR

B service_none

isr_table

DCD service_timer1

; timer1 ISR

DCD service_commtx

; commtx ISR

DCD service_commrx

; commrx ISR

DCD service_timer2

; timer2 ISR

priority_masks

DCD MASK_2

; priority mask 2

DCD MASK_1

; priority mask 1

DCD MASK_0

; priority mask 0

DCD MASK_3

; priority mask 3

...

service_timer1

MOV r11, #bit_timer1

; copy bit_timer1

LDR r14, =ic_Base

; int ctrl addr

LDR r12, [r14,#IRQEnable] ; IRQ enable register

ADR r10, priority_masks ; obtain priority addr

LDR r10, [r10,r11,LSL#2] ; load priority mask

AND r12, r12, r10

; AND enable reg

STR r12, [r14, #IRQEnableClear] ; disable ints

MRS r14, cpsr

; copy cpsr

BIC r14, r14, #I_Bit

; clear I-bit

MSR cpsr_c, r14

; enable IRQ

<rest of the ISR>优先级中断是通过首先检查最高优先级中断,然后逐级向下检查来确定的。一旦确定了优先级中断,pcis将被加载为相应ISR的地址。间接地址存储在isr_table的地址加上优先级级别向左移动两位(乘以四)的位置。或者您可以使用条件分支指令BNE。

ISR跳转表isr_table按照最高优先级中断在表的开头排序。

service_timer1条目展示了优先级直接中断处理程序中使用的ISR的示例。每个ISR都是独特的,取决于特定的中断源。

中断控制器的基地址的副本被放入寄存器r14_irq中。这个地址加上一个偏移量用于将IRQEnable寄存器复制到寄存器r12中。

优先级屏蔽表的地址需要被复制到寄存器r10中,以便用于计算实际屏蔽的地址。寄存器r11向左移动两个位置,得到一个偏移量为0、4、8或12。偏移量加上优先级屏蔽表的地址用于将屏蔽加载到寄存器r10中。优先级屏蔽表与前一节中的优先级中断处理程序相同。

寄存器r10将包含ISR屏蔽,寄存器r12将包含当前屏蔽。使用二进制AND操作将两个屏蔽合并。然后使用新的屏蔽配置中断控制器,使用IRQEnableClear寄存器。现在可以通过清除cpsr中的i位来安全地启用IRQ异常。

处理程序可以继续服务当前的中断,除非发生了一个优先级更高的中断,这种情况下该中断将优先于当前的中断。■

总结:优先级直接中断处理程序

■ 在较短时间内处理高优先级中断。直接跳转到特定的ISR。

■ 中断延迟低。

■ 优点:使用单个跳转,节省宝贵的周期进入ISR。

■ 缺点:每个ISR都需要设置外部中断屏蔽机制,以防止低优先级中断中断当前ISR,这会为每个ISR增加额外的代码。

9.3.7 Prioritized Grouped Interrupt Handler

最后,优先级分组中断处理程序与其他优先级中断处理程序不同,因为它设计用于处理大量的中断。这是通过将中断分组并形成一个子集来实现的,然后可以为该子集分配一个优先级级别。

嵌入式系统的设计者必须识别出每个中断源的子集,并为该子集分配一个群组优先级级别。在选择中断源的子集时要小心,因为群组可以决定系统的特性。将中断源进行分组可以降低处理程序的复杂性,因为不需要扫描每个中断来确定优先级级别。如果优先级分组中断处理程序设计良好,它将显著提高整个系统的响应时间。

示例 9.14

此处理程序被设计为具有两个优先级分组。计时器源被分组到群组0中,通信源被分组到群组1中(见表9.11)。群组0中断的优先级高于群组1中断。

bash

I_Bit

EQU 0x80

PRIORITY_0 EQU 2

; Comms Rx

PRIORITY_1 EQU 1

; Comms Tx

PRIORITY_2 EQU 0

; Timer 1

PRIORITY_3 EQU 3

; Timer 2

BINARY_0 EQU 1 << PRIORITY_0 ; 1 << 2 0x00000004

BINARY_1 EQU 1 << PRIORITY_1 ; 1 << 1 0x00000002

BINARY_2 EQU 1 << PRIORITY_2 ; 1 << 0 0x00000001

BINARY_3 EQU 1 << PRIORITY_3 ; 1 << 3 0x00000008

GROUP_0 EQU BINARY_2|BINARY_3

GROUP_1 EQU BINARY_0|BINARY_1

GMASK_1 EQU GROUP_1

GMASK_0 EQU GMASK_1+GROUP_0

MASK_TIMER1 EQU GMASK_0

MASK_COMMTX EQU GMASK_1

MASK_COMMRX EQU GMASK_1

MASK_TIMER2 EQU GMASK_0

ic_Base EQU 0x80000000

IRQStatus EQU 0x0

IRQRawStatus EQU 0x4

IRQEnable EQU 0x8

IRQEnableSet EQU 0x8

IRQEnableClear EQU 0xc

interrupt_handler

SUB r14, r14,#4

; r14_irq-=4

STMFD r13!, {r14}

; save r14_irq

MRS r14, spsr

; copy spsr_irq

STMFD r13!, {r10,r11,r12,r14} ; save context

LDR r14, =ic_Base

; int ctrl addr

LDR r10, [r14, #IRQStatus] ; load IRQ status

ANDS r11, r10, #GROUP_0 ; belong to GROUP_0

ANDEQS r11, r10, #GROUP_1 ; belong to GROUP_1

AND r10, r11, #0xf

; mask off top 24-bit

ADR r11, lowest_significant_bit ; load LSB addr

LDRB r11, [r11, r10]

; load byte

B disable_lower_priority ; jump to routine

lowest_significant_bit

; 0 123456789abcdef

DCB 0xff,0,1,0,2,0,1,0,3,0,1,0,2,0,1,0

disable_lower_priority

CMP r11, #0xff

; if unknown

BEQ unknown_condition

; then jump

LDR r12, [r14, #IRQEnable] ; load IRQ enable reg

ADR r10, priority_mask ; load priority addr

LDR r10, [r10, r11, LSL #2] ; mem32[r10+r11 << 2]

AND r12, r12, r10

; AND enable reg

STR r12, [r14, #IRQEnableClear] ; disable ints

MRS r14, cpsr

; copy cpsr

BIC r14, r14, #I_Bit

; clear I-bit

MSR cpsr_c, r14

; enable IRQ ints

LDR pc, [pc, r11, LSL #2] ; jump to an ISR

NOP

DCD service_timer1

; timer1 ISR

DCD service_commtx

; commtx ISR

DCD service_commrx

; commrx ISR

DCD service_timer2

; timer2 ISR

priority_mask

DCD MASK_TIMER1

; mask GROUP 0

DCD MASK_COMMTX

; mask GROUP 1

DCD MASK_COMMRX

; mask GROUP 1

DCD MASK_TIMER2

; mask GROUP 0GROUP_x定义通过对二进制模式进行二进制OR操作将各种中断源分配到它们的特定优先级级别。GMASK_x定义为分组中断分配掩码。MASK_x定义将每个GMASK_x连接到特定的中断源,然后可以在优先级掩码表中使用。

在保存上下文后,中断处理程序使用中断控制器基地址的偏移量加载IRQ状态寄存器。

然后,处理程序通过对源进行二进制AND操作来确定中断源所属的组别。指令后缀字母S表示更新cpsr中的条件标志。

现在,寄存器r11将包含最高优先级的组别0或1。处理程序现在通过与0xf进行二进制AND操作来屏蔽其他中断源。

最低有效位表的地址随后加载到寄存器r11中。使用寄存器r10中的值(0、1、2或3,参见表9.12)从表的起始位置加载一个字节。

一旦最低有效位位置加载到寄存器r11中,处理程序将跳转到一个例程。

disable_lower_priority中断例程首先检查是否存在虚拟中断(不再存在)。如果中断是虚拟的,则调用unknown_condition例程。然后,处理程序加载IRQEnable寄存器,并将结果放入寄存器r12中。

通过加载优先级掩码表的地址,可以找到优先级掩码,然后将寄存器r11中的数据左移两位。将结果(0、4、8或12)加到优先级掩码地址上。寄存器r10然后包含一个屏蔽,用于禁止提升较低优先级组中断。

下一步是使用屏蔽来清除较低优先级中断,通过在寄存器r10和r12(IRQEnable寄存器)中进行二进制AND操作,然后将结果保存到IRQEnableClear寄存器中以清除位。此时,通过在cpsr中清除i位,现在可以安全地启用IRQ异常。

最后,处理程序通过修改寄存器r11(仍包含最高优先级中断)和pc来跳转到正确的中断服务例程。通过将寄存器r11左移两位并将结果加到pc上,确定ISR的地址。然后将此地址直接加载到pc中。请注意,跳转表必须在LDR指令之后。

由于ARM流水线的存在,NOP指令是必要的。

总结:优先分组中断处理程序

-

机制:处理按不同优先级分组的中断。

-

低中断延迟。

-

优点:在嵌入式系统需要处理大量中断时非常有用,同时减少了响应时间,因为确定优先级级别的过程较短。

-

缺点:确定如何将中断分组在一起。

9.3.8 VIC PL190 Based Interrupt Service Routine

为了充分利用向量中断控制器,必须修改IRQ向量入口。

0x00000018 LDR pc,[pc,#-0xff0] ; IRQ pc=mem32[0xfffff030]

这条指令从内存映射位置0xffffff030加载一个ISR地址到pc寄存器中,绕过任何软件中断处理程序,因为可以直接从硬件中获取中断源。它还减少了中断延迟,因为只有一个跳转到特定的ISR。

这里是VIC服务例程的一个示例:

bash

INTON

EQU 0x0000

; enable interrupts

SYS32md EQU 0x1f

; system mode

IRQ32md EQU 0x12

; IRQ mode

I_Bit

EQU 0x80

VICBaseAddr EQU 0xfffff000 ; addr of VIC ctrl

VICVectorAddr EQU VICBaseAddr+0x30 ; isr address of int

vector_service_routine

SUB r14,r14,#4

; r14-=4

STMFD r13!, {r0-r3,r12,r14} ; save context

MRS r12, spsr

; copy spsr

STMFD r13!,{r12}

; save spsr

<clear the interrupt source>

MSR cpsr_c, #INTON|SYS32md ; cpsr_c=ift_sys

<interrupt service code>

MSR cpsr_c, #I_Bit|IRQ32md ; cpsr_c=Ift_irq

LDMFD r13!, {r12}

; restore (spsr_irq)

MSR spsr_cxsf, r12 ; restore spsr

LDR r1,=VICVectorAddr ; load VectorAddress

STR r0, [r1]

; servicing complete

LDMFD r13!, {r0-r3,r12,pc}ˆ ; return该例程在清除中断源之前保存了上下文和spsr_irq。完成后,可以通过清除i位重新启用IRQ异常,并将处理器模式设置为系统模式。然后,服务例程可以在系统模式下处理中断。

完成后,通过设置i位禁用IRQ异常,并将处理器模式切换回IRQ模式。

spsr_irq从IRQ堆栈中恢复,准备好返回到被中断的任务。

然后,服务例程将写入控制器中的VICVectorAddr寄存器。向该地址写入表示优先级硬件已处理完中断。

请注意,由于VIC基本上是一个硬件中断处理程序,在激活之前必须预先将ISR地址数组编程到VIC中。

9.4 Summary

异常改变了指令的正常顺序执行。ARM处理器有七种异常:数据终止异常、快速中断请求异常、中断请求异常、预取终止异常、软件中断异常、复位异常和未定义指令异常。每个异常都有一个关联的处理器模式。当引发异常时,处理器进入特定模式并跳转到向量表中的一个条目。每个异常也有一个优先级级别。

中断是一种特殊类型的异常,由外部设备引起。IRQ异常用于一般操作系统活动。FIQ异常通常保留给单个中断源。中断延迟是从外部中断请求信号引发到特定中断服务例程(ISR)的第一条指令被提取之间的时间间隔。

我们介绍了八种中断处理方案,从非嵌套的简单中断处理程序,用于处理和服务单个中断,到高级的优先级分组中断处理程序,用于处理分组成不同优先级级别的中断。

Chapter10 Firmware

本章讨论基于ARM的嵌入式系统的固件。 因为它通常是在新平台上移植和执行的第一个代码,所以固件是任何嵌入式系统的重要组成部分。 固件可以从完整的软件嵌入式系统到简单的初始化和引导加载程序例程不等。 我们将本章分为两个部分。

第一部分介绍固件。 在本节中,我们定义固件术语并描述了可用于ARM处理器的两种流行行业标准固件包:ARM固件套件和Red Hat的RedBoot。 这些固件包是通用的,可以相对容易和快速地移植到不同的ARM平台上。

第二部分仅关注初始化和引导加载程序过程。 为了帮助处理这个问题,我们开发了一个名为Sandstone的简单示例。 Sandstone旨在初始化硬件、将映像加载到存储器中并将pc的控制权移交给该映像。

我们首先讨论固件,介绍两种常见的ARM固件软件包。

10.1 Firmware and Bootloader

我们意识到工程师之间对术语的使用可能会有所不同,但我们将使用以下定义:

-

固件(firmware)是一种深度嵌入、低级软件,提供硬件和应用程序/操作系统级软件之间的接口。它驻留在只读存储器中,在嵌入式硬件系统通电时执行。固件可以在系统初始化后保持活动状态,并支持基本的系统操作。选择用于特定ARM-based系统的固件取决于具体的应用程序,可能涉及从加载和执行复杂操作系统到简单地将控制权移交给小型微内核。因此,从一个固件实现到另一个固件实现,要求可能差异很大。例如,一个小型系统可能仅需要最少的固件支持来引导一个小型操作系统。固件的主要目的之一是提供一个稳定的机制来加载和引导操作系统。

-

引导加载程序(bootloader)是一个小型应用程序,用于将操作系统或应用程序安装到硬件目标上。引导加载程序仅存在于操作系统或应用程序执行的时候,并且通常包含在固件中。

为了帮助理解不同固件实现的特点,我们有一个常见的执行流程(见表10.1)。现在对每个阶段进行更详细的讨论。

第一阶段是设置目标平台,也就是为引导操作系统准备环境,因为操作系统在操作之前需要特定类型的环境。这个步骤涉及确保平台被正确初始化(例如,确保特定微控制器的控制寄存器位于已知地址或将内存映射更改为预期的布局)。

在同一个可执行文件上运行不同的核心和平台是常见的情况。在这种情况下,固件必须识别和发现它正在运行的确切核心和平台。通常通过读取协处理器15中的寄存器0来识别核心,该寄存器保存处理器类型和制造商名称。有多种方法可以识别平台,从检查一组特定外设的存在到简单地读取预编程芯片。

诊断软件提供了一种快速识别基本硬件故障的实用方法。由于这种软件的特性,它往往针对特定的硬件设备进行优化。

调试能力以模块或监视器的形式提供,为在硬件目标上运行的代码提供软件调试支持。该支持包括以下内容:

-

在RAM中设置断点。断点允许程序中断并检查处理器核心的状态。

-

列出和修改内存(使用peek和poke操作)。

-

显示当前处理器寄存器的内容。

-

将内存反汇编为ARM和Thumb指令助记符。

这些都是交互式功能:可以通过命令行解释器(CLI)或连接到目标平台的专用主机调试器发送命令。

除非固件可以访问内部的硬件调试电路,否则只能通过软件调试机制对RAM映像进行调试。

CLI通常在高级固件实现中可用。它允许您通过在命令提示符处键入命令来更改要引导的操作系统的默认配置。对于嵌入式系统,CLI通常通过主机终端应用程序进行控制。主机和目标之间的通信通常通过串口或网络连接进行。

第二阶段是对硬件进行抽象化。硬件抽象层(HAL)是一个软件层,通过提供一组定义的编程接口来隐藏底层硬件。当切换到新的目标平台时,这些编程接口保持不变,但底层实现会发生变化。例如,两个目标平台可能使用不同的计时器外设。每个外设都需要新的代码来初始化和配置设备。尽管硬件和软件在实现之间可能有很大差异,但HAL编程接口保持不变。

与特定硬件外设通信的HAL软件称为设备驱动程序。设备驱动程序提供一个标准的应用程序编程接口(API),用于读取和写入特定外设。

第三阶段是加载可引导映像。固件执行此操作的能力取决于用于存储映像的介质类型。请注意,并非所有操作系统映像或应用程序映像都需要复制到RAM中。操作系统映像或应用程序映像可以直接从ROM中执行。

ARM处理器通常用于包含闪存ROM的小型设备。常见的功能是简单的闪存ROM文件系统(FFS),允许存储多个可执行映像。

其他媒体设备,如硬盘,则需要固件具有适用于访问硬件的设备驱动程序。访问硬件需要固件了解底层文件系统格式,这使得固件能够读取文件系统,找到包含映像的文件,并将映像复制到内存中。同样,如果映像在网络上,则固件还必须了解网络协议以及以太网硬件。

加载过程必须考虑映像格式。最基本的映像格式是纯二进制格式。纯二进制映像不包含任何标头或调试信息。 ARM系统常用的映像格式是可执行和链接格式(ELF)。该格式最初是为UNIX系统开发的,取代了旧格式称为通用对象文件格式(COFF)。 ELF文件有三种形式:可重定位文件、可执行文件和共享对象。

大多数固件系统必须处理可执行格式。加载ELF映像涉及解密标准ELF标头信息(即执行地址、类型、大小等)。映像也可能被加密或压缩,在这种情况下,加载过程将涉及对映像执行解密或解压缩。

第四个阶段是放弃控制权。这是固件将平台控制权交给操作系统或应用程序的地方。请注意,并非所有固件都放弃控制权;相反,固件可以继续成为平台上的控制软件。设计用于将控制权传递给操作系统的固件,在操作系统获得控制权后可能变得不活动。或者,固件的机器无关层(MIL)或硬件抽象层(HAL)部分可以保持活动状态。该层通过SWI机制公开特定硬件设备的标准应用程序接口。

在ARM系统上放弃控制意味着更新向量表并修改pc。更新向量表涉及修改特定异常和中断向量,以便它们指向专门的操作系统处理程序。必须修改pc,以便它指向操作系统入口点地址。

对于更复杂的操作系统,例如Linux,放弃控制需要向内核传递一个标准数据结构。此数据结构解释内核将运行的环境。例如,一个字段可能包括平台上可用的RAM量,而另一个字段包括正在使用的MMU类型。

我们使用这些定义来描述两个常见的固件套件。

10.1.1 ARM Firmware Suite

ARM开发了一个名为ARM固件套件(AFS)的固件包。AFS专门为基于ARM的嵌入式系统设计。它支持多种板卡和处理器,包括英特尔XScale和StrongARM处理器。这个套件包括两个主要技术:一个名为μHAL(读作"micro-HAL")的硬件抽象层和一个名为Angel的调试监视器。

μHAL提供了一个低级设备驱动框架,可以通过不同的通信设备(例如USB、以太网或串口)进行操作。它还提供了一个标准API。因此,在进行移植时,各种硬件特定部分必须根据μHAL API函数来实现。

这样做的好处是移植过程相对简单,因为你有一个标准的函数框架可以使用。一旦固件移植完成,就可以开始将操作系统移植到新的目标平台上。这个过程的速度取决于操作系统是否利用了移植的μHAL API调用来访问硬件。

μHAL支持以下主要功能:

-

系统初始化:设置目标平台和处理器核心。根据目标平台的复杂性,这可能是一个简单或复杂的任务。

-

轮询串行驱动程序:用于与主机进行基本通信的方法。

-

LED支持:允许控制LED以提供简单的用户反馈。这使得应用程序能够显示操作状态。

-

定时器支持:允许设置周期性中断。对于需要这种机制的抢占式上下文切换操作系统来说,这是必需的。

-

中断控制器:支持不同的中断控制器。

μHAL中的引导监视器包含一个CLI。

第二项技术是Angel,它允许主机调试器与目标平台之间进行通信。它允许您检查和修改内存、下载和执行映像、设置断点,并显示处理器寄存器内容。所有这些控制都通过主机调试器进行。Angel调试监视器必须可以访问SWI和IRQ或FIQ向量。

Angel使用SWI指令提供一组API,允许程序打开、读取和写入主机文件系统。IRQ/FIQ中断用于与主机调试器进行通信。

10.1.2 Red Hat RedBoot

RedBoot是由Red Hat开发的固件工具。它在开放源代码许可下提供,没有版税或预付费用。RedBoot旨在在不同的CPU上执行(例如ARM、MIPS、SH等)。它提供了通过GNU调试器(GDB)进行调试的功能,同时还具备引导加载程序的功能。RedBoot软件核心基于一个HAL。

RedBoot支持以下主要功能:

-

通信:配置可以通过串口或以太网进行。对于串口,使用X-Modem协议与GNU调试器(GDB)进行通信。对于以太网,使用TCP与GDB进行通信。RedBoot支持一系列网络标准,如bootp、telnet和tftp。

-

Flash ROM存储器管理:提供了一组文件系统例程,可以下载、更新和擦除Flash ROM中的映像。此外,这些映像可以是压缩或非压缩的。

-

完整的操作系统支持:支持加载和引导嵌入式Linux、Red Hat eCos和许多其他流行的操作系统。对于嵌入式Linux,RedBoot支持定义在引导时直接传递给内核的参数的能力。

10.2 Example: Sandstone

我们设计Sandstone成为一个最小系统。它只执行以下任务:设置目标平台环境、将可引导映像加载到内存中并将控制权交给操作系统。然而,它仍然是一个真正的工作示例。

实现是针对ARM Evaluator-7T平台的,其中包括一个ARM7TDMI处理器。这个示例向你展示了如何设置一个简单的平台,并将软件负载加载到内存中进行引导。这个负载可以是应用程序或操作系统映像。Sandstone是一个静态设计,在构建过程完成后无法配置。表10.2列出了Sandstone的基本特性。

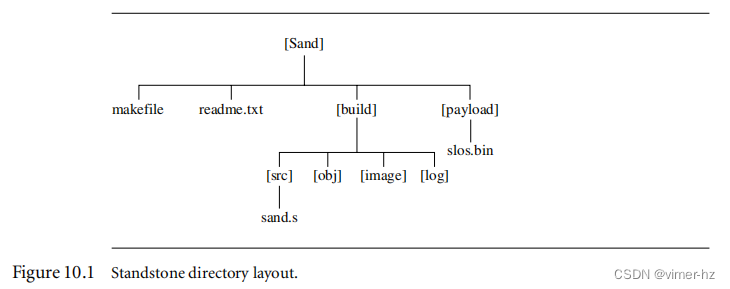

我们将为你介绍目录布局和代码结构。目录布局展示了源代码的位置以及不同的构建文件所放置的位置。代码结构更注重实际的初始化和引导过程。

请注意,Sandstone完全使用ARM汇编语言编写,是一个可用于初始化目标硬件并在ARM Evaluator-7T上合理范围内引导任何软件的工作代码。

10.2.1 Sandstone Directory Layout

你可以在我们的网站上找到Sandstone。如果你查看Sandstone,你会发现目录结构如图10.1所示。这个结构遵循一个标准的风格,在后续的章节中我们会继续使用。

Sandstone的源文件sand.s位于sand/build/src目录下。

汇编器生成的目标文件放置在build/obj目录下。然后将目标文件链接起来,最终的Sandstone映像放置在sand/build/image目录下。这个映像包括了Sandstone代码和负载。负载映像,也就是由Sandstone加载和引导的映像,位于sand/payload目录下。

关于Sandstone构建过程的信息,请查看sand目录下的readme.txt文件。该文件描述了如何为ARM Evaluator-7T构建示例二进制映像。

10.2.2 Sandstone Code Structure

Sandstone由一个单独的汇编文件组成。文件结构被分解为多个步骤,每个步骤对应Sandstone执行流程中的一个阶段(参见表10.3)。

我们将带你逐步了解这些步骤,尽量避免平台特定的部分。但你应该注意到,有些特定部分是不可避免的(例如,配置系统寄存器和内存重映射)。

Sandstone的初始目标是设置目标平台环境,以便能够提供某种形式的反馈,表明固件正在运行并控制平台。

10.2.2.1 Step 1: Take the Reset Exception

执行从复位异常开始。在默认的向量表中,只需要复位向量入口。这是被执行的第一条指令。从这里的代码可以看出,除了复位向量外,所有的向量都会跳转到一个唯一的虚拟处理程序------一个导致无限循环的跳转指令。假设在Sandstone运行过程中不会发生任何异常或中断。复位向量用于将执行流程转移到第二阶段。

bash

AREA start,CODE,READONLY

ENTRY

sandstone_start

B sandstone_init1 ; reset vector

B ex_und ; undefined vector

B ex_swi ; swi vector

B ex_pabt ; prefetch abort vector

B ex_dabt ; data abort vector

NOP ; not used...

B int_irq ; irq vector

B int_fiq ; fiq vector

ex_und B ex_und ; loop forever

ex_swi B ex_swi ; loop forever

ex_dabt B ex_dabt ; loop forever

ex_pabt B ex_pabt ; loop forever

int_irq B int_irq ; loop forever

int_fiq B int_fiq ; loop foreversandstone_start位于地址0x00000000。

执行步骤1的结果如下:

-

虚拟处理程序已设置完成。

-

控制权被传递给初始化硬件的代码。

10.2.2.2 Step 2: Start Initializing the Hardware

初始化硬件的主要阶段是设置系统寄存器。在访问硬件之前,必须设置这些寄存器。例如,ARM Evaluator-7T拥有一个七段显示器,我们选择将其用作反馈工具,以指示固件处于活动状态。在设置段显示器之前,我们必须将系统寄存器的基地址定位到已知位置。在这种情况下,我们选择了默认地址0x03ff0000,因为这样可以将所有硬件系统寄存器与ROM和RAM分离开来,区分外设和存储器。

因此,所有微控制器内存映射寄存器都位于0x03ff0000的偏移量处。这通过以下代码实现:

bash

sandstone_init1

LDR r3, =SYSCFG ; where SYSCFG=0x03ff0000

LDR r4, =0x03ffffa0

STR r4, [r3]寄存器r3包含默认的系统寄存器基地址,并用于设置新的默认地址,以及其他特定属性,如缓存。寄存器r4包含新的配置。其中,高16位包含新系统寄存器基地址0x03ff的高位地址,低16位包含新的属性设置0xffa0。

设置完系统寄存器基地址后,可以配置段显示器。段显示器硬件用于显示Sandstone的进展。请注意,由于它是硬件特定的,因此不会显示段显示器。

执行步骤2的结果如下:

-

系统寄存器从已知的基地址0x03ff0000被设置。

-

配置了段显示器,以便用于显示进度。

10.2.2.3 Step 3: Remap Memory

硬件初始化的主要活动之一是设置内存环境。Sandstone旨在初始化SRAM并重新映射内存。该过程在系统初始化的早期进行。平台在已知的内存状态下启动,如表10.4所示。

正如您所看到的,当平台上电时,只有闪存ROM被分配了内存映射中的位置。两个SRAM bank(0和1)尚未初始化,因此无法使用。接下来的步骤是引入这两个SRAM bank,并将闪存ROM重新映射到新位置。

//内存包含闪存ROM和SRAM么?

/*内存(Memory)是计算机中用于存储数据和指令的设备。它可以被分为多种类型,包括闪存ROM(Read-Only Memory)和SRAM(Static Random-Access Memory),但内存并不仅限于这两种形式。

闪存ROM是一种非易失性存储器,它用于存储固定的数据和指令,如启动程序、固件和操作系统等。它的内容在断电后仍然能够保持,因此被称为只读存储器。在计算机系统中,闪存ROM通常用于存储固定信息,如引导程序和BIOS(Basic Input/Output System)。

SRAM是一种易失性存储器,它用于临时存储正在被处理的数据和指令。与闪存ROM不同,SRAM的内容在断电后会丢失。SRAM以其高速读写访问和较低的功耗而著称,因此广泛应用于高性能计算机中的高速缓存、寄存器和其他需要快速访问的存储器单元。

除了闪存ROM和SRAM,计算机系统中还存在其他类型的内存,如动态随机访问存储器(DRAM)、扩展内存(Extended Memory)和虚拟内存(Virtual Memory)等。每种类型的内存都具有特定的特点和用途,用于满足不同的存储需求。

总之,内存包含多种类型的存储器,其中闪存ROM用于存储固定信息,而SRAM用于临时存储正在处理的数据和指令。

*/

可以使用以下代码实现:

bash

LDR r14, =sandstone_init2

LDR r4, =0x01800000 ; new flash ROM location

ADD r14, r14, r4

ADRL r0, memorymaptable_str

LDMIA r0, {r1-r12}

LDR r0, =EXTDBWTH

; =(SYSCFG + 0x3010)

STMIA r0, {r1-r12}

MOV pc, r14

; jump to remapped memory

sandstone_init2

; Code after sandstone_init2 executes @ +0x1800000代码的第一部分计算了 sandstone_init2 过程的绝对地址,该地址在重新映射之前由 Sandstone 用于跳转到新的重新映射环境中的下一个过程。第二部分执行内存重新映射操作。新的内存映射数据从 memorymaptable_str 指向的结构中加载到寄存器 R1-R12 中。然后,使用这些寄存器将该结构写入系统配置寄存器偏移量为 0x3010 的内存控制器中。完成后,新的内存映射如表10.5所示生效。您可以看到,SRAM bank 现在可用,并且闪存ROM设置为较高的地址。最后一部分是跳转到固件的下一个过程或阶段。通过利用 ARM 流水线,实现了这个跳转。即使新的内存环境已经生效,下一条指令已经加载到流水线中。可以通过将寄存器 R14(即 sandstone_init2 的地址)的内容移动到 PC 寄存器来调用下一个过程。我们可以在重新映射代码之后立即用一条 MOV 指令实现这个目的。执行第3步骤的结果如下:

-

内存已按照表10.5所示进行了重新映射。

-

PC 现在指向下一步。该地址位于新的重新映射闪存ROM中。

10.2.2.4 Step 4: Initialize Communication Hardware

通信初始化包括配置串口并输出标准的横幅信息。该横幅用于显示固件已经完全功能并且内存已经成功重新映射。由于在 ARM Evaluator-7T 上初始化串口的代码是与硬件相关的,因此在这里没有展示。

串口被设置为9600波特率、无奇偶校验、一位停止位和无流控。如果串口电缆连接到板子上,则主机终端必须使用这些设置进行配置。

执行第4步骤的结果如下:

-

串口已初始化:9600波特率、无奇偶校验、一位停止位和无流控。

-

Sandstone横幅通过串口发送出去:

bash

Sandstone Firmware (0.01)

- platform ......... e7t

- status ........... alive

- memory ........... remapped

+ booting payload ...10.2.2.5 Step 5: Bootloader---Copy Payload and Relinquish Control

最后一个阶段涉及将有效负载复制并放弃对 PC(程序计数器)的控制权,让其控制所复制的负载。这是通过这里展示的代码实现的。代码的第一部分设置了在块复制中使用的寄存器 R12、R13 和 R14。引导加载程序的代码假定有效负载是一个纯二进制图像,不需要进行解密或解压缩。

bash

sandstone_load_and_boot

MOV r13,#0

; destination addr

LDR r12,payload_start_address ; start addr

LDR r14,payload_end_address ; end addr

_copy

LDMIA r12!,{r0-r11}

STMIA r13!,{r0-r11}

CMP r12,r14

BLT _copy

MOV pc,#0

payload_start_address

DCD startAddress

payload_end_address

DCD endAddress目标寄存器 R13 指向 SRAM 开始处,这里是 0x00000000。源寄存器 R12 指向有效负载的起始位置,源结束寄存器 R14 指向有效负载的末尾。使用这些寄存器将有效负载复制到 SRAM 中。

然后,通过将 PC 强制设置为所复制有效负载的入口地址,让控制权转交给有效负载。对于这个特定的有效负载,入口点是地址 0x00000000。现在,有效负载已经控制了系统。

执行第5步骤的结果如下:

-

有效负载已复制到 SRAM,地址为 0x00000000。

-

控制权已经转交 PC = 0x00000000。

-

系统已经完全启动。

串口输出以下内容:

bash

Sandstone Firmware (0.01)

- platform ......... e7t

- status ........... alive

- memory ........... remapped

+ booting payload ...

Simple Little OS (0.09)

- initialized ...... ok

- running on ....... e7t

e7t:10.3 Summary

本章介绍了固件。我们将固件定义为连接硬件与应用程序或操作系统的低级代码。我们还将引导加载程序定义为将操作系统或应用程序加载到内存中并放弃对 PC 的控制的软件。

我们介绍了 ARM 固件套件和 RedBoot。ARM 固件套件仅适用于基于 ARM 的系统。而 RedBoot 则更通用,可以用于其他非 ARM 处理器。

接下来,我们看了一个名为 Sandstone 的固件示例。Sandstone 初始化硬件,然后按照以下步骤加载和启动图像:

-

处理复位异常。

-

开始初始化硬件;设置系统寄存器的基地址,并初始化段显示硬件。

-

重新映射内存;ROM 地址 = 高地址,SRAM 地址 = 0x00000000。

-

初始化串口上的通信硬件输出。

-

引导加载程序将图像加载到 SRAM,并将控制权转交(PC = 0x00000000)。

现在,我们拥有一个完全初始化的 ARM7TDMI 嵌入式系统。

Chapter11 Embedded Operating Systems

本章讨论了嵌入式操作系统(OS)的实现。由于嵌入式操作系统是为特定目的而设计的,所以在历史上,嵌入式操作系统通常简单、时间受限,并且在有限的内存中运行。随着嵌入式硬件的复杂性增加,这种区别随着时间的推移发生了变化。传统上只存在于台式计算机上的功能,例如虚拟内存,已经迁移到了嵌入式系统领域。

由于这是一个庞大的主题,我们将范围限制在构成嵌入式操作系统的基本组件上。我们还在第10章显示的固件示例基础上进行扩展。

本章分为两部分:第一部分介绍构成嵌入式操作系统的基本组件,并注意与 ARM 处理器相关的问题。第二部分介绍了一个名为 Simple Little Operating System (SLOS) 的示例操作系统。SLOS旨在展示基本组件的实现方式。

11.1 Fundamental Components

一个操作系统由一组常见的低级组件组成,每个组件执行指定的动作。这些组件之间的相互作用和功能确定了特定操作系统的特征。

初始化是操作系统中第一个执行的代码,涉及设置内部数据结构、全局变量和硬件。初始化在固件交出控制权后开始。对于硬件初始化,操作系统设置各种控制寄存器,初始化设备驱动程序,并且如果操作系统支持抢占式,则设置一个周期性的中断。

内存处理涉及设置系统和任务堆栈。堆栈的位置决定了可供任务或系统使用的内存量。通常在操作系统初始化期间确定系统堆栈的位置。设置任务堆栈取决于任务是静态还是动态。

静态任务在构建时定义,并包含在操作系统映像中。对于这些任务,堆栈可以在操作系统初始化期间设置。例如,SLOS 是一个基于静态任务的操作系统。

动态任务在操作系统安装和执行后加载和执行,并不属于操作系统映像的一部分。任务创建时设置堆栈(例如,Linux 中的情况)。内存处理的复杂性因操作系统而异。它取决于多个因素,如所选的 ARM 处理器核心、微控制器的功能以及最终目标硬件的物理内存布局。

例子操作系统 SLOS 在第11.2节中使用了静态内存设计。它只是在微控制器内部配置一组寄存器,并设置堆栈的位置。由于没有动态内存管理的形式,你在其中不会找到 malloc() 和 free() 的实现。这些函数通常在标准的 C 库中找到。

处理中断和异常的方法是操作系统架构设计的一部分。你需要决定如何处理各种异常:数据中止、快速中断请求、中断请求、预取中止、复位和软件中断(SWI)。

并非所有的异常都需要处理程序。例如,如果你有一个不使用 FIQ 中断的目标板,那么就不需要特定的 FIQ 处理程序。为未使用的异常提供一个无限循环作为默认处理程序总是更安全的做法。这种方法使得调试变得容易:当程序中断时,很清楚是被陷入到了特定的处理程序中。它也能保护系统免受意外的异常干扰。

像 SLOS 这样的抢占式操作系统需要一个周期性中断,通常由目标硬件上的计数/定时器设备产生。在初始化阶段,操作系统设置周期性中断的频率。通常是通过将指定的值设置到计数/定时器的内存映射寄存器中来实现。

当计数/定时器启动后,它会开始递减这个值。一旦值达到零,就会触发一个中断。该中断然后由周期性中断的适当中断服务例程(ISR)处理。ISR 首先使用新的起始值重新初始化计数/定时器,然后调用调度程序或其他专门的例程。

相比之下,非抢占式操作系统不需要周期性中断,它将使用不同的技术,例如轮询------对设备状态进行持续检查。如果设备状态发生变化,那么特定的操作可以与特定的状态变化相连接。

调度程序是一个确定下一个要执行的任务的算法。有许多可用的调度算法。其中一个最简单的是循环调度算法------按照固定的循环顺序激活任务。调度算法必须在效率、大小和复杂性之间寻找平衡。

一旦调度程序完成,新旧任务必须通过上下文切换进行交换。上下文切换将处理器中所有旧任务的寄存器保存到一个数据结构中。然后将新任务的数据加载到处理器的寄存器中。(有关此过程的更多详细信息,请参阅第11.2.6节。)

最后一个组件是设备驱动程序框架------操作系统用于在不同硬件外设之间提供一致接口的机制。该框架允许将对特定外设的新支持以标准和简单的方式整合到操作系统中。对于应用程序要访问的特定外设,必须有一个特定的设备驱动程序可用。该框架必须提供一种安全的方法来访问外设(例如,不允许多个应用程序同时访问同一个外设)。

11.2 Example: Simple Little Operating System

我们开发了一个小型操作系统,称为Simple Little Operating System (SLOS)。它展示了之前讨论的基本组件如何在一个完整的操作系统中结合在一起。我们选择了ARM7TDMI作为核心,因为它是ARM家族中最简单的核心。我们使用ARM Developers' Suite version 1.2作为开发环境,以及ARM的Evaluator-7T作为目标板。相对而言,将SLOS修改为其他开发环境下构建应该是相对容易的。SLOS使用了第10章中描述的Sandstone固件来加载和执行。

SLOS是一个抢占式操作系统。定期中断激活一个休眠任务。为了简单起见,所有的任务和设备驱动程序都是静态的,也就是说,在系统运行时它们是在构建时创建的,而不是动态创建的。SLOS还提供了一个设备驱动程序框架,详见第11.2.7节。

SLOS被设计为在没有内存管理单元或保护单元的ARM7TDMI核心上执行。假设内存映射已经由初始化代码配置好了(在本例中是Sandstone,在第10章中有介绍)。要求SRAM位于0x00000000到0x00080000之间,并且基本配置寄存器必须设置为地址0x03ff0000。

SLOS被加载到地址0x00000000,其中向量表位于该地址。这也是进入SLOS的入口点。在固件交出控制权时,重要的是ARM处理器处于SVC模式,因为SVC模式是特权模式,因此允许初始化代码通过访问cpsr来改变模式。我们利用这一点在IRQ和系统模式下设置了堆栈。

在当前配置下,SLOS包括三个任务和两个服务例程。任务1和任务2通过使用二进制信号量提供了一个互斥的示例。实现的两个服务例程是周期定时器(必需的)和一个按键中断(可选的)。任务3通过ARM Evaluator-7T的一个串口提供了一个简单的命令行界面。

SLOS中的每个任务都需要有自己的堆栈。所有的任务都在用户模式下运行,因此一个任务可以读取但不能写入cpsr。任务改变为特权模式的唯一方式是使用SWI指令调用。这是调用设备驱动程序函数的机制,因为设备驱动程序可能需要完全访问cpsr。

cpsr可以在任务中被修改,但只能通过更新条件标志位的指令来间接修改。

11.2.1 SLOS Directory Layout

SLOS可以在我们的网站上的第11章目录下找到。SLOS的目录结构类似于Sandstone固件的布局(见图10.1和11.1)。

在slos/build/src目录下有六个子目录,包含了所有操作系统的源文件。slos/build/src/core目录包含了杂项的实用文件,以及命令行解释器(CLI)源代码。

特定平台的代码存储在以该平台名称命名的目录下。例如,Evaluator-7T的代码存储在e7t目录下。

slos/build/src/e7t/devices目录包含了所有设备驱动程序文件,slos/build/src/e7t/events目录包含了处理服务、异常和中断的文件。

最后,slos/build/src/apps目录包含了特定配置的所有应用程序/任务。例如,对于Evaluator-7T实现,有三个应用程序/任务。

11.2.2 Initialization

SLOS的初始化有三个主要阶段:启动、执行进程控制块(PCB)设置代码和执行C语言初始化代码。启动代码设置FIQ寄存器以及系统、SVC和IRQ模式的堆栈。在接下来的阶段中,设置PCB,其中包含每个任务的状态,包括所有的ARM寄存器。它用于在上下文切换期间存储和恢复任务状态。设置代码将进程控制块设置为初始启动状态。最后的C语言初始化阶段调用设备驱动程序、事件处理程序和周期定时器的初始化例程。完成后,可以调用第一个任务。

控制通过复位向量传递给SLOS。向量复位是存放初始化代码起始地址的内存位置。假设固件将处理器置于SVC模式下,允许操作系统初始化代码完全访问cpsr。第一条操作系统指令将pc加载为初始化代码(coreInitialization)的开始地址。从向量表中可以看到,该指令使用相对于pc的地址的加载指令加载一个字。汇编工具已经根据pc和vectorReset地址之间的差值计算出偏移值。

bash

AREA ENTRYSLOS,CODE,READONLY

ENTRY

LDR pc, vectorReset

LDR pc, vectorUndefined

LDR pc, vectorSWI

LDR pc, vectorPrefetchAbort

LDR pc, vectorDataAbort

LDR pc, vectorReserved

LDR pc, vectorIRQ

LDR pc, vectorFIQ

vectorReset

DCD coreInitialize

vectorUndefined DCD coreUndefinedHandler

vectorSWI

DCD coreSWIHandler

vectorPrefetchAbort DCD corePrefetchAbortHandler

vectorDataAbort DCD coreDataAbortHandler

vectorReserved DCD coreReservedHandler

vectorIRQ

DCD coreIRQHandler

vectorFIQ

DCD coreFIQHandler作为初始化过程的一部分,我们使用了FIQ寄存器来实现低级别的调试系统,如下图所示。这些寄存器用于存储状态信息。但并不总是可以使用FIQ寄存器,因为它们可能被用于其他目的。

bash

bringupInitFIQRegisters

MOV r2,r14

; save r14

BL switchToFIQMode ; change FIQ mode

MOV r8,#0

; r8_fiq=0

MOV r9,#0

; r9_fiq=0

MOV r10,#0

; r10_fiq=0

BL switchToSVCMode ; change SVC mode

MOV pc,r2

; return

coreInitialize

BL bringupInitFIQRegisters下一阶段是设置SVC、IRQ和系统基本堆栈寄存器。对于SVC堆栈来说,这很简单,因为处理器已经处于SVC模式。代码如下所示:

bash

MOV sp,#0x80000

; SVC stack

MSR cpsr_c,#NoInt|SYS32md

MOV sp,#0x40000

; user/system stack

MSR cpsr_c,#NoInt|IRQ32md

MOV sp,#0x9000

; IRQ stack

MSR cpsr_c,#NoInt|SVC32md从代码中可以看出,一旦堆栈设置完毕,处理器将切换回SVC模式,以便继续进行剩余的初始化过程。处于特权模式下允许最后的初始化阶段通过清除I位和将处理器更改为用户模式来取消屏蔽IRQ中断。

执行启动代码的结果如下:

-

低级别调试机制已初始化。

-

SVC、IRQ和系统基本堆栈已设置好。

要启动SLOS运行,必须初始化每个任务的PCB。PCB是一个保留的数据结构,保存了整个ARM寄存器集的副本(参见表11.1)。通过将相应任务的PCB数据复制到处理器寄存器中,可以激活任务。

在发生上下文切换之前,必须设置每个任务的PCB,因为切换会将PCB数据传输到r0至r15寄存器和cpsr中。如果未初始化,上下文切换将在这些寄存器中复制垃圾数据。

有四个主要部分的PCB需要初始化:程序计数器(PC)、链接寄存器(LR)、用户模式堆栈和保存的处理器状态寄存器(也就是r13、r14、r15和spsr)针对每个任务进行初始化。

bash

; void pcbSetUp(void *entryAddr, void *PCB, UINT offset);

pcbSetUp

STR r0,[r1,#-4] ; PCB[-4]=C_TaskEntry

STR r0,[r1,#-64] ; PCB[-64]=C_TaskEntry

SUB r0,sp,r2

STR r0,[r1,#-8] ; PCB[-8]=sp-<offset>

MOV r0,#0x50

; cpsr_c

STR r0,[r1,#-68] ; PCB[-68]=iFt_User

MOV pc,lr为了帮助说明这一点,我们提取了初始化PCB的例程。调用pcbSetUp例程来设置任务2和任务3的PCB。寄存器r0是任务的入口地址------标签entryAddr。这是任务的执行地址。寄存器r1是PCB数据结构的地址------标签pcbAddr。该地址指向一个存储任务PCB的内存块。寄存器r2是堆栈偏移量,用于在内存映射中定位堆栈。需要注意的是,任务1不需要初始化,因为它是第一个要执行的任务。

设置PCB的最后一部分是设置当前任务标识符,调度算法使用该标识符确定要执行的任务。

bash

LDR r0,=PCB_CurrentTask

MOV r1,#0

STR r1,[r0]

LDR lr,=C_Entry

MOV pc,lr ; enter the CEntry world在代码片段的末尾,通过将pc设置为例程的起始地址,调用了第一个C例程------C_Entry。

执行PCB设置代码的结果如下:

-

初始化所有三个任务的PCB。

-

将要执行的当前PCB设置为任务1(标识符为0)。

现在,初始化工作交给了C_Entry()例程,该例程可以在build/src/core/cinit.c文件中找到。C_Entry例程调用另一个例程cinit_init()。这个例程用于初始化设备驱动、服务和周期性中断滴答。这里展示了cinit_init()例程的内容。C代码的设计不需要初始化标准C库,因为它不调用任何标准C库函数,例如printf()、fopen()等。

bash

void cinit_init(void)

{

eventIODeviceInit();

eventServicesInit();

eventTickInit(2);

}函数eventIODeviceInit、eventServicesInit和eventTickInit都被调用以初始化操作系统的各个特定部分。你会注意到,eventTickInit有一个参数,值为2。这用于设置周期性滴答事件之间的毫秒数。

初始化完成后,可以启动周期性定时器,如下所示。这意味着在第一个定时器中断之前需要调用任务1。为了允许周期性事件中断处理器,必须启用IRQ并将处理器置于用户模式。完成这一步骤后,将调用任务1的入口点C_EntryTask1的地址。

cpp

int C_Entry(void)

{

cinit_init();

eventTickStart();

__asm

{

MSR cpsr_c,#0x50

}

C_EntryTask1();

return 0;

}如果一切正常,C_Entry例程末尾的返回语句将永远不会执行。此时,所有初始化工作已经完成,操作系统完全可用。

执行所有C初始化代码的结果如下:

-

设备驱动程序被初始化。

-

服务被初始化。

-

周期性定时器滴答被初始化并启动。

-

cpsr中启用了IRQ中断。

-

处理器被置于用户模式。

-

调用了任务1的入口点(即C_EntryTask1)。

11.2.3 Memory Model

我们采用了一个简单的内存模型来设计SLOS。图11.2显示了SLOS的代码部分,包括任务,位于低地址内存中,而IRQ和每个任务的堆栈位于较高地址内存中。SVC堆栈设置在内存的顶部。内存映射中的箭头表示堆栈增长的方向。

//SVC stack

/*

SVC(Supervisor Call)是一种处理器指令,用于在操作系统内核态(supervisor mode)和用户态(user mode)之间进行切换和通信。当用户程序需要执行特权指令或访问受限资源时,会触发一个SVC异常,将控制权传递给操作系统内核。

在处理SVC异常时,操作系统会使用一个称为SVC堆栈(SVC stack)的数据结构来保存相关的上下文信息。SVC堆栈通常是一个专门的内存区域,用于存储异常处理所需的寄存器值、返回地址和其他相关数据。它位于内核的地址空间中,并且在内核模式下可访问。

*/

11.2.4 Interrupts and Exceptions Handling

在这个操作系统的实现中,实际上只使用了三个异常。其他异常会通过转到特定的虚拟处理程序而被忽略,为了安全起见,这些处理程序被实现为无限循环。在完整的实现中,这些虚拟处理程序应该被替换为完整的处理程序。表11.2展示了这三个异常以及它们在操作系统中的使用方式。

11.2.4.1 Reset Exception

重置只在初始化阶段被调用一次。理论上,它可以被再次调用以重新初始化系统,例如作为响应看门狗定时器事件重置处理器。当系统长时间处于非活动状态时,看门狗定时器用于重置系统。

11.2.4.2 SWI Exception

每当应用程序调用设备驱动程序时,调用会通过SWI处理程序机制进行。SWI指令强制处理器从用户模式切换到SVC模式。

以下是核心的SWI处理程序。处理程序的第一个动作是将寄存器r0到r12保存到SVC堆栈中。

接下来的动作是计算SWI指令的地址,并将该指令加载到寄存器r10中。通过屏蔽掉最高的8位,可以获取SWI号码。然后将SVC堆栈的地址复制到寄存器r1中,并在调用SWI C处理程序时作为第二个参数使用。

接着,将spsr复制到寄存器r2,并存储在堆栈中。这仅在出现嵌套的SWI调用时才需要。然后,处理程序跳转到调用C处理程序例程的代码处。

bash

coreSWIHandler

STMFD sp!,{r0-r12,r14} ; save context

LDR r10,[r14,#-4] ; load SWI instruction

BIC r10,r10,#0xff000000 ; mask off the MSB 8 bits

MOV r1,r13

; copy r13_svc to r1

MRS r2,spsr

; copy spsr to r2

STMFD r13!,{r2}

; save r2 onto the stack

BL swi_jumptable ; branch to the swi_jumptable在BL指令之后的代码如下所示,将返回到调用方程序。这通过从堆栈中还原spsr并重新加载所有用户保留的寄存器,包括pc,来实现。

bash

LDMFD r13!,{r2} ; restore the r2 (spsr)

MSR spsr_cxsf,r2 ; copy r2 back to spsr

LDMFD r13!,{r0-r12,pc}ˆ ; restore context and return链接寄存器在BL指令中已经设置。当SWI C处理程序完成时,执行该代码。

bash

swi_jumptable

MOV r0,r10

; move the SWI number to r0

B eventsSWIHandler ; branch to SWI handler在图11.3中显示的C处理程序eventsSWIHandler以寄存器r0包含的SWI号码和寄存器r1指向存储在SVC堆栈上的寄存器的位置被调用。

11.2.4.3 IRQ Exception

IRQ处理程序比SWI处理程序要简单得多。它作为基本的非嵌套中断处理程序实现。处理程序首先保存上下文,然后将中断控制器状态寄存器INTPND的内容复制到寄存器r0中。然后,每个服务例程将寄存器r0与特定的中断源进行比较。如果源和中断匹配,则调用服务例程;否则,将中断视为幻影中断并忽略。

bash

TICKINT EQU 0x400

BUTTONINT EQU 0x001

eventsIRQHandler

SUB r14, r14, #4

; r14_irq-=4

STMFD r13!, {r0-r3, r12, r14} ; save context

LDR r0,INTPND

; r0=int pending reg

LDR r0,[r0]

; r0=memory[r0]

TST r0,#TICKINT

; if tick int

BNE eventsTickVeneer

; then tick ISR

TST r0,#BUTTONINT

; if button interrupt

BNE eventsButtonVeneer ; then button ISR

LDMFD r13!, {r0-r3, r12, pc}ˆ ; return to task对于已知的中断源,会调用中断修饰程序来处理事件。下面的代码展示了一个定时器修饰程序的示例。从示例中可以看出,修饰程序包括调用两个例程:第一个是重置定时器的eventsTickService(特定于平台的调用),第二个是调用调度器的kernelScheduler,而调度器则会进行上下文切换。

bash

eventsTickVeneer

BL eventsTickService ; reset tick hardware

B kernelScheduler

; branch to scheduler在IRQ堆栈上没有对寄存器r4到r12的要求,因为调度算法和上下文切换处理了所有寄存器的细节。

11.2.5 Scheduler

在SLOS中使用的低级调度器或分发器是一个简单的静态轮转算法,如下的伪代码所示。这里的"静态"表示任务仅在操作系统初始化时创建。在SLOS中,任务既不能在操作系统处于活动状态时创建,也不能被销毁。

cpp

task t=0,t';

scheduler()

{

t' = t + 1;

if t' = MAX_NUMBER_OF_TASKS then

t' = 0 // the first task.

end;

ContextSwitch(t,t')

}如前所述,在初始化阶段,当前活动任务t(PCB_CurrentTask)被设置为0。当周期性的时钟中断发生时,新的任务t'是通过当前任务t加1来计算得到的。如果任务编号等于任务限制(MAX_NUMBER_OF_TASKS),则任务t'将被重置为起始值0。

表11.3列出了调度器使用的标签以及它们在算法中的用法的描述。这些标签用于调度器的以下过程和代码:

-

通过加载PCB_CurrentTask的内容获取当前任务ID。

-

使用PCB_CurrentTask作为索引在PCB_Table中找到当前任务对应的PCB地址。

-

使用第2步获取的地址更新PCB_PtrCurrentTask的值。

-

使用轮转算法计算新的任务t'的ID。

-

将新的任务t'的ID存储到PCB_CurrentTask中。

-

通过使用更新后的PCB_CurrentTask作为索引在PCB_Table中找到下一个任务PCB的地址。

-

将下一个任务PCB存储到PCB_PtrNextTask中。

调度下一个任务t'的代码如下:

bash

MaxNumTasks EQU 3

FirstTask EQU 0

CurrentTask

LDR r3,=PCB_CurrentTask ; [1] r3=PCB_CurrentTask

LDR r0,[r3]

; r0= current Task ID

LDR r1,=PCB_Table ; [2] r1=PCB_Table address

LDR r1,[r1,r0,LSL#2] ; r1=mem32[r1+r0 << 2]

LDR r2,=PCB_PtrCurrentTask ; [3] r2=PCB_PtrCurrentTask

STR r1,[r2]

; mem32[r2]=r1 : task addr

; ** PCB_PtrCurrentTask - updated with the addr of the current task

; ** r2 = PCB_PtrCurrentTask address

; ** r1 = current task PCB address

; ** r0 = current task ID

NextTask

ADD r0,r0,#1

; [4] r0 = (CurrentTaskID)+1

CMP r0,#MaxNumTasks ; if r0==MaxNumTasks

MOVEQ r0,#FirstTask ; then r0 = FirstTask (0)

STR r0,[r3]

; [5] mem32[r3]=next Task ID

LDR r1,=PCB_Table ; [6] r1=PCB_Table addr

LDR r1,[r1,r0,LSL#2] ; r1=memory[r1+r0 << 2]

LDR r0,=PCB_PtrNextTask ; [7] r0=PCB_PtrNextTask

STR r1,[r0]

; memory[r0]=next task addr执行调度器后的结果如下:

* PCB_PtrCurrentTask指向当前活动PCB的地址。

* PCB_PtrNextTask指向下一个活动PCB的地址。

* PCB_CurrentTask存储下一个任务的标识符的值。

11.2.6 Context Switch

利用调度器产生的更新信息,上下文切换将当前活动任务t与下一个任务t'进行交换。为了实现这一点,上下文切换将活动分为两个阶段,如图11.4所示。第一阶段涉及将处理器寄存器保存到由PCB_PtrCurrentTask指向的当前任务t的PCB中。第二阶段从由PCB_PtrNextTask指向的下一个任务t'的PCB中加载寄存器的数据。

//看起来每个task都有对应的PCB

现在我们将带您了解上下文切换的两个阶段的过程和代码,首先详细介绍保存当前上下文的过程,然后再加载新的上下文。

11.2.6.1 Save the Current Context

第一阶段是保存活动任务t的当前寄存器。所有任务都在用户模式下执行,因此必须保存用户模式寄存器。以下是该过程:

-

我们必须从堆栈中恢复寄存器r0到r3和r14。这些寄存器属于当前任务。

-

然后,使用寄存器r13指向当前任务PCB的偏移量为-60的位置。这个偏移量允许两条指令更新整个PCB。

-

第一阶段的最后一个动作是存储所有的用户模式寄存器r0到r14。这可以通过一条指令完成。请记住,符号ˆ表示存储多个指令作用于用户模式寄存器。第二条存储指令保存spsr和返回的链接寄存器。

将寄存器保存到PCB的代码如下:

bash

Offset15Regs EQU 15*4

handler_contextswitch

LDMFD r13!,{r0-r3,r12,r14} ; [1.1] restore registers

LDR r13,=PCB_PtrCurrentTask ; [1.2]

LDR r13,[r13]

; r13=mem32[r13]

SUB r13,r13,#Offset15Regs ; r13-=15*Reg:place r13

STMIA r13,{r0-r14}ˆ

; [1.3] save user mode registers

MRS r0, spsr

; copy spsr

STMDB r13,{r0,r14}

; save r0(spsr) & r14(lr)保存当前上下文的结果如下:

-

IRQ堆栈被重置,并保存到PCB_IRQStack中。

-

任务t的用户模式寄存器被保存到当前PCB中。

11.2.6.2 Load the Next Context

上下文切换的第二阶段涉及将任务t'的PCB转移到用户模式的保护寄存器中。完成后,程序必须将控制权交给新的任务t'。以下是该过程:

-

加载并将寄存器r13定位在新的PCB起始处偏移量为-60的位置。

-

首先加载寄存器spsr和链接寄存器。然后加载下一个任务的寄存器r0到r14。寄存器r14是用户模式的寄存器r14,而不是指令中的ˆ所示的IRQ寄存器r14。

-

然后从PCB_IRQStack中恢复IRQ堆栈。

-

通过将寄存器r14中保存的地址复制到pc,并更新cpsr,来恢复执行新的任务。

从PCB加载寄存器的代码如下:

bash

LDR r13,=PCB_PtrNextTask ; [2.1] r13=PCB_PtrNextTask

LDR r13,[r13]

; r13=mem32[r13] : next PCB

SUB r13,r13,#Offset15Regs ; r13-=15*Registers

LDMDB r13,{r0,r14} ; [2.2] load r0 & r14

MSR spsr_cxsf, r0 ; spsr = r0

LDMIA r13,{r0-r14}ˆ ; load r0_user-r14_user

LDR r13,=PCB_IRQStack ; [2.3] r13=IRQ stack addr

LDR r13,[r13]

; r13=mem32[r13] : reset IRQ

MOVS pc,r14

; [2.4] return to next task加载下一个上下文的结果如下:

-

上下文切换完成。

-

下一个任务的寄存器被加载到用户模式寄存器中。

-

IRQ堆栈被还原为在进入IRQ处理程序之前的原始设置。

11.2.7 Device Driver Framework

设备驱动框架(DDF)使用SWI指令来实现。DDF保护操作系统免受应用程序直接访问硬件的影响,并为任务提供统一的标准接口。为了访问特定设备,任务必须首先获得一个唯一的标识号(UID)。通过调用open宏或eventsIODeviceOpen来实现这一目的。该宏会直接转换成设备驱动的SWI指令。UID用于检查是否有其他任务已经访问了相同的设备。

打开设备驱动的任务代码是:

cpp

device_treestr *host;

UID serial;

host = eventIODeviceOpen(&serial,DEVICE_SERIAL_E7T,COM1);

if (host==0)

{

/* ...error device driver not found...*/

}

switch (serial)

{

case DEVICE_IN_USE:

case DEVICE_UNKNOWN:

/* ...problem with device... */

}该示例展示了使用设备驱动框架打开串行设备。一组宏将参数转换为寄存器r1到r3。然后,这些寄存器通过SWI机制传递给设备驱动函数。在该示例中,只有由r1指向的值,即&serial,实际上被更新。该值用于返回UID。如果返回的值为零,则表示发生了错误。

下面的代码显示了如何将宏eventIODeviceOpen转换为单个SWI指令调用:

bash

PRE

r0 = Event_IODeviceOpen (unsigned int)

r1 = &serial (UID *u)

r2 = DEVICE_SERIAL_E7T (unsigned int major)

r3 = COM1 (unsigned int minor)

SWI 5075

POST

r1 = The data pointed to by the UID pointer is updatedSWI接口被用作在任务在非特权模式下执行时切换到特权模式的方法。这允许设备驱动程序完全访问cpsr。图11.5显示了调用设备驱动函数时实际的模式变化。从图中可以看出,设备驱动程序本身在系统模式下执行(特权模式)。

一旦执行了SWI指令,处理器就会进入SVC模式,并且IRQ中断会自动禁用。只有当处理器切换到系统模式时,中断才会重新启用。唯一的例外是在初始化阶段调用设备驱动函数时,此时中断将保持禁用状态。

11.3 Summary

在ARM处理器上执行的嵌入式操作系统的基本组件如下:

■ 初始化:设置操作系统使用的所有内部变量、数据结构和硬件设备。

■ 内存管理:组织内存以容纳内核及要执行的各种应用程序。

■ 所有中断和异常都需要一个处理程序。对于未使用的中断和异常,必须安装一个虚拟处理程序。

■ 预置定时器:对于抢占式操作系统,需要定期定时器。定时器产生一个中断,导致调度程序被调用。

■ 调度程序:是确定要执行的新任务的算法。

■ 上下文切换:保存当前任务的状态,并加载下一个任务的状态。

这些组件在名为Simple Little Operating System(SLOS)的操作系统中得到了体现:

■ 初始化:设置SLOS的所有功能,包括银行模式堆栈、每个应用程序的进程控制块(PCB)、设备驱动程序等。

■ 内存模型:SLOS内核放置在低内存中,每个应用程序都有自己的存储区域和堆栈。微控制器系统寄存器放置在ROM和SRAM之外。

■ 中断和异常:SLOS仅使用三个事件,分别是Reset、SWI和IRQ。所有其他未使用的中断和异常都有一个虚拟处理程序安装。

■ 调度程序:SLOS实现了一个简单的轮转调度程序。

■ 上下文切换:首先将当前上下文保存到一个PCB中,然后从另一个PCB中加载下一个任务的上下文。

■ 设备驱动框架:这保护操作系统免受应用程序直接访问硬件的影响。

Chapter12 Caches

缓存是位于处理器核心和主内存之间的一种小型、快速的存储器阵列,用于存储最近引用的主内存的部分内容。处理器尽可能使用缓存而不是主内存,以提高系统性能。缓存的目标是减少处理器核心由于慢速内存而产生的内存访问瓶颈。

常与缓存一起使用的是写缓冲区,它是一个非常小的先进先出(FIFO)存储器,位于处理器核心和主内存之间。写缓冲区的目的是解放处理器核心和缓存存储器,使其不受写入主内存的缓慢写入时间的影响。

单词"缓存"是法语,意思是"隐藏的存储空间"。当应用于ARM嵌入式系统时,这个定义非常准确。缓存存储器和写缓冲区硬件添加到处理器核心时被设计为对软件代码执行透明,因此以前编写的软件不需要重新编写以在缓存的核心上使用。缓存和写缓冲区都有额外的控制硬件,自动处理代码和数据在处理器和主内存之间的移动。然而,了解处理器的缓存设计的细节可以帮助您创建在特定ARM核心上运行更快的程序。

由于本章的大部分内容都是关于缓存如何使程序运行更快的精彩事物,所以会产生一个问题:"在系统中使用缓存是否会带来任何缺点?"答案是肯定的。主要的缺点是确定程序的执行时间的困难。为什么这是一个问题,很快就会明显。

由于缓存存储器只占主内存的很小一部分,在程序执行过程中,缓存很快就会填满。一旦满了,缓存控制器会频繁地从缓存存储器中逐出现有的代码或数据,以为新的代码或数据腾出更多空间。这个逐出过程往往是随机发生的,有些数据保留在缓存中,而其他数据则被移除。因此,在任何给定的时刻,一个值可能存储在缓存中,也可能不在。

由于数据可能存在或不存在于缓存中的任何时间点,一个例程的执行时间由于使用直接从缓存内存中读取数据与从主内存加载缓存行之间的时间差异而略有变化。

因此,在这种情况下,我们首先展示缓存在标准内存层次结构中的位置,并介绍引用局部性原理,以解释为什么缓存可以提高系统性能。然后我们概述一般的缓存架构,并定义了一组ARM社区常用的术语。本章最后以示例代码结束,展示如何清除和刷新缓存,并将代码和数据段锁定在缓存中。

12.1 The Memory Hierarchy and Cache Memory

在第一章中,我们介绍了计算机系统中的内存层次结构。图12.1回顾了部分信息,以展示缓存和写缓冲区在层次结构中的位置。

内存层次结构的最内层是处理器核心。这种内存与处理器紧密耦合,在很多方面很难将其视为与处理器分离的部分。这种内存被称为寄存器文件。这些寄存器是处理器核心的一部分,并在系统中提供最快的内存访问。

在主要级别上,内存组件通过专用的芯片内接口连接到处理器核心。在这个级别上,我们可以找到紧密耦合的内存(TCM)和一级缓存。稍后我们会详细讨论缓存。

主存也位于主要级别上。它包括易失性组件,如SRAM和DRAM,以及非易失性组件,如闪存。主存的目的是在系统运行程序时存储这些程序。

下一个级别是辅助存储,即大型、慢速、相对廉价的大容量存储设备,如硬盘驱动器或可移动存储器。此级别还包括来自外围设备的数据,其特点是访问时间极长。辅助存储用于存储不适合主存的非常大的程序的未使用部分以及当前未执行的程序。

值得注意的是,内存层次结构既取决于体系结构设计,也取决于周围的技术。例如,TCM和SRAM都是相同的技术,但在体系结构布局上有所不同:TCM位于芯片上,而SRAM位于电路板上。

缓存可以嵌入到层次结构的任何级别,在内存组件之间存在显著的访问时间差异时。只要存在这样的差异,缓存就可以提高系统性能。缓存存储器系统将存储在较低层次的信息临时移动到较高层次。

图12.1包括一级(L1)缓存和写缓冲区。L1缓存是一组高速芯片内存,临时存放来自较慢层次的代码和数据。缓存存储这些信息以减少访问指令和数据所需的时间。写缓冲区是一个非常小的FIFO缓冲区,支持从缓存向主存进行写操作。

图中没有显示二级(L2)缓存。L2缓存位于L1缓存和较慢的内存之间。L1和L2缓存也被称为一级和二级缓存。

图12.2显示了缓存与主存系统和处理器核心的关系。图的上半部分显示了一个没有缓存的系统的块图。主存由处理器核心直接访问,使用处理器核心支持的数据类型。图的下半部分显示了一个带有缓存的系统。缓存存储器比主存快得多,因此可以快速响应核心的数据请求。缓存与主存的关系涉及在较慢的主存和较快的缓存之间传输小块数据。这些数据块被称为缓存行。写缓冲区充当临时缓冲区,释放缓存存储器中的可用空间。缓存以高速将缓存行传输到写缓冲区,然后写缓冲区以较慢的速度将其传输到主存。

12.1.1 Caches and Memory Management Units

如果有一个带有缓存的核心支持虚拟内存,它可以位于核心和内存管理单元(MMU)之间,或位于MMU和物理内存之间。缓存在MMU之前或之后的放置决定了缓存所在的地址空间以及程序员如何看待缓存存储系统。图12.3显示了这两种缓存之间的差异。

逻辑缓存以虚拟地址空间存储数据。逻辑缓存位于处理器和MMU之间。处理器可以直接从逻辑缓存访问数据,无需经过MMU。逻辑缓存也被称为虚拟缓存。

物理缓存使用物理地址存储内存。物理缓存位于MMU和主存之间。对于处理器访问内存,MMU必须先将虚拟地址转换为物理地址,然后缓存存储器才能向核心提供数据。

带有MMU的ARM缓存核心在ARM7到ARM10系列处理器(包括Intel StrongARM和Intel XScale处理器)中使用逻辑缓存。ARM11处理器系列使用物理缓存。关于MMU操作的更多信息,请参阅第14章。

//ARM11处理器属于ARMv6系列。

缓存提供性能改进的原因是因为计算机程序以非随机方式执行。可预测的程序执行是缓存系统成功的关键。如果程序对内存的访问是随机的,缓存对整体系统性能的改进将很小。参考局部性原理解释了缓存内存对系统性能改进的原因。这个原理指出计算机软件程序经常运行一些小循环代码,反复操作数据内存的局部部分。

在内存中重复使用相同的代码或数据,或者非常接近的代码或数据,是缓存提高性能的原因。当首次访问时,通过将引用的代码或数据加载到更快的内存中,后续的访问将快得多。正是对较快内存的重复访问改善了性能。

缓存在时间和空间上利用了这种重复的局部引用。如果是时间上的引用,则称为时间局部性。如果是地址上的邻近引用,则称为空间局部性。

//ARMv8系列处理器使用的是物理缓存还是逻辑缓存?

ARMv8系列处理器使用的是物理缓存。

12.2 Cache Architecture

ARM处理器在其带有缓存的核心中使用了两种总线架构,分别是冯·诺依曼(Von Neumann)和哈佛(Harvard)。冯·诺依曼和哈佛总线架构在核心和内存之间指令和数据路径的分离上存在差异。为支持这两种架构,使用了不同的缓存设计。

在使用冯·诺依曼架构的处理器核心中,有一个单一的用于指令和数据的缓存。这种类型的缓存被称为统一缓存。统一缓存内存包含了指令和数据值。

哈佛架构通过分离指令和数据总线来提高整个系统的性能,但是支持这两个总线需要两个缓存。在使用哈佛架构的处理器核心中,有两个缓存:指令缓存(I-cache)和数据缓存(D-cache)。这种类型的缓存被称为分离缓存。在分离缓存中,指令存储在指令缓存中,数据值存储在数据缓存中。

我们通过图12.4展示了统一缓存的基本架构来介绍缓存的基本架构。缓存的两个主要元素是缓存控制器和缓存存储器。缓存存储器是一个专用的内存数组,以称为缓存行的单位访问。缓存控制器使用处理器发出的地址的不同部分来选择缓存存储器的部分。我们将首先介绍缓存存储器的架构,然后再详细介绍缓存控制器的细节。

//ARMv8处理器使用的总线架构是冯·诺依曼架构还是哈佛架构?

//应该是分离的哈佛架构

12.2.1 Basic Architecture of a Cache Memory

图12.4的右侧显示了一个简单的高速缓存存储器。它由三个主要部分组成:目录存储区、数据区和状态信息。高速缓存存储器的所有三个部分都存在于每个缓存行中。

高速缓存存储器必须知道缓存行中存储的信息来自主存的哪个位置。它使用目录存储区来保存标识缓存行从主存复制而来的地址。目录条目称为缓存标记。

高速缓存存储器还必须存储从主存读取的数据。这些数据存储在数据区中(参见图12.4)。

高速缓存的大小定义为缓存能够从主存存储的实际代码或数据。不包括在缓存大小内的是支持缓存标记或状态位所需的缓存存储器。

高速缓存存储器中还有状态位以维护状态信息。两个常见的状态位是有效位和脏位。有效位将缓存行标记为活动状态,表示它包含最初来自主存的实时数据,并且当前可供处理器核心按需访问。脏位定义了缓存行是否包含与其在主存中表示的值不同的数据。我们会在第12.3.1节中对脏位进行更详细的说明。

12.2.2 Basic Operation of a Cache Controller

Cache控制器是一种硬件,它自动将代码或数据从主存储器复制到缓存内存。它的任务是自动执行此操作,以使支持的软件无需改变即可在带有缓存和不带缓存的系统上运行。

缓存控制器在将读取和写入内存的请求传递给内存控制器之前拦截这些请求。它通过将请求的地址分成三个字段来处理请求,即标签字段、集合索引字段和数据索引字段。这三个位字段如图12.4所示。

首先,控制器使用地址的集合索引部分来定位可能包含所请求的代码或数据的缓存行。该缓存行包含缓存标签和状态位,控制器使用它们来确定实际存储在其中的数据。

然后,控制器检查有效位以确定缓存行是否活动,并将缓存标签与请求地址的标签字段进行比较。如果状态检查和比较都成功,则为缓存命中。如果状态检查或比较失败,则为缓存未命中。

在缓存未命中的情况下,控制器会将整个缓存行从主存储器复制到缓存内存,并提供所请求的代码或数据给处理器。将缓存行从主存储器复制到缓存内存的过程称为缓存行填充。

在缓存命中的情况下,控制器直接从缓存内存中向处理器提供代码或数据。为此,它继续进行下一步,即使用地址请求的数据索引字段来选择缓存行中的实际代码或数据,并将其提供给处理器。

12.2.3 The Relationship between Cache and Main Memory

了解基本的缓存内存架构和缓存控制器的工作原理,就足够讨论缓存与主存储器之间的关系了。

图12.5显示了主存储器的部分内容临时存储在缓存内存中。该图表示最简单的缓存形式,称为直接映射缓存。在直接映射缓存中,主存储器中的每个地址位置都映射到缓存内存中的一个位置。由于主存储器比缓存内存大得多,因此在主存储器中有很多地址映射到缓存内存中的同一个位置。该图展示了以0x824结尾的地址类别的映射关系。

图中也显示了图12.4中引入的三个位字段。集合索引选择缓存中存储所有以0x824结尾的地址的位置。数据索引选择缓存行中的字/半字/字节,本例中是缓存行中的第二个字。标签字段是与目录存储中的缓存标签值进行比较的地址部分。在这个例子中,每个缓存内存位置对应着主存储器中一百万个可能的位置。在任何给定时间,主存储器的一百万个可能值中只能有一个存在于缓存内存中。标签与缓存标签的比较决定了所请求的数据是否在缓存中,或者表示主存储器中以0x824结尾的另一个位置。

在填充缓存行期间,缓存控制器可能会将加载的数据同时转发给核心,同时将其复制到缓存中;这就是所谓的数据流传输。数据流传输允许处理器在缓存控制器填充缓存行的剩余字时继续执行。

如果该缓存行中存在有效数据,但表示主存储器中的另一个地址块,则整个缓存行将被替换为包含所请求地址的缓存行。作为处理缓存未命中的一部分,删除现有缓存行并替换为包含所请求地址的缓存行的过程称为驱逐(eviction)------将缓存行的内容从缓存返回到主存储器,为需要加载到缓存中的新数据腾出空间。

直接映射缓存是一种简单的解决方案,但它存在一个设计成本,即只有一个位置可用于存储主存储器中的值。直接映射缓存容易受到大量的抖动影响,即在缓存内存中争夺同一位置的软件冲突。抖动的结果是重复加载和替换缓存行。加载和替换是由于程序元素被放置在主存储器中映射到缓存内存中相同缓存行的地址上。

图12.6在图12.5的基础上添加了一个简单的、人为制造的软件过程来演示抖动现象。该过程在一个do-while循环中重复调用两个例程。每个例程具有相同的索引地址;也就是说,这些例程所在的地址在物理内存中映射到缓存内存中的同一位置。在循环的第一次迭代中,例程A在执行时被放置在缓存中。当过程调用例程B时,它会逐个缓存行地将例程A替换出去,同时加载并执行例程B。在第二次循环中,例程A取代了例程B,然后例程B又取代了例程A。反复发生缓存未命中导致了不在运行的例程持续被替换,这就是缓存抖动的情况。

12.2.4 Set Associativity

//组相连

//4路组相连

一些缓存包含一个额外的设计特征,以减少抖动的频率(见图12.7)。这个结构设计特征是将缓存内存分成更小的相等单元,称为路(ways)。图12.7仍然是一个4KB的缓存;然而,集索引现在可以指向多个缓存行,每个路指向一个缓存行。缓存不再是256行的单路,而是由64行的四个路组成。具有相同集索引的四个缓存行被称为同一个集合,这也是"集索引"名称的来源。由集索引指向的缓存行集合被称为关联集。可以将主存中的数据或代码块分配给集中任何一个路中的任意一个,而不会影响程序行为;换句话说,将数据存储在集合内的缓存行中不会影响程序执行。两个连续的主内存块可以作为缓存行存储在同一个路或两个不同的路中。需要注意的重要一点是,来自主内存特定位置的数据或代码块可以存储在属于该集合的任何缓存行中。集合内的值的放置是互斥的,以防止同一代码或数据块同时占用集合中的两个缓存行。

在四路组相联缓存中,主内存到缓存的映射发生了变化。图12.8显示了差异。现在,主内存中的任何一个位置映射到缓存中的四个不同位置。尽管图12.5和图12.8都是4KB的缓存,但有一些值得注意的差异。

标记的位域现在比之前多两位,而集索引的位域减少了两位。这意味着400万个主内存地址现在映射到一个包含四个缓存行的集合,而不是100万个地址映射到一个位置。

映射到缓存的主存区域的大小现在是1KB,而不是4KB。这意味着将缓存行数据块映射到相同集合的可能性现在增加了四倍。这一点可以通过缓存行被驱逐的可能性减少四分之一来抵消。

如果在图12.8所示的四路组相联缓存中运行图12.6中显示的示例代码,抖动的发生频率会很快稳定下来,因为例程A、例程B和数据数组在集合的四个可用位置中可建立了唯一的位置。

/*

例如:

Routine A: 0x000000224

Routine B: 0x000001224

对于直接映射内存来说,Routine B替换Routine A时,必将发生cache miss;

对于四路组相联来说,Routine B替换Routine A时,Routine A的数据如果缓存在四路中的一路,Routine B的数据可以缓存在四路中的另外三路,从而降低cach miss;

*/

12.2.4.1 Increasing Set Associativity

随着缓存控制器的关联度增加,抖动的概率会降低。理想目标是通过设计将任何主内存位置映射到任何缓存行来最大化缓存的关联度。能够实现这一目标的缓存称为全相联缓存。然而,随着关联度的增加,支持它的硬件复杂性也增加。硬件设计师用于增加缓存关联度的一种方法是使用内容可寻址存储器(Content Addressable Memory,CAM)。

CAM使用一组比较器将输入的标记地址与每个有效缓存行中存储的缓存标记进行比较。CAM的工作方式与RAM相反。RAM在给定地址值后产生数据,而CAM在存储器中存在给定数据值时产生一个地址。使用CAM可以同时比较更多的缓存标记,从而增加可以包含在集合中的缓存行数量。在ARM920T和ARM940T处理器核心中,ARM选择使用CAM来定位缓存标记。ARM920T和ARM940T中的缓存是64路组相联的。图12.9显示了ARM940T缓存的框图。缓存控制器将地址标记作为CAM的输入,并且输出选择包含有效缓存行的路。

所请求地址的标记部分被用作同时将输入标记与64个路中存储的所有缓存标记进行比较的四个CAM的输入。如果匹配成功,则缓存数据由缓存内存提供。如果没有匹配,存储器控制器生成一个缺失信号。

控制器使用集索引位启用四个CAM之一。索引的CAM然后在缓存内存中选择一个缓存行,而核心地址的数据索引部分选择所请求的字、半字或字节。

12.2.5 Write Buffers

写缓冲区是一个非常小、快速的FIFO内存缓冲区,临时存储处理器通常要写入主内存的数据。在没有写缓冲区的系统中,处理器直接写入主内存。而在有写缓冲区的系统中,数据以高速写入FIFO,然后再被传输到较慢的主内存。写缓冲区减少了处理器将小块连续数据写入主内存所需的时间。写缓冲区的FIFO位于内存层次结构中与L1缓存相同的级别上,如图12.1所示。

写缓冲区的效率取决于对主内存写入次数与执行的指令数之比。在给定的时间间隔内,如果对主内存的写入次数较低或足够分散于其他处理指令之间,写缓冲区很少会填满。如果写缓冲区没有填满,运行的程序将继续使用缓存内存执行,使用寄存器进行处理,使用缓存内存进行读写,并使用写缓冲区来保存被驱逐的缓存行,直到它们排空到主内存为止。

写缓冲区还改善了缓存性能;这种改善发生在缓存行被驱逐时。如果缓存控制器驱逐了一个脏缓存行,它会将该缓存行写入写缓冲区而不是主内存。因此,新的缓存行数据将更快地可用,并且处理器可以继续从缓存内存中操作。

写入写缓冲区的数据在从写缓冲区传输到主内存之前无法进行读取。同样,被驱逐的缓存行也不能在写缓冲区中进行读取。这是写缓冲区的FIFO深度通常相当小(只有几个缓存行)的原因之一。

一些写缓冲区并不严格遵循FIFO缓冲的原则。例如,ARM10系列支持合并(coalescing),即将写操作合并为一个缓存行。如果它们代表主内存中的同一个数据块,写缓冲区将把新值合并到已存在的缓存行中。合并也称为写合并(write merging)、写折叠(write collapsing)或写组合(write combining)。

//ARMv8处理器支持写缓冲区么?

/*

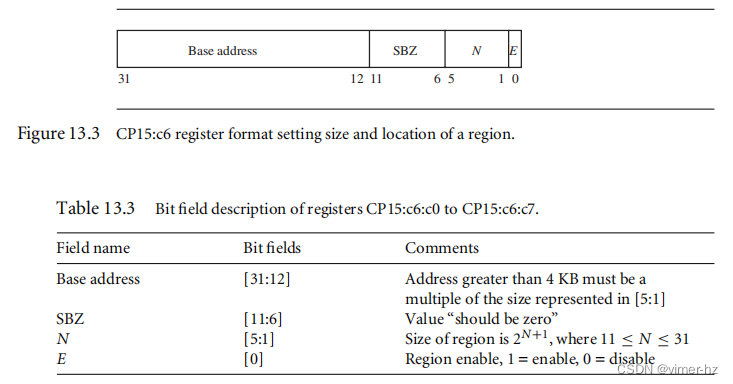

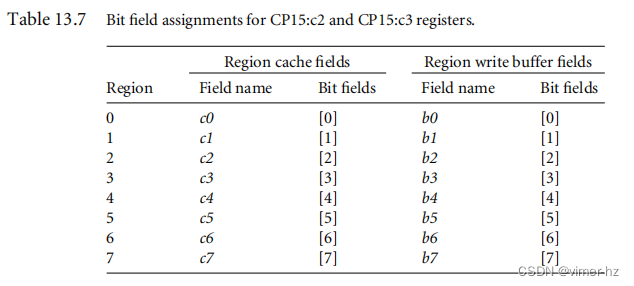

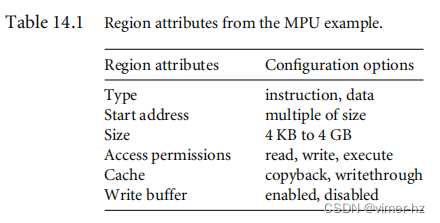

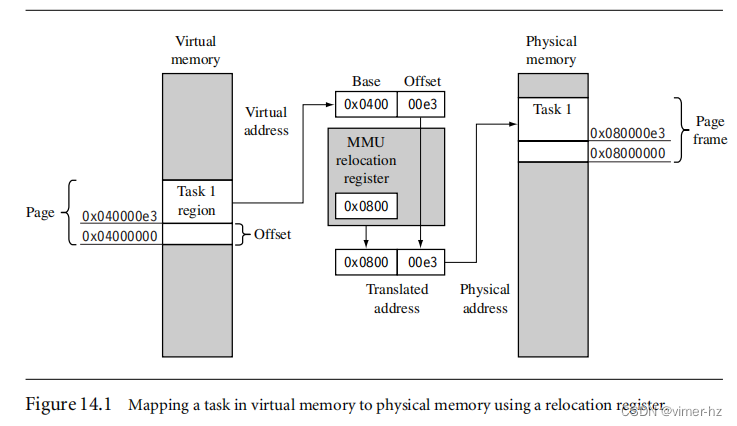

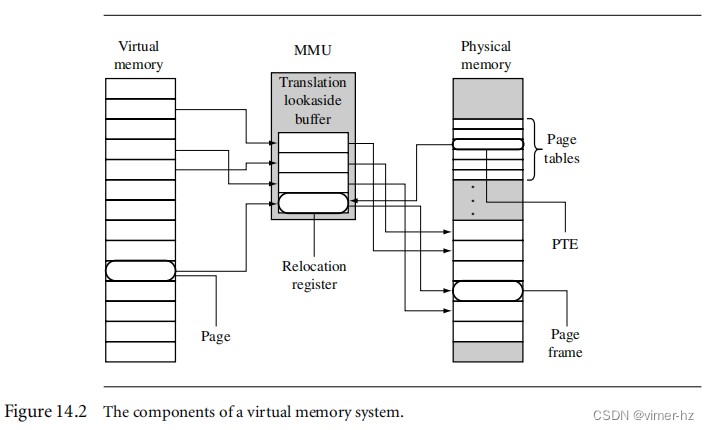

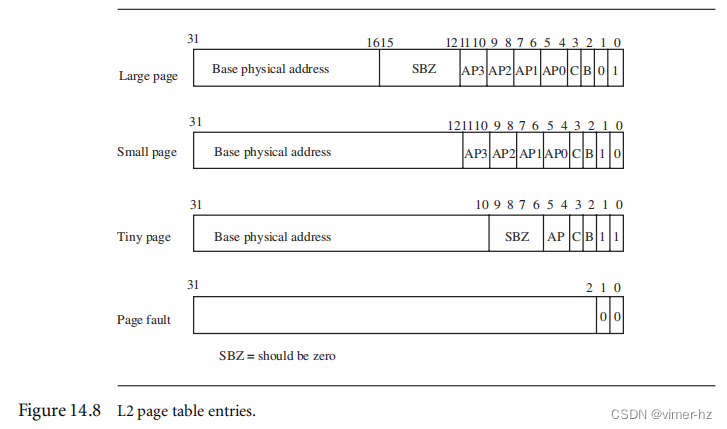

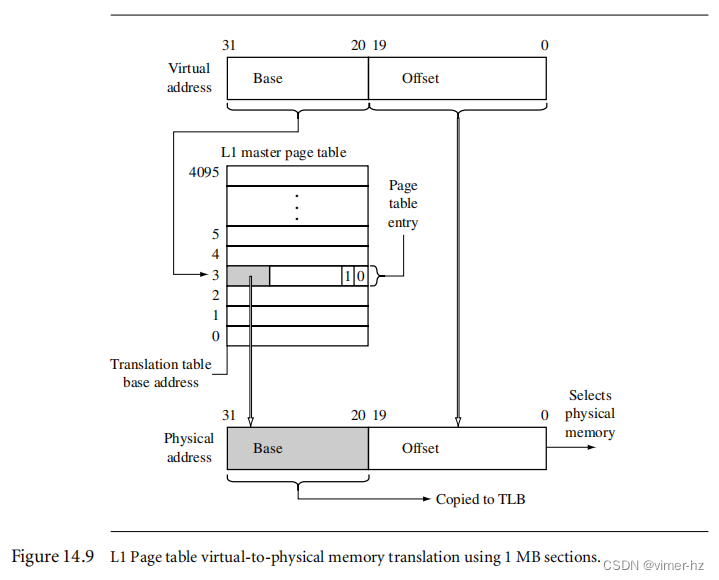

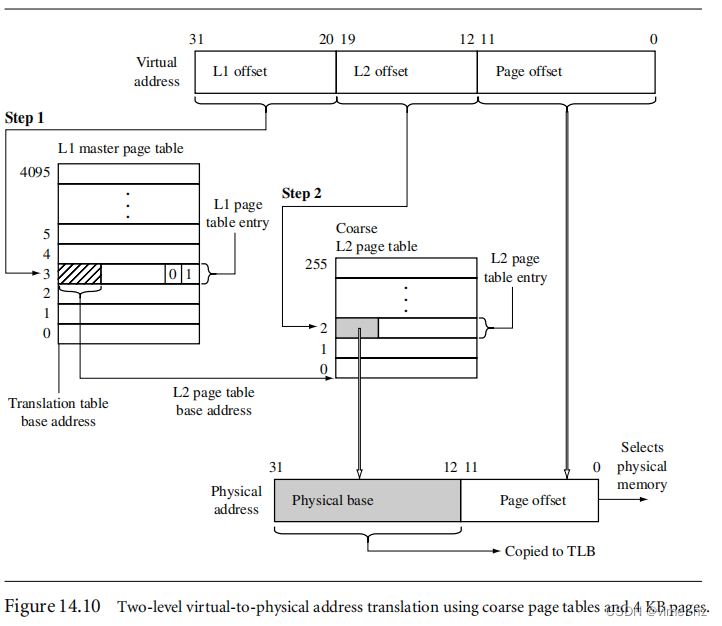

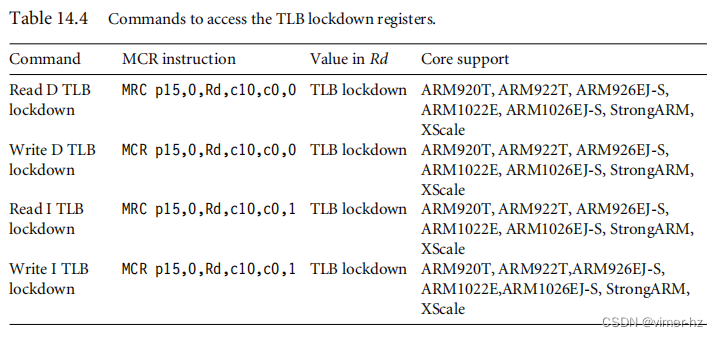

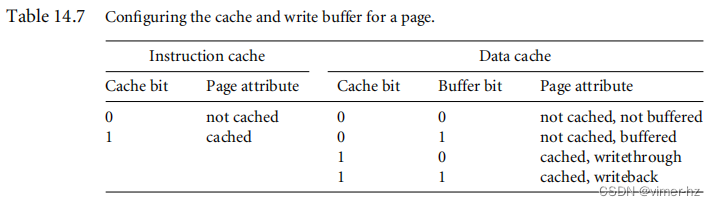

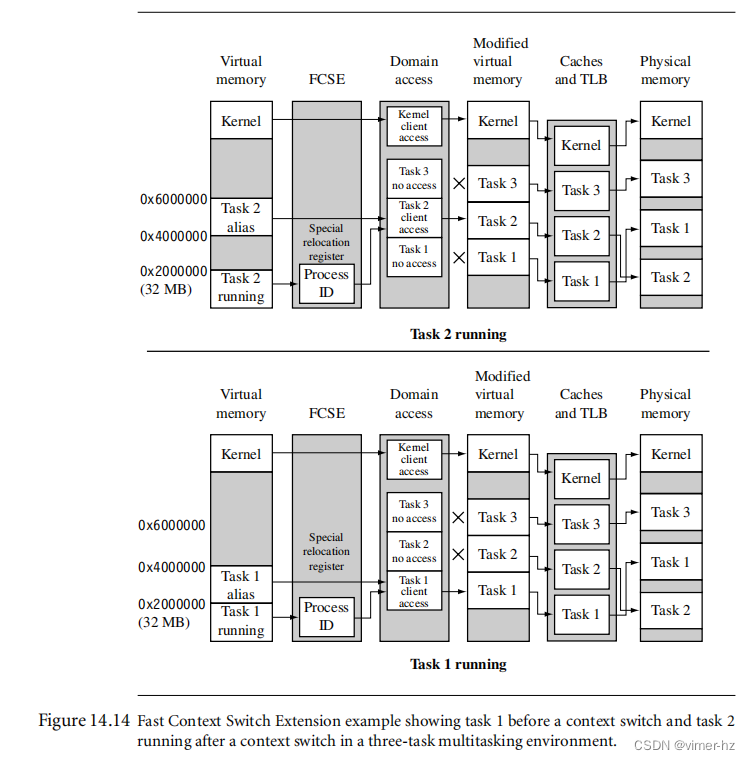

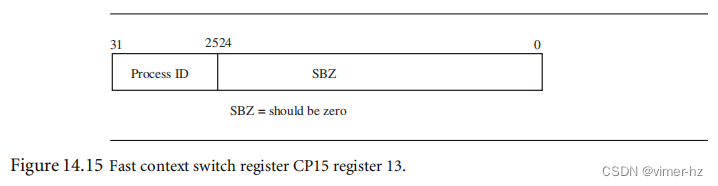

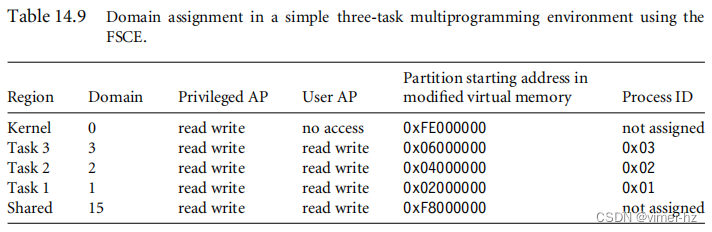

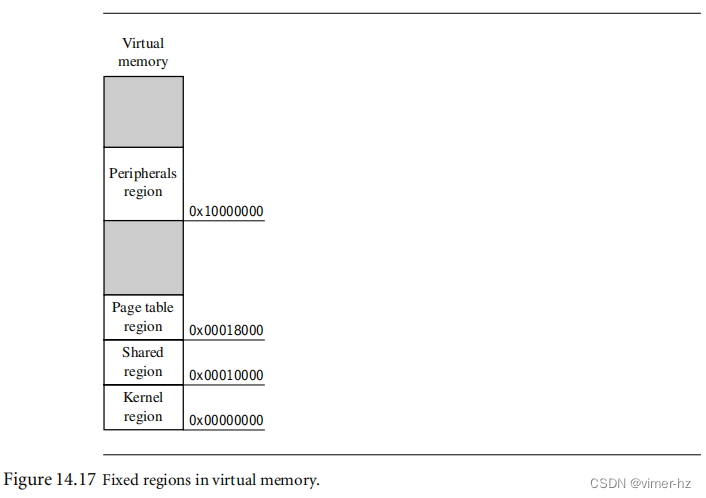

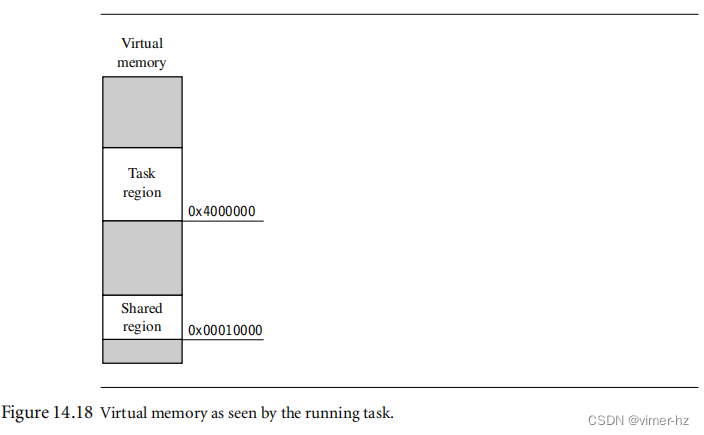

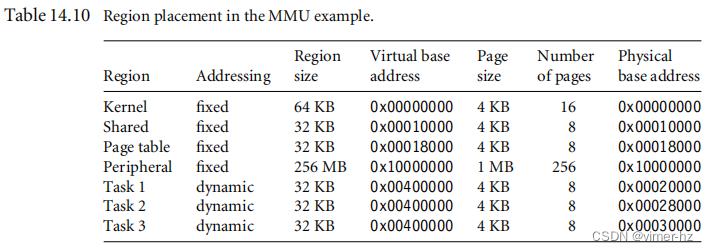

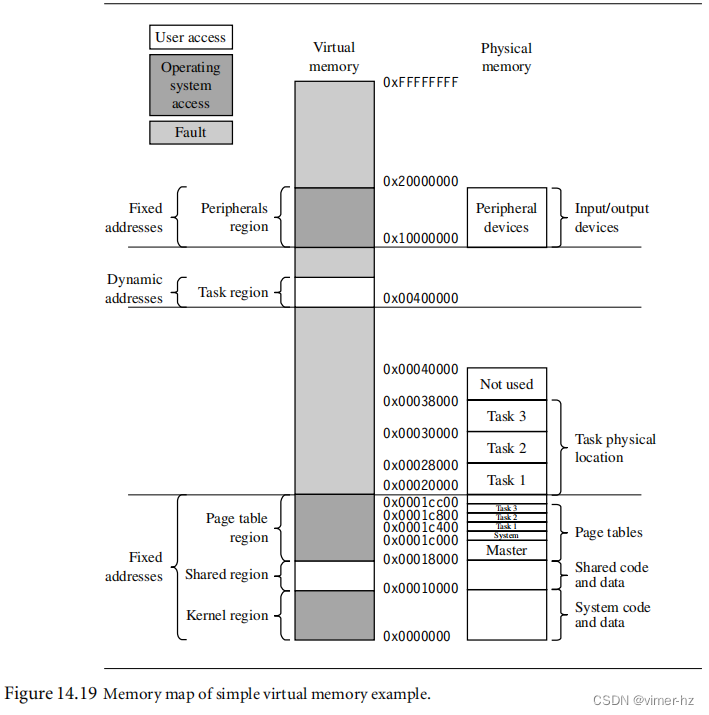

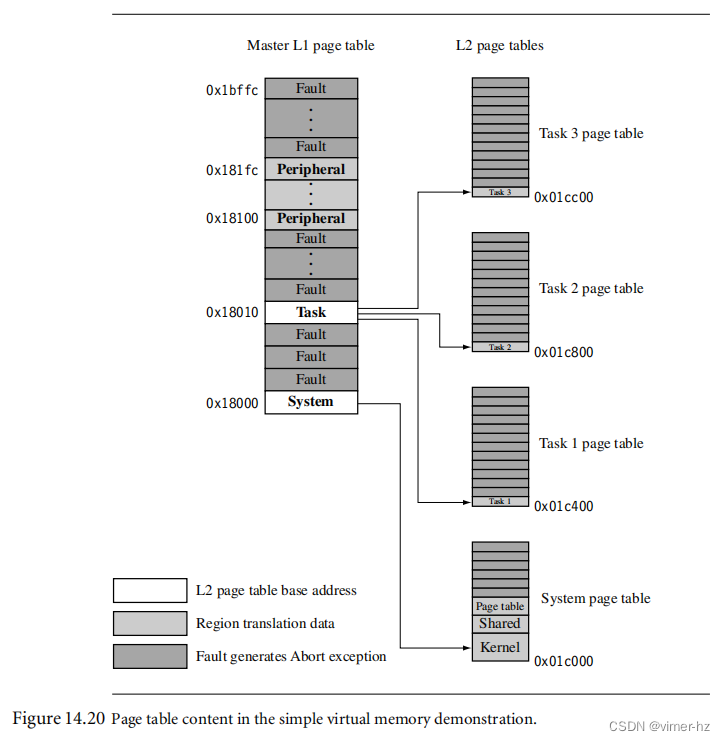

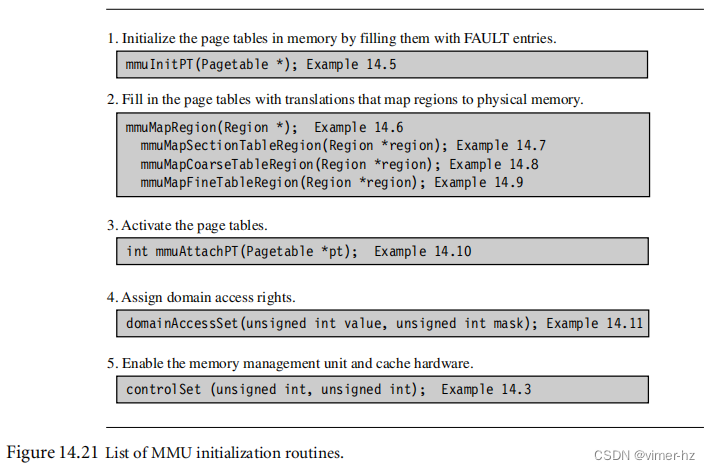

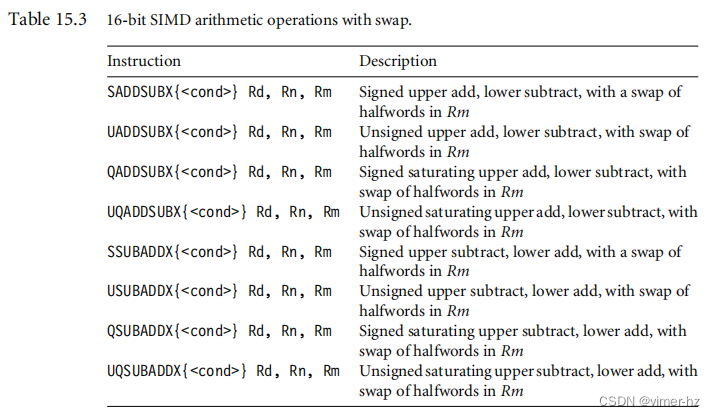

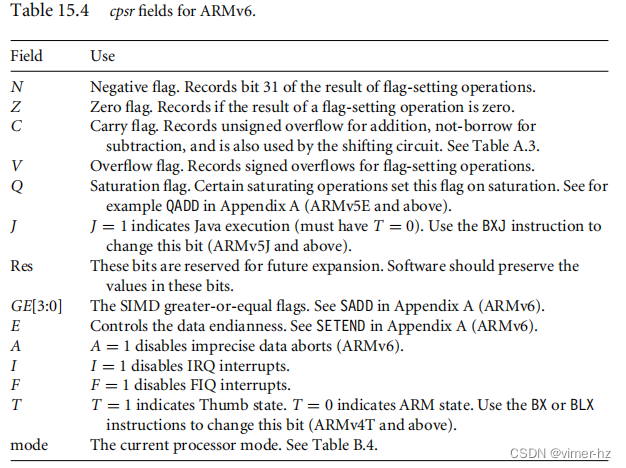

是的,ARMv8处理器也支持写缓冲区。ARMv8架构引入了一种称为Store Buffer的写缓冲区机制。Store Buffer是一个用于暂时存储处理器写入主内存的数据的缓冲区。它可以将数据以高速写入缓冲区,然后再将其传输到较慢的主内存。