在数字音频系统中,I2S(Inter-IC Sound)IP核如同一条高速专用通道,负责在芯片内部或跨芯片间精准传输音频数据流。作为飞利浦于1986年制定的标准协议,I2S已成为现代音频芯片设计的基石。本文将深入解析其技术特点、核心价值及典型应用。

一、I2S IP的核心作用

数字音频的"同步指挥官"

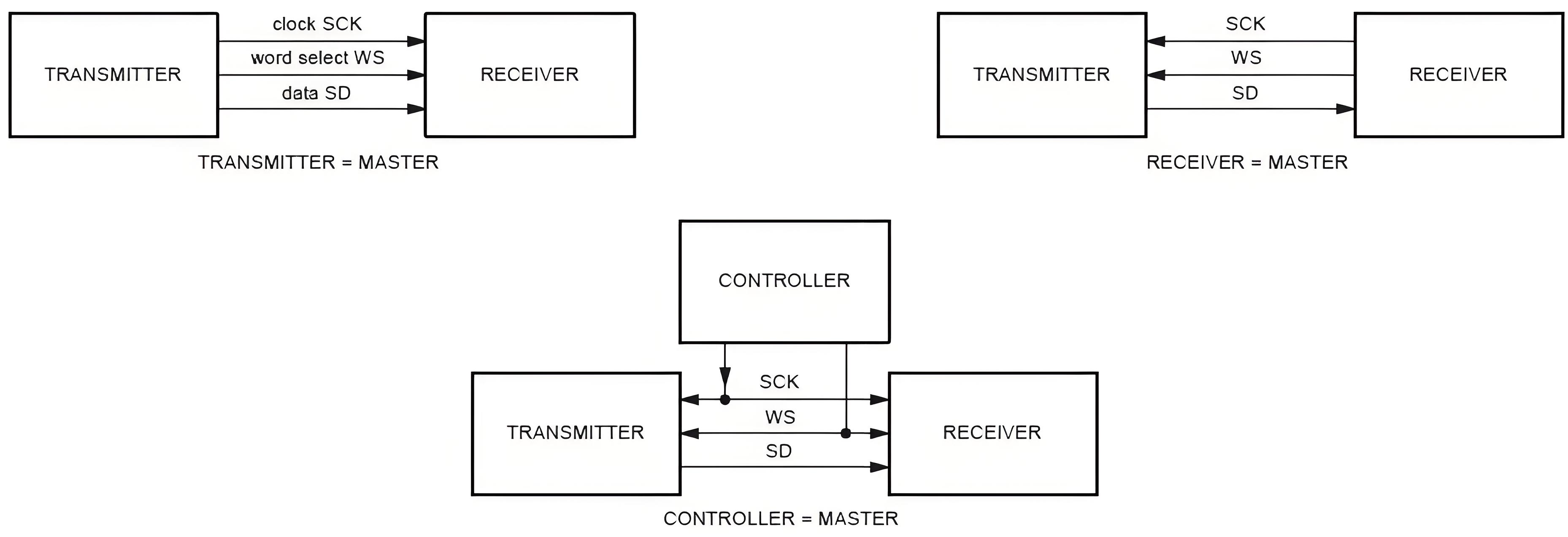

I2S IP核的核心职责是解决音频数据传输的时钟同步问题。传统模拟音频易受干扰,而I2S通过分离时钟(SCK)、数据(SD)和声道选择(WS)三条信号线,实现数据与时钟的严格同步。这种设计避免了信号抖动导致的失真,无需额外抗抖动设备,显著降低系统成本。

多设备协同的"调度中心"

在芯片系统中,I2S IP核协调编解码器(CODEC)、ADC/DAC、DSP等模块的通信。例如:

主控芯片通过I2S向DAC发送解码后的数字音频;

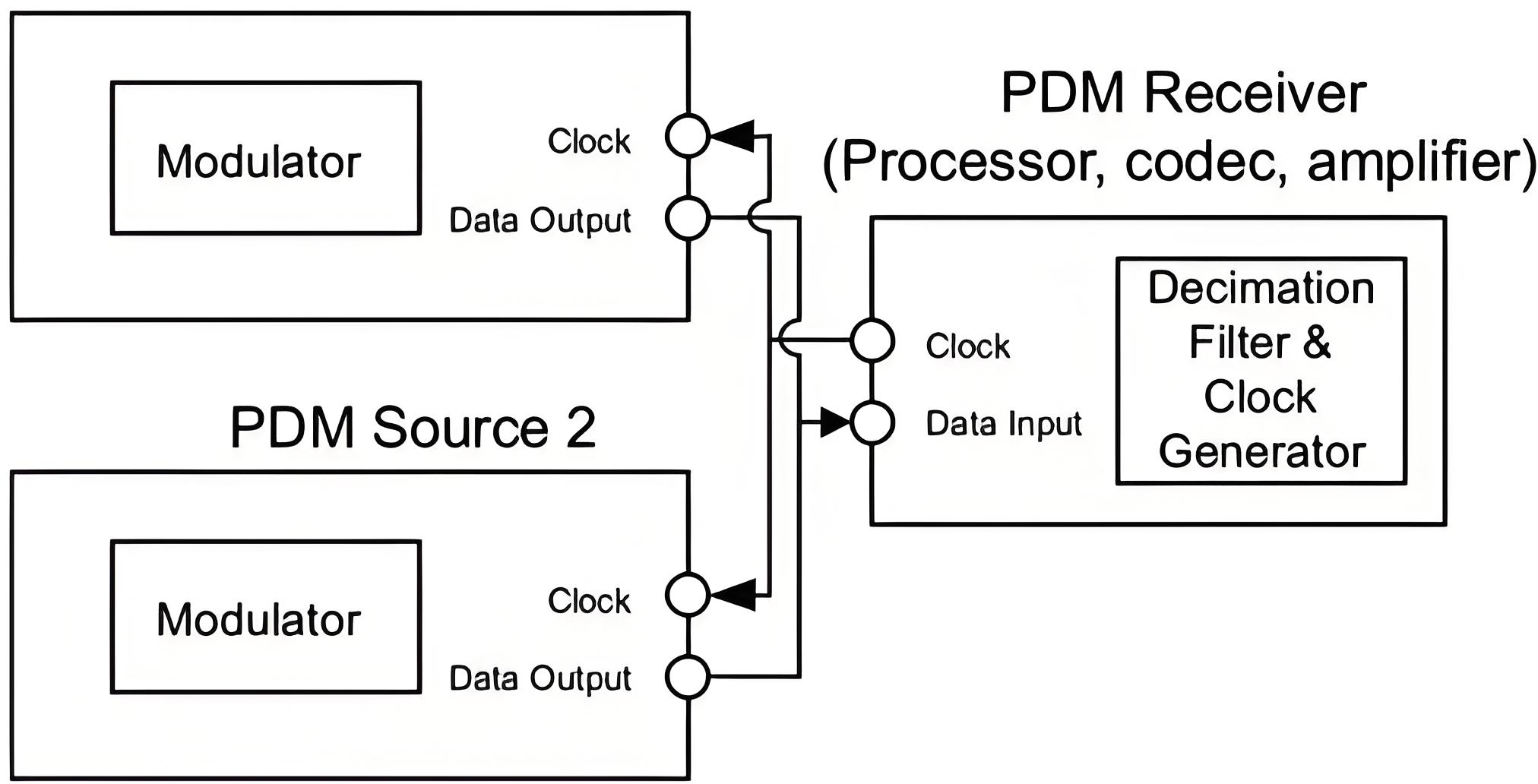

麦克风通过I2S将PDM信号传输至音频处理器。

二、I2S IP的五大技术特点

低延迟高保真

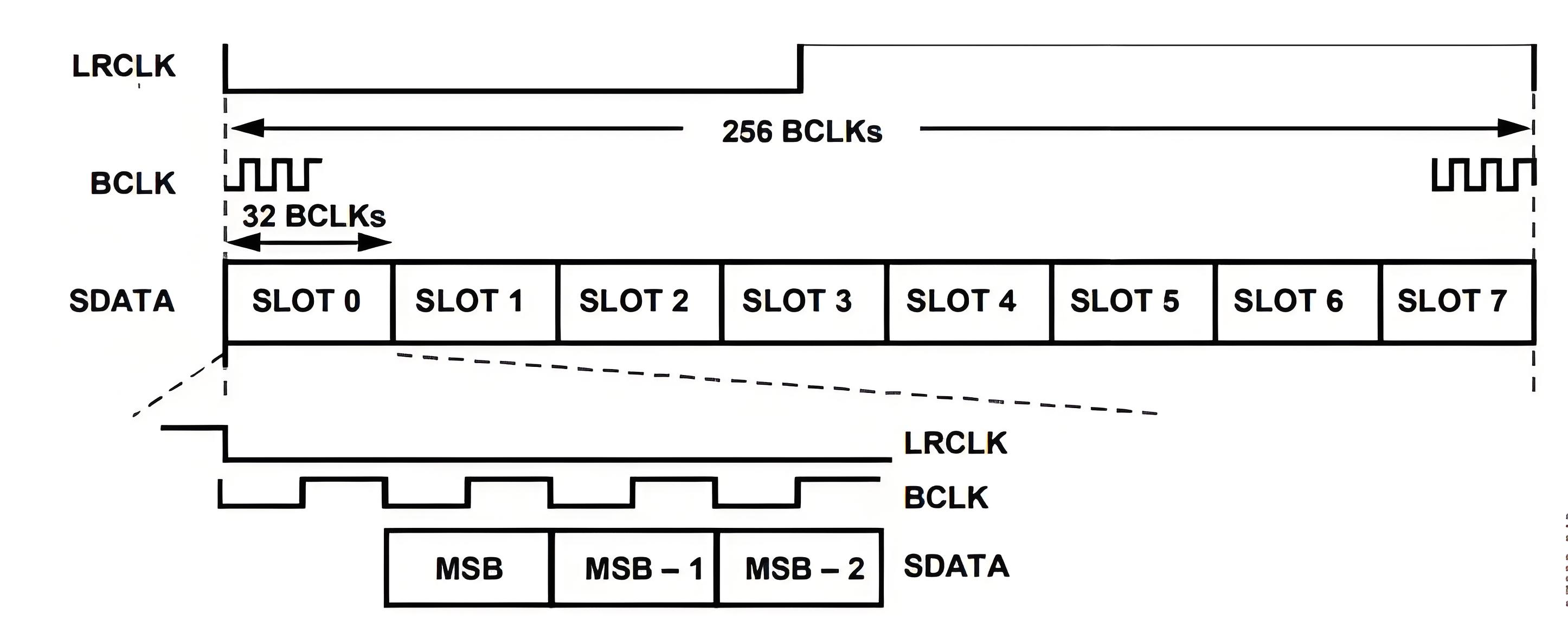

I2S采用MSB(最高有效位)优先传输机制,确保关键音频信息完整送达。接收端在时钟上升沿采样数据,传输延迟仅纳秒级,满足实时音频处理需求。

灵活的时钟架构

主从模式可配置:IP核可生成时钟(主模式)或接收外部时钟(从模式);

MCLK同步设计:主时钟(MCLK)与数据时钟(BCLK)同源,避免采样偏差。

例如:ADAU1761 CODEC需MCLK同步,否则会出现杂音。

多声道扩展能力

通过TDM(时分复用)模式,单组I2S总线可传输8通道甚至更多音频数据:

TDM模式BCLK频率 = 采样率 × 通道数 × 位深

(如48kHz采样率+32位深+8通道需12.288MHz时钟)

抗干扰设计

管脚串接33Ω电阻抑制反射;

短帧同步(Short Frame Sync)模式减少信号抖动。

低功耗优势

相比PCM协议,I2S功耗降低30%以上,尤其适合电池供电的移动设备。

三、I2S IP的四大应用场景

智能音频终端

语音交互:数字麦克风通过I2S传输PDM数据至处理器,结合降噪算法实现远场拾音;

高清播放:DAC通过I2S接收24bit/192kHz音频流,驱动扬声器输出。

车载娱乐系统

采用TDM模式传输多座位独立声道:

主控芯片通过1组I2S总线管理4声道环绕声;

时钟同步设计避免引擎干扰导致的音频断点。

无线音频设备

蓝牙耳机CODEC通过I2S接收44.1kHz SBC解码数据;

支持左右声道独立FIFO传输,降低延时。

工业音频处理

DSP芯片通过I2S采集多路传感器音频,实时分析设备状态(如异响检测)。

四、设计选型指南

根据需求选择协议方案:

| 场景 | 推荐协议 | 原因 |

|---|---|---|

| 立体声耳机 | I2S | 低延迟+低功耗 |

| 家庭影院多声道 | TDM | 单总线支持8通道 |

| 数字麦克风阵列 | PDM+I2S | 高信噪比+简化布线 |

| 高清录音设备 | PCM | 支持24bit/192kHz高保真 |

避坑提示:

主从设备时钟极性需严格匹配;

TDM脉冲模式需在LRCLK引脚增加47pF电容对齐时序。

五、未来演进

随着空间音频和AI降噪技术的普及,I2S IP正向更高集成度演进:

支持32通道TDM的超高带宽传输;

融合I3C协议实现动态地址分配;

硅光互联技术进一步降低纳秒级延迟。

结语

I2S IP核如同数字音频系统的"神经脉络",其低延迟、高同步、易扩展的特性,将持续赋能从消费电子到工业智能的音频创新。设计者需深入理解其时钟机制与协议变体,方能构建稳定高效的音频架构。