EP4CE10F17C8-锁相环

1.例化

c

pll_clk u0_pll_clk(

.areset (~sys_rst_n ),

.inclk0 (sys_clk ),

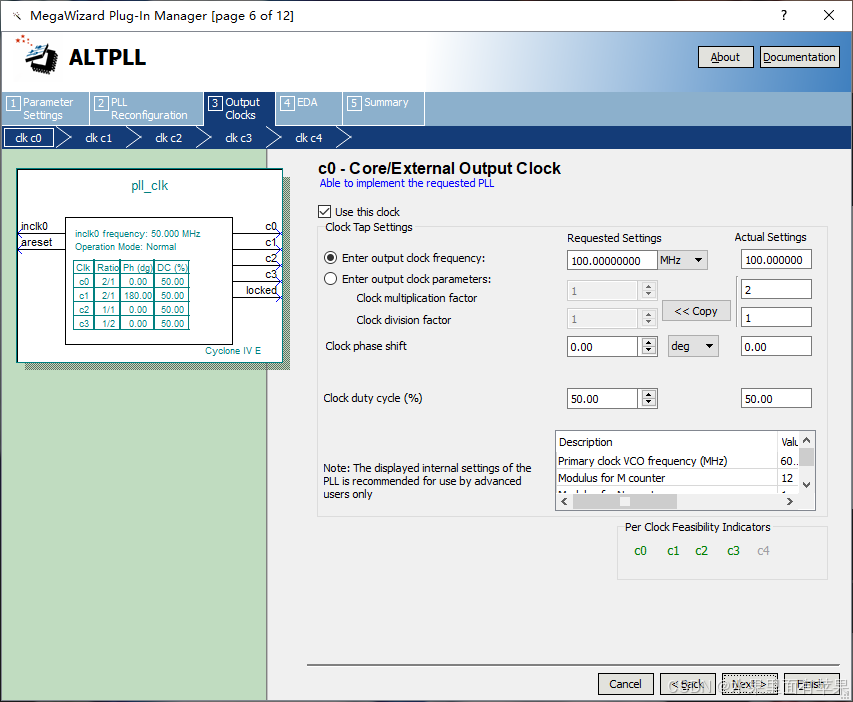

.c0 (clk_100m ),

.c1 (clk_100m_180deg),

.c2 (clk_50m ),

.c3 (clk_25m ),

.locked (locked )

);2.配置

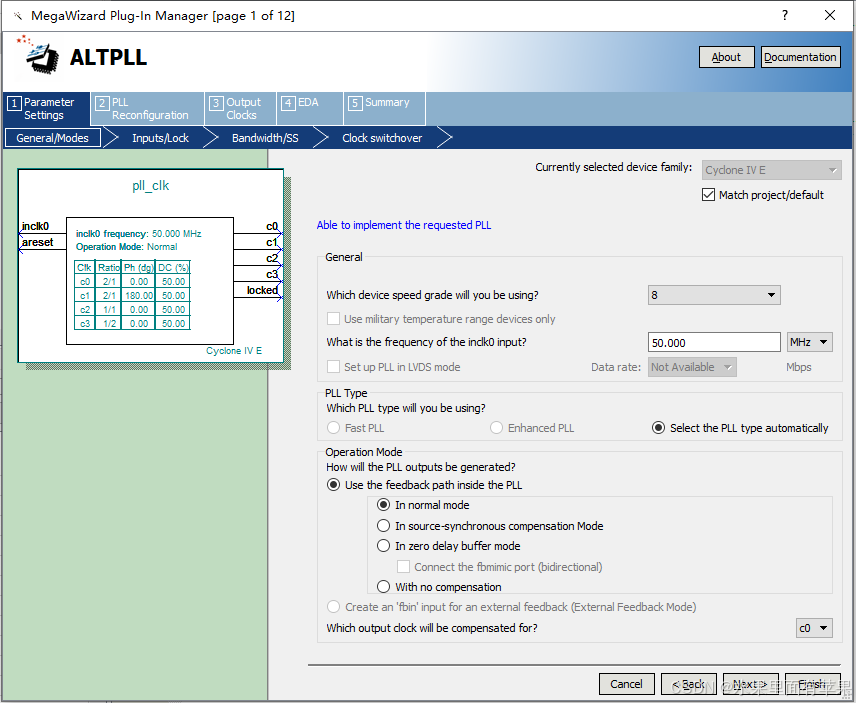

我们要用到的pll模块是I/O目录下的ALTPLL。

速度等级8

晶振频率根据实际填写

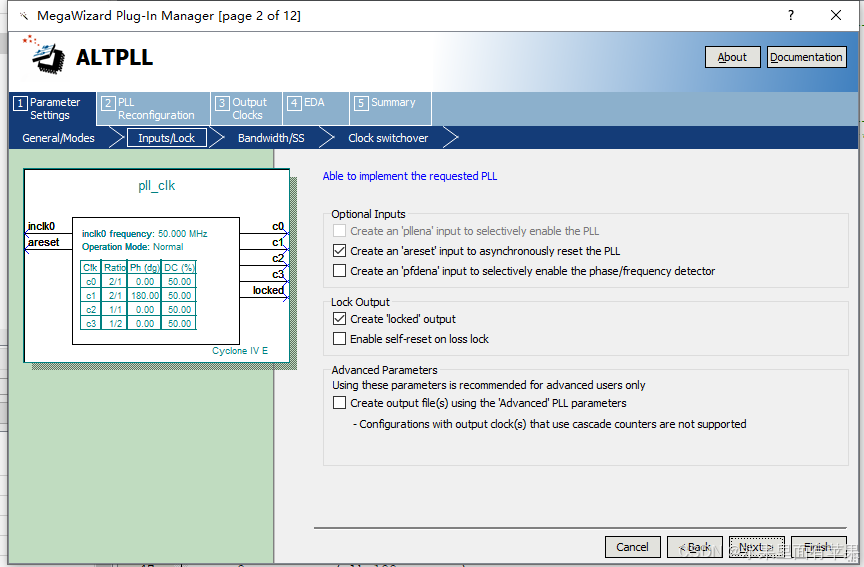

输入端需不需要复位信号

输出端需不需要锁定信号

高级参数

这里可以配置输入端和输出端,高级参数一般项目中可以不用管。

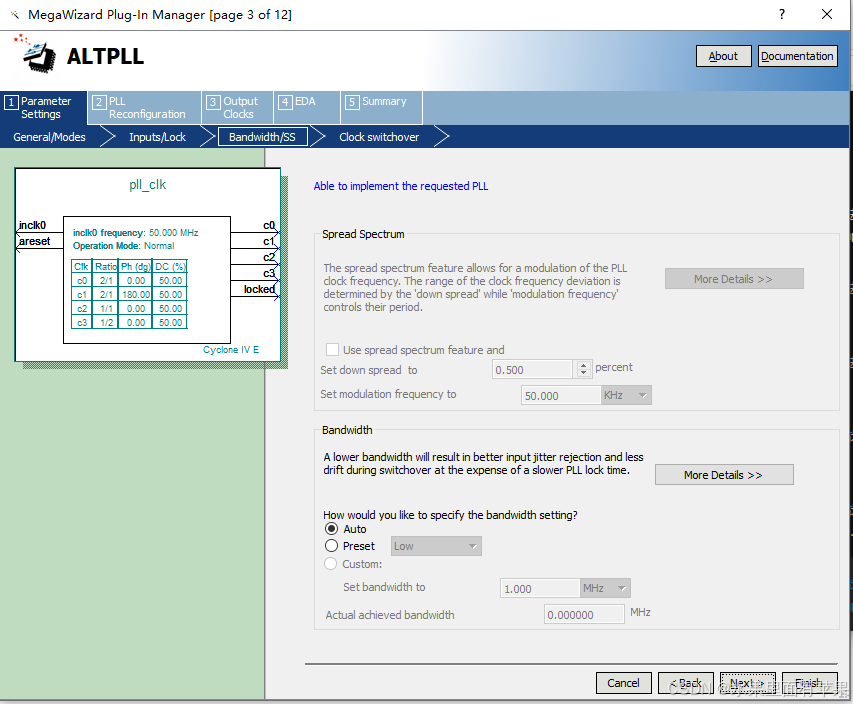

可以忽略

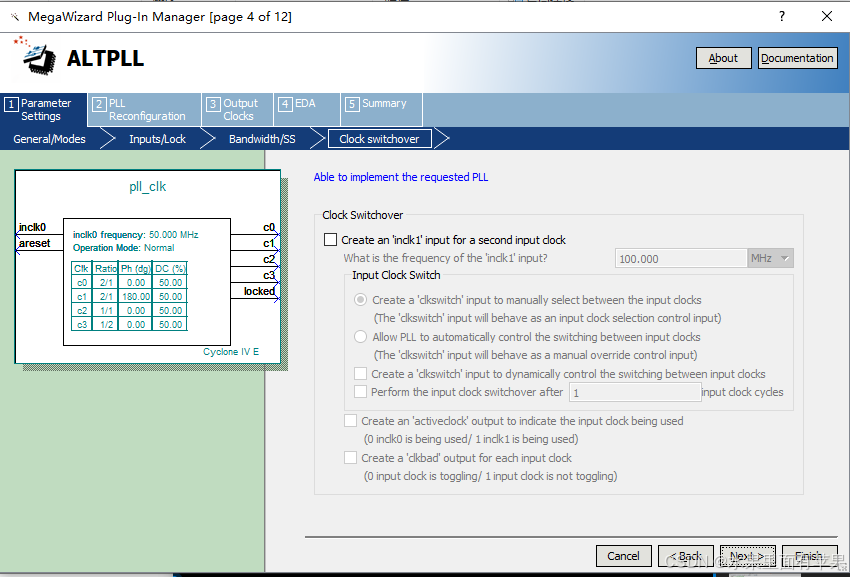

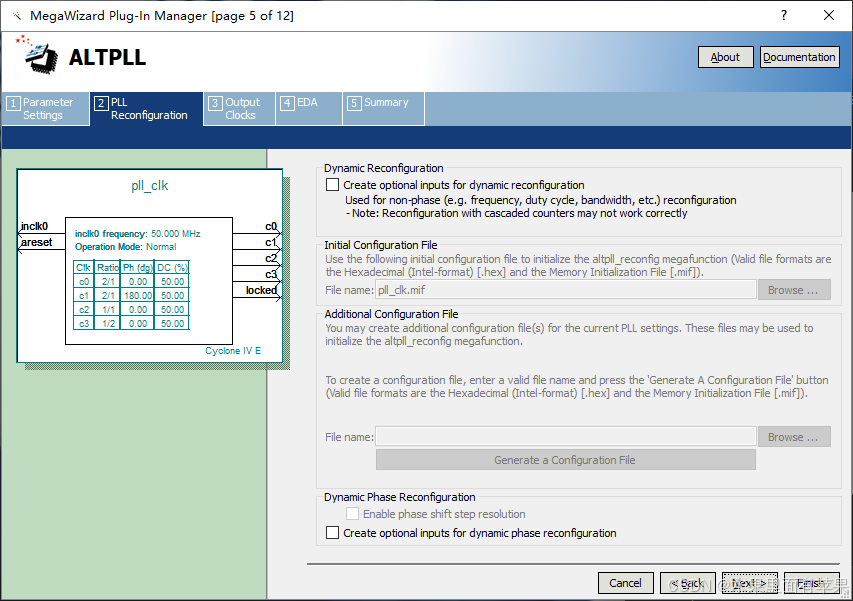

重配置,可忽略

开始配置始终的频率

完成后直接点击开始