文章目录

嵌入式处理器

嵌入式微处理器的组成

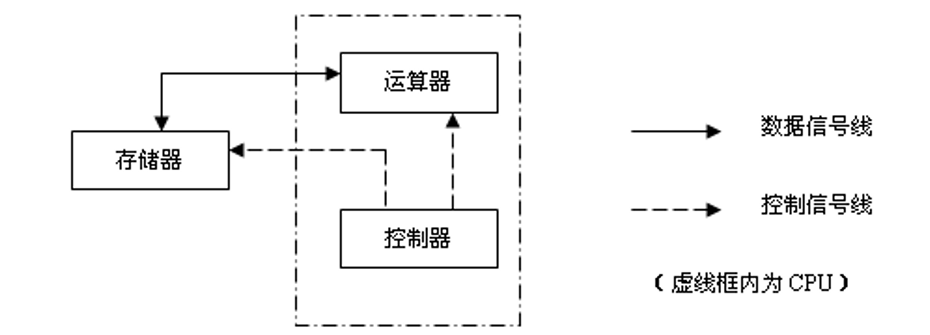

嵌入式系统中的中央微处理器(CPU)是嵌入式系统中最重要的一个部分

CPU(中央处理器)由运算器 和控制器两大部分组成

- 运算器(执行算术/逻辑运算):用来完成算术运算和逻辑运算,运算的中间结果被暂存在运算器内

- 控制器(指令译码、时序控制):用来控制、指挥程序和数据的输入、运行,处理运算结果。它是计算机组成的神经中枢,指挥全机各部件自动、协调地工作

微处理器的关键指标

- 主频:CPU内部时钟频率,也就是CPU运算时的工作频率,直接影响运算速度(例如3.0 GHz)

- 外频:系统总线频率,决定CPU与外部设备(如内存)的通信速率

- 倍频 :指CPU外频与主频相差的倍数,主频 = 外频 × 倍频,用于平衡CPU内部高速与外部低速设备的协同

- 缓存(Cache) :

- L1 Cache(一级缓存):集成在CPU内核中,速度最快,容量最小(KB级)

- L2 Cache(二级缓存):位于CPU与内存之间,容量较大(MB级)

- L3 Cache(三级缓存):多核共享缓存,容量更大,降低内存访问延迟

嵌入式微处理器的流水线技术

微处理器的流水线技术

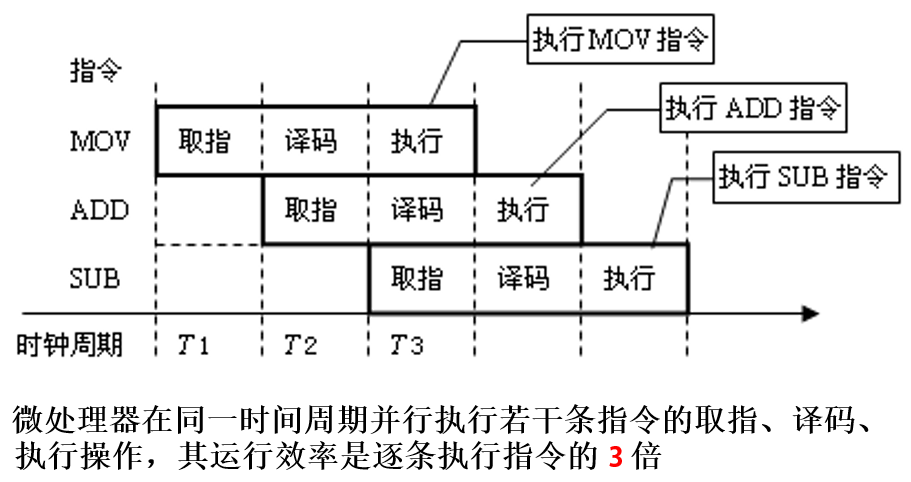

原理:将指令处理拆分为多个阶段(取指、译码、执行等),各阶段并行工作来缩短程序执行时间,提高微处理器的运行效率和吞吐率

【eg.】

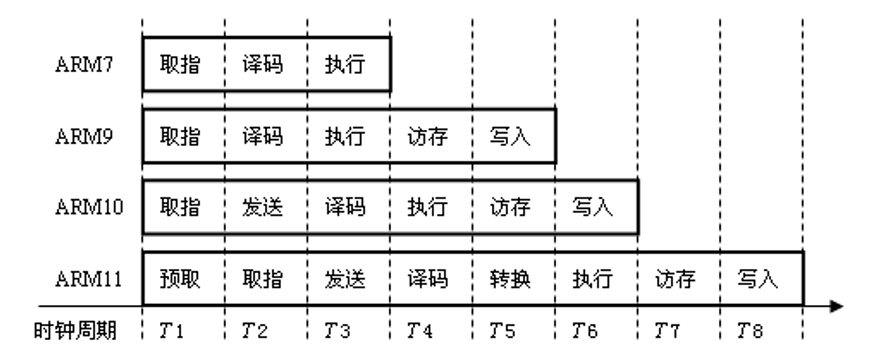

ARM处理器示例:

- ARM7:3级流水线(取指→译码→执行)

- ARM9:5级流水线(新增内存访问和写回阶段)

- ARM11 :8级流水线,支持分支预测和乱序执行,显著提升效率

寄存器与存储器

寄存器

作用:CPU内部的高速存储单元,用于暂存指令、数据和地址(如ARM的R0-R15通用寄存器)

特点:访问速度极快(纳秒级),但容量极小(通常为32/64位)

存储器

- RAM(随机存取存储器) :

- DRAM :动态随机存取存储器,需定期刷新,容量大、成本低

- SRAM:静态随机存取存储器,无需刷新,速度快但成本高(常用于缓存)

- Flash存储器 :

- NOR Flash:支持芯片内执行(XIP),读取速度快,适合存储代码

- NAND Flash:容量大、写入快,适合存储大量数据(不能直接在芯片内执行程序)

总线与通信协议

总线

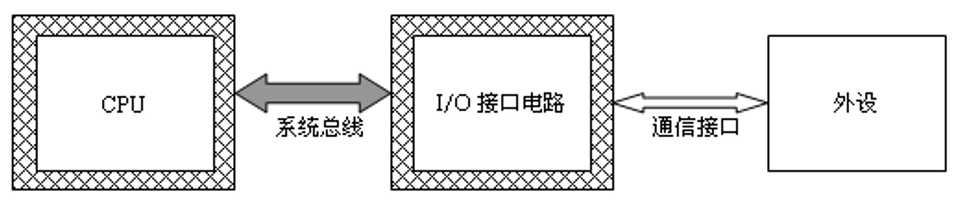

总线是接口电路与CPU或者接口电路与I/O外部设备之间连接的主要形式,是各功能部件之间传送信息的公共通路

采用一组公共的信号线作为嵌入式系统各部件之间的通信线,这组公共信号线就称为总线

总线通信协议

通信协议是指通信双方的一种约定

约定包括对数据格式、同步方式、传送速度、传送步骤等问题做出统一规定,通信双方必须共同遵守

-

总线时序协议

- 同步时序:总线上所有事件共用同一时钟脉冲进行操作过程的控制,所有事件都在时钟周期的开始发生

- 异步时序:操作由源或目的模块发出的特定信号确定。双方相互提供联络信号

-

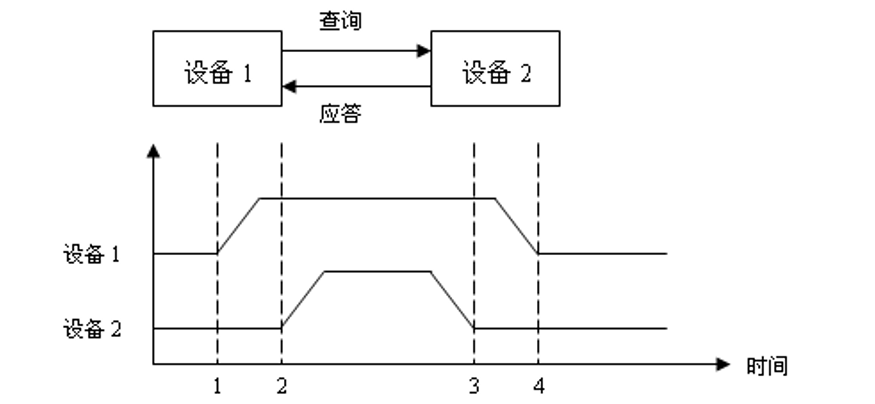

异步时序协议的握手协议

在嵌入式系统或计算机体系中,异步通信 是指没有统一的时钟信号来同步通信双方的行为,而是依赖握手信号来协调数据的发送与接收

握手通常通过两个控制信号线来完成:

- 请求信号(Request)

- 响应信号(Acknowledge)

它的过程可以分为四个周期(阶段):

阶段 发起方(主设备)行为 响应方(从设备)行为 描述 请求阶段 主设备在数据准备好后,将请求信号置为高电平(或有效状态) \ 表示"我准备好了要传数据" 应答阶段 \ 从设备检测到请求信号后,准备接收数据,并将响应信号置为高电平 表示"我准备好了可以接收" 请求释放阶段 主设备检测到响应信号后,清除请求信号(拉低) \ 表示"数据已发送完毕" 应答释放阶段 \ 从设备检测到请求信号拉低后,也拉低响应信号 表示"数据接收完毕,通信完成"

I/O端口与中断

I/O端口

I/O端口又称为I/O接口,它是微处理器对外控制和信息交换的必经之路,是CPU与外部设备连接的桥梁,它在CPU与外部设备之间起信息转换和匹配的作用。I/O端口有串行和并行之分

CPU对外设I/O端口物理地址的编址方式有两种:

- I/O映射(独立编址):独立地址空间

- 内存映射(统一编址):I/O与内存共享地址空间

具体采用哪一种则取决于CPU的体系结构

中断

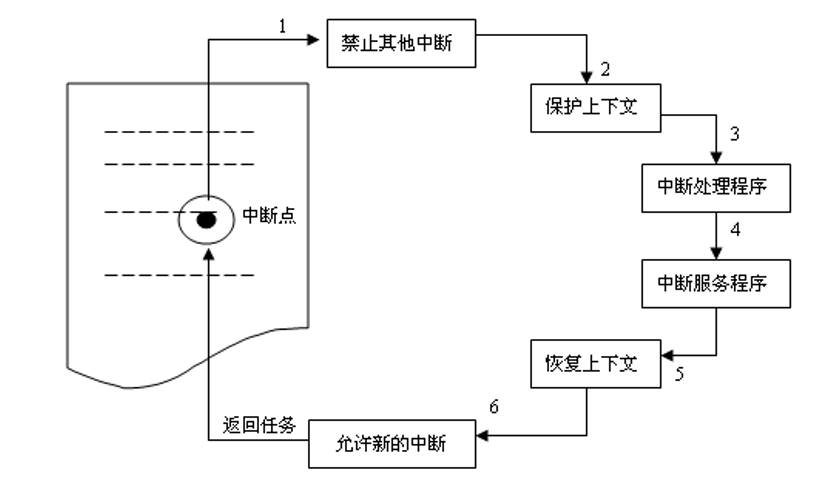

流程:外设请求→CPU保存现场→执行中断服务程序(ISR)→恢复现场继续执行

应用场景:实时响应事件(如按键触发、传感器数据到达)