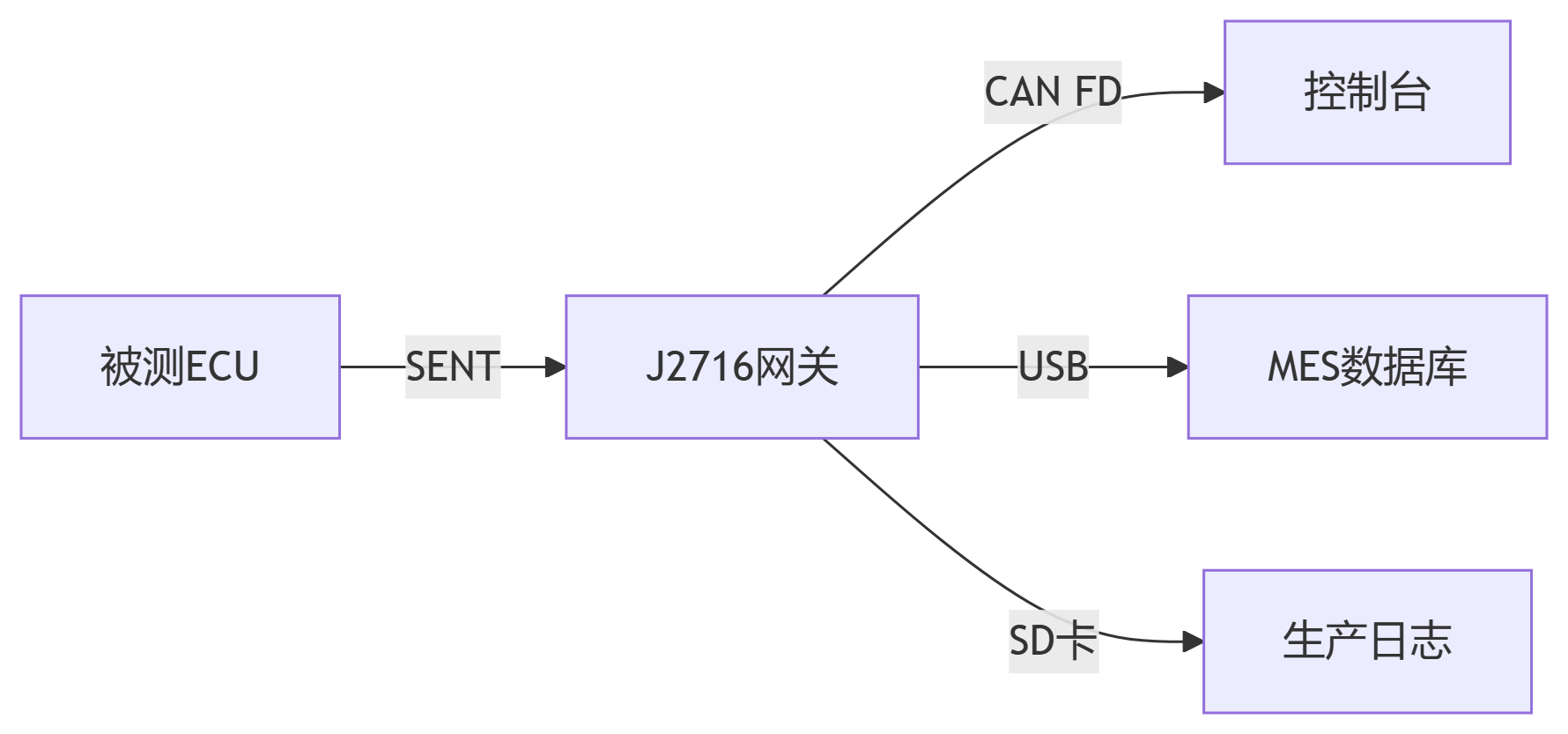

本文解析符合SAE J2716标准的工业级协议转换设备技术架构,通过拆解其四路双向SENT通道与多总线(CANFD/Ethernet/USB)的实时交互机制、MicroSD独立日志系统设计及模拟量动态映射方案,为汽车电子与工业通信开发者提供可复用的技术参考。

一、核心架构设计

1.1 四路SENT通道的FPGA实现

-

硬件逻辑:采用Xilinx Zynq-7000 SoC,通过可编程逻辑单元实现4路独立SENT控制器

-

关键参数支持:

-

Tick时间:3μs~90μs(0.1μs步进)

-

数据域:支持1-8个半字节(Fast/Slow/Enhanced格式)

-

SPC模式:支持Short PWM Code单脉冲数据传输

-

-

错误注入:硬件级CRC故障注入引擎,支持Fast/Slow报文

1.2 协议转换引擎

-

跨总线转发延迟(实测数据):

转换方向 延迟(μs) 吞吐量上限 SENT→CAN FD ≤250 8,000帧/秒@500kbps SENT→Ethernet ≤120 1,500帧/秒@100Mbps USB→SENT ≤180 全速12Mbps -

带宽优化:基于Identifier的帧过滤算法,减少95%无效数据转发

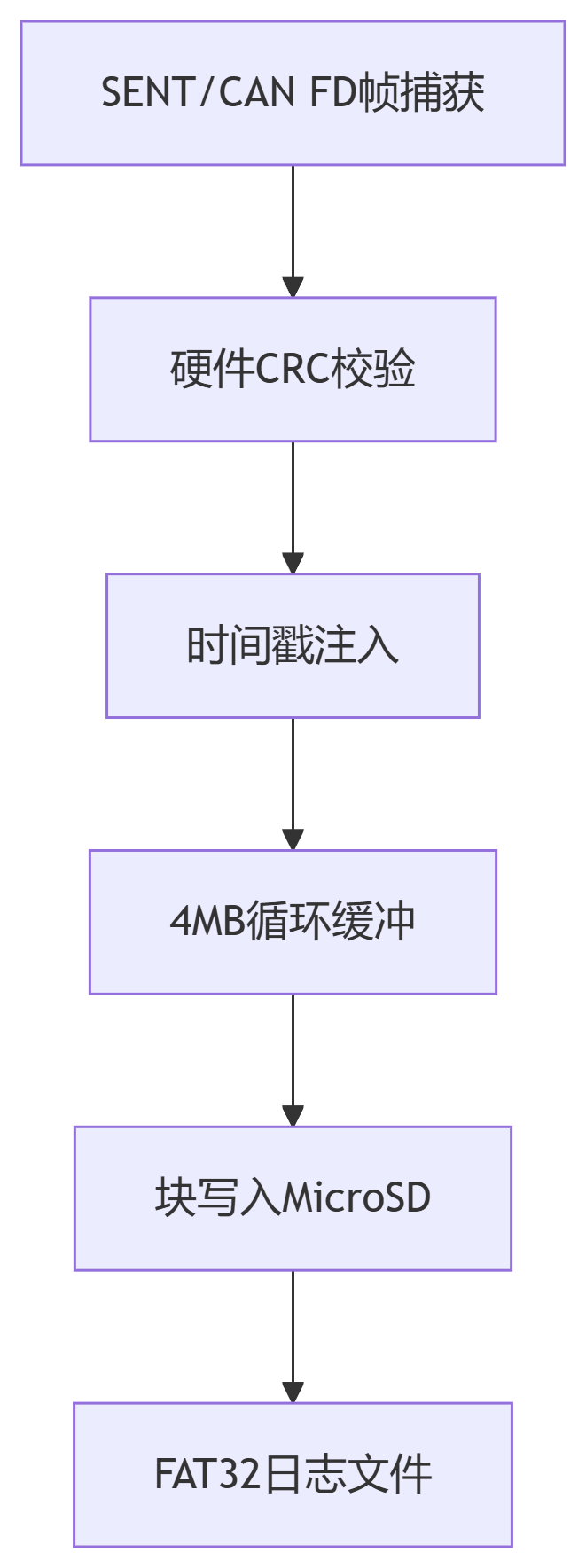

二、独立数据记录系统关键技术

2.1 高精度时序同步

-

RTC时钟误差:±2ppm(-40℃~85℃),电池备份≥5年

-

时间戳精度:1μs(FPGA硬件计时器实现)

2.2 存储优化策略

- 支持32GB卡持续记录45天(1ms采样周期)

三、模拟量-SENT动态映射引擎

3.1 线性转换模型

Vout=(SENTraw×K)+BVout=(SENTraw×K)+B

约束条件:

-

输入范围:0~5V(16-bit ADC,±0.05% FSR线性误差)

-

输出范围:0~4.095V(12-bit DAC)

-

边界保护:±0.5V硬件箝位电路

3.2 位域映射示例

python

# 将SENT通道1的12位数据映射到模拟输出0

config = {

"source": "SENT_CH1_RX", # 数据源

"start_bit": 4, # 起始位位置

"bit_length": 12, # 有效数据长度

"multiplier": 0.001, # 缩放系数

"offset": 0.5, # 电压偏移

"clamp": [0.2, 4.0] # 输出限幅

} # 配置存储于设备NVROM:cite[6]:cite[9]四、工程集成方案

4.1 开放协议栈集成

- 串口协议框架(RS-232/USB VCP):

text

[STX][LEN][ID][DATA][CHKSUM][ETX]示例:读取设备序列号(0x5A指令)

python

import serial

req = bytes.fromhex('02 01 5A 5B 03') # 请求帧

ser.write(req)

resp = ser.read(9) # 响应格式:02 05 5A SN1 SN2 SN3 SN4 CHK 03:cite[9]4.2 多设备CAN总线协同

| 设备ID | TX_CAN_ID | RX过滤器掩码 |

|---|---|---|

| NodeA | 0x500 | 0x600~0x6FF |

| NodeB | 0x510 | 0x700~0x7FF |

冲突规避:支持29bit扩展ID的ACR/AMR寄存器配置

五、实测性能对比

| 功能 | 本设备 | 传统方案 | 提升幅度 |

|---|---|---|---|

| SENT→CAN FD延迟 | 223μs ±15μs | 480μs ±50μs | 53.5% |

| 多通道捕获抖动 | <1% | 3%~8% | 3× |

| 温度适应性 | -40℃~85℃ | -20℃~60℃ | 扩展45% |

测试条件:ISO 16750-4 温度循环标准

六、典型应用场景

-

ECU传感器模拟

-

模拟量输入→SENT实时转换(如油门踏板信号仿真)

-

配置示例:12-bit分辨率,100Hz更新率36

-

-

产线终端测试

HIL系统集成

- 通过Ethernet-CAN FD接口连接dSPACE/ETAS实时机

技术挑战与解决方案

| 挑战 | 解决策略 | 技术效益 |

|---|---|---|

| SENT帧抖动累积 | FPGA硬件时间戳同步 | 通道间偏移<100ns |

| 大容量日志丢失风险 | 4MB DDR3缓存+块写入策略 | 100%连续捕获@10kHz |

| 模拟输出噪声干扰 | 隔离型DC-DC+π型滤波电路 | SNR>80dB |

了解更多详情信息,联系广州智维提供免费技术支持;