一、时钟

1.时钟系统基本概念

(1)PLL (锁相环, Phase-Locked Loop)

作用 :PLL是一种反馈控制电路,用于生成稳定的高频时钟信号。它通过将输出时钟与参考时钟进行比较和调整,可以产生比输入参考时钟频率高得多的输出时钟。倍频Fin * n = Fout

特点:

-

倍频功能:可将低频参考时钟倍频为高频时钟

-

低抖动:输出时钟稳定性好

-

可编程性:可通过寄存器配置倍频系数

(2)Prescaler (预分频器)

作用 :用于对输入时钟进行分频,降低时钟频率。分频 Fin / m = Fout

特点:

-

分频比可配置 (通常为2的幂次方或整数分频)

-

用于将高速时钟分频为适合外设工作的频率

-

可级联使用实现更大的分频比

(3)FPD (Fractional Post Divider,相位项数分频器 )

作用 :提供更精细的时钟分频能力,可以实现非整数分频比。既能倍频也能分频 (Fin * n) / m = Fout

特点:

-

支持分数分频 (如4.5分频)

-

提供更灵活的时钟配置

-

通常用于需要特定频率但整数分频无法满足的场景

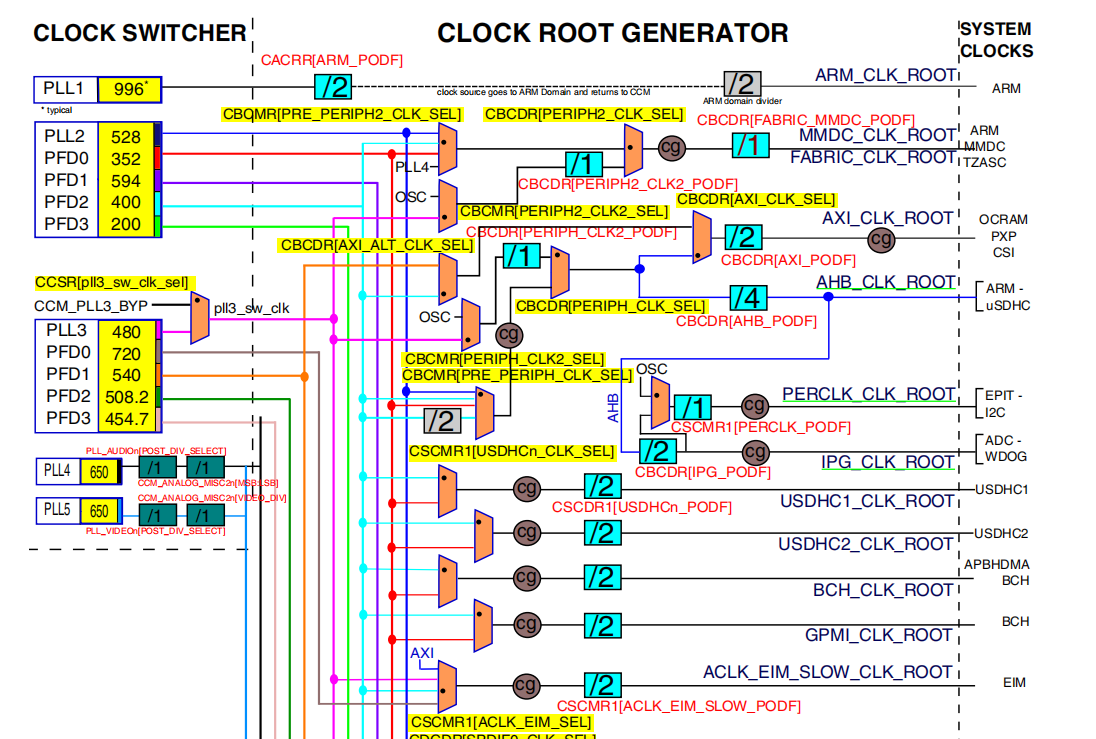

时钟树

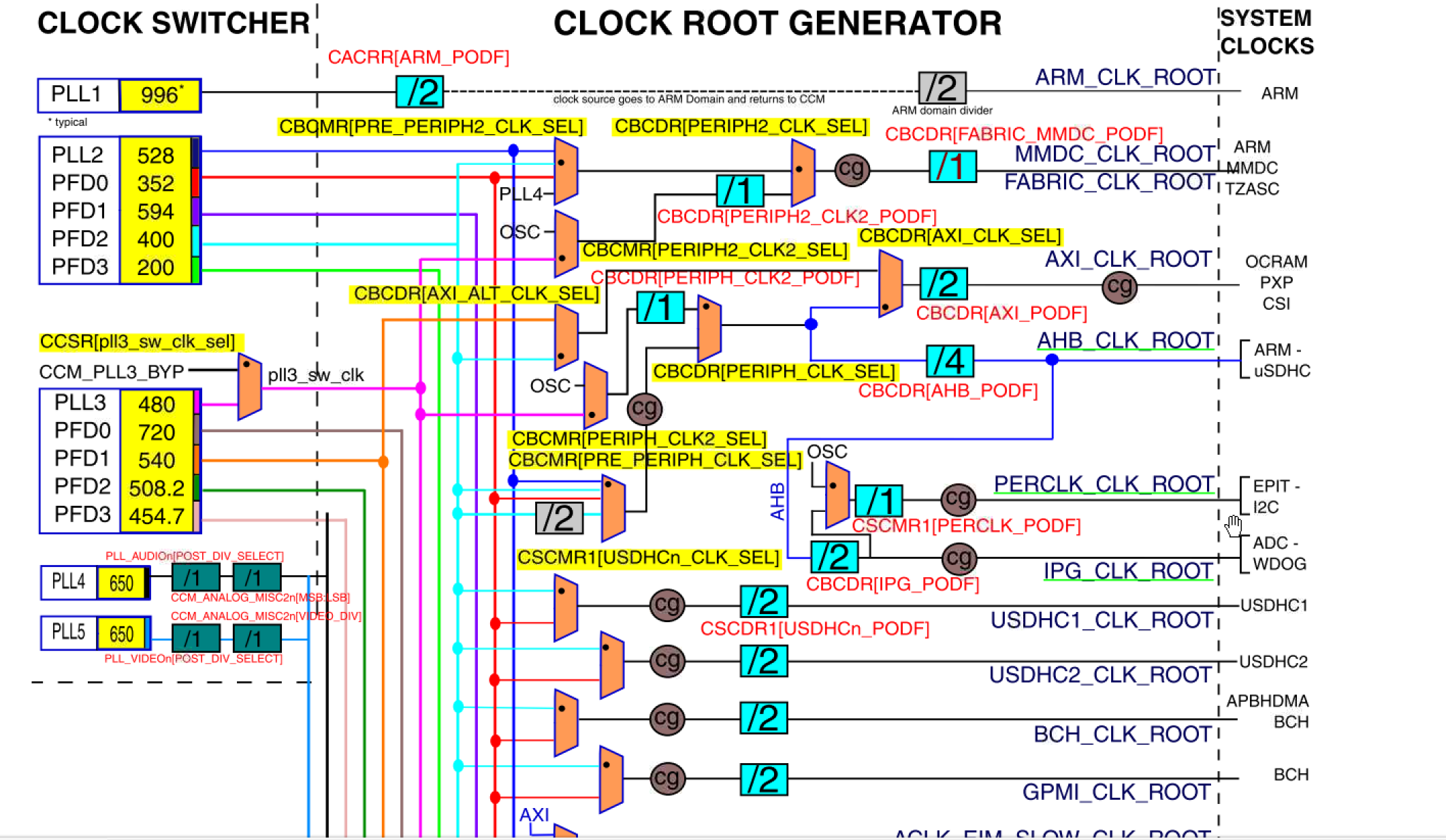

2.IMX6ULL中的PLL和PFD

(1)PLL数量

IMX6ULL中有7个PLL:

-

ARM PLL (用于ARM内核)

-

SYSTEM PLL (系统主PLL)

-

USB1 PLL (USB1专用)

-

USB2 PLL (USB2专用)

-

AUDIO PLL (音频子系统)

-

VIDEO PLL (视频处理)

-

ENET PLL (以太网专用)

(2)PFD数量

IMX6ULL的每个PLL有4个PFD (Phase Fractional Dividers),因此总共有:

- 7个PLL × 4个PFD = 28个PFD

二、EPIT定时器

1.定义

EPIT的全称是:Enhanced Periodic Interrupt Timer,增强的周期中断定时器 , 它主要是完成周期性中断定时的。

s3c2440里面的定时器还有很多其它的功能,比如输入捕获、PWM 输出等等。但是 I.MX6U 的 EPIT 定时器只是完成周期性中断定时的,仅此一项功能!至于输入捕获、 PWM 输出等这些功能,I.MX6U 由其它的外设来完成。

EPIT 是一个 32 位定时器,在处理器几乎不用介入的情况下提供精准的定时中断,软件使能以后 EPIT 就会开始运行.

2.EPIT 定时器特点

(1).时钟源可选的 32 位向下计数器;

(2). 12 位的分频值;

(3). 当计数值和比较值相等的时候产生中断.

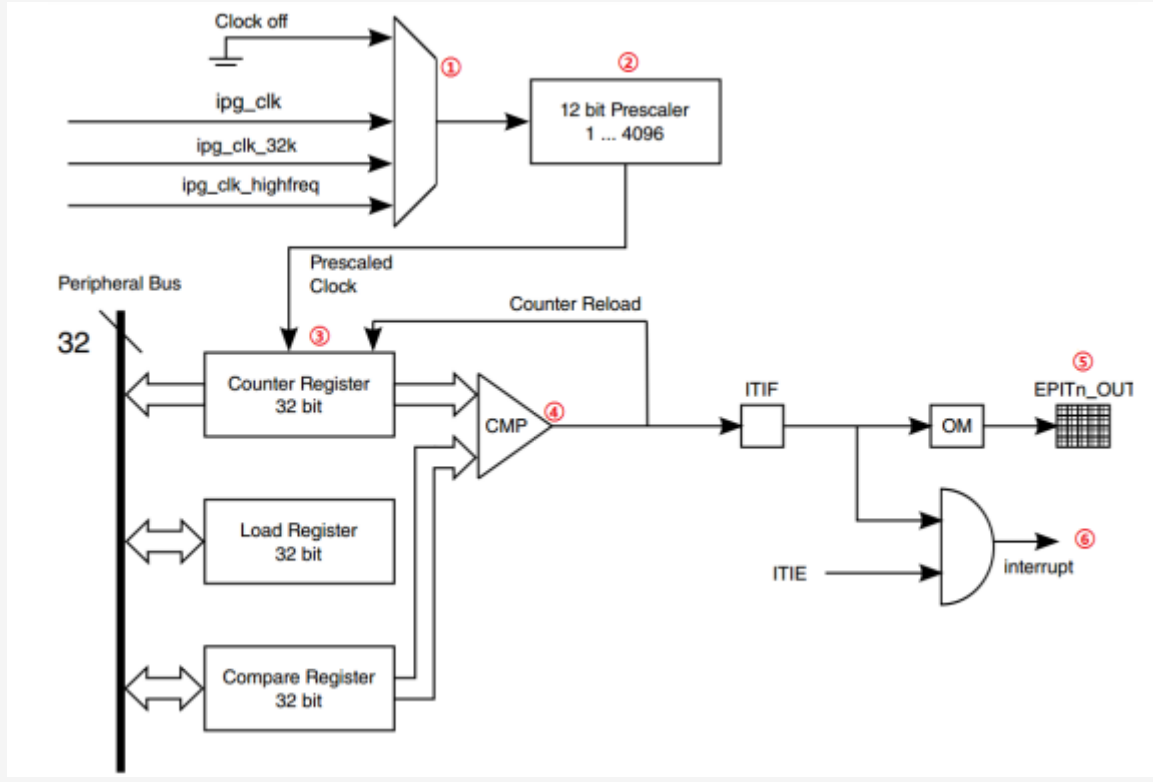

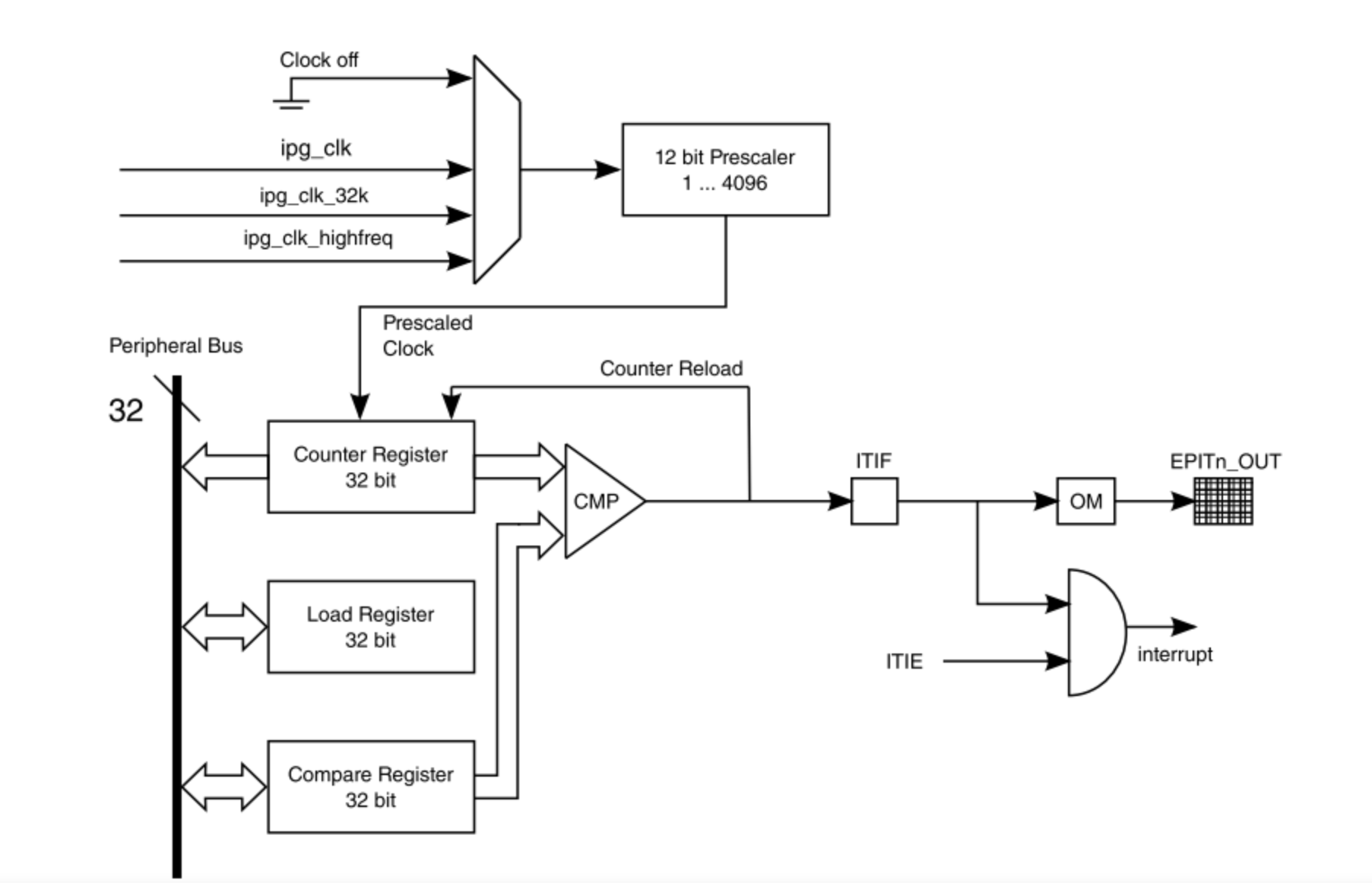

3.EPIT结构图

① 这是个多路选择器,用来选择 EPIT 定时器的时钟源,EPIT 共有 3 个时钟源可选择,ipg_clk、ipg_clk_32k 和 ipg_clk_highfreq,ipg_clk我们之前已经配置好了------66MHz;

② 这是一个 12 位的分频器,负责对时钟源进行分频,12 位对应的值是 0~4095,对应着1~4096 分频.

③ 经过分频的时钟进入到 EPIT 内部,在 EPIT 内部有三个重要的寄存器:计数寄存器(EPIT_CNR)、加载寄存器(EPIT_LR)和比较寄存器(EPIT_CMPR),这三个寄存器都是 32 位的。EPIT 是一个向下计数 器,也就是说给它一个初值,它就会从这个给定的初值开始递减,直到减为 0,计数寄存器里面保 存的就是当前的计数值。如果 EPIT 工作在 set-and-forget 模式下,当计数寄存器里面的值减少到 0,EPIT 就会重新从加载寄存器读取数值到计数寄存器里面,重新开始向下计数;

④ 比较器,比较寄存器里面保存的数值用于和计数寄存器里面的计数值比较,如果相等的话就会产生 一个比较事件;

⑤ EPIT 可以设置引脚输出,如果设置了的话就会通过指定的引脚输出信号;

⑥ 产生比较中断,也就是定时中断。

4.EPIT两种工作模式

set-and-forget 和 free-running

这两个工作模式的区别如下:

set-and-forget模式:此模式下,在此模式下 EPIT 的计数器从加载寄存器 EPITx_LR 中获取

初始值,不能直接向计数器寄存器写入数据。不管什么时候,只要计数器计数到 0,那么就会从加载寄存器 EPITx_LR 中重新加载数据到计数器中,周而复始。

free-running模式:此模式下,当计数器计数到 0 以后会重新从0XFFFFFFFF 开始计数,并

不是从加载寄存器 EPITx_LR 中获取数据。

5.相关配置

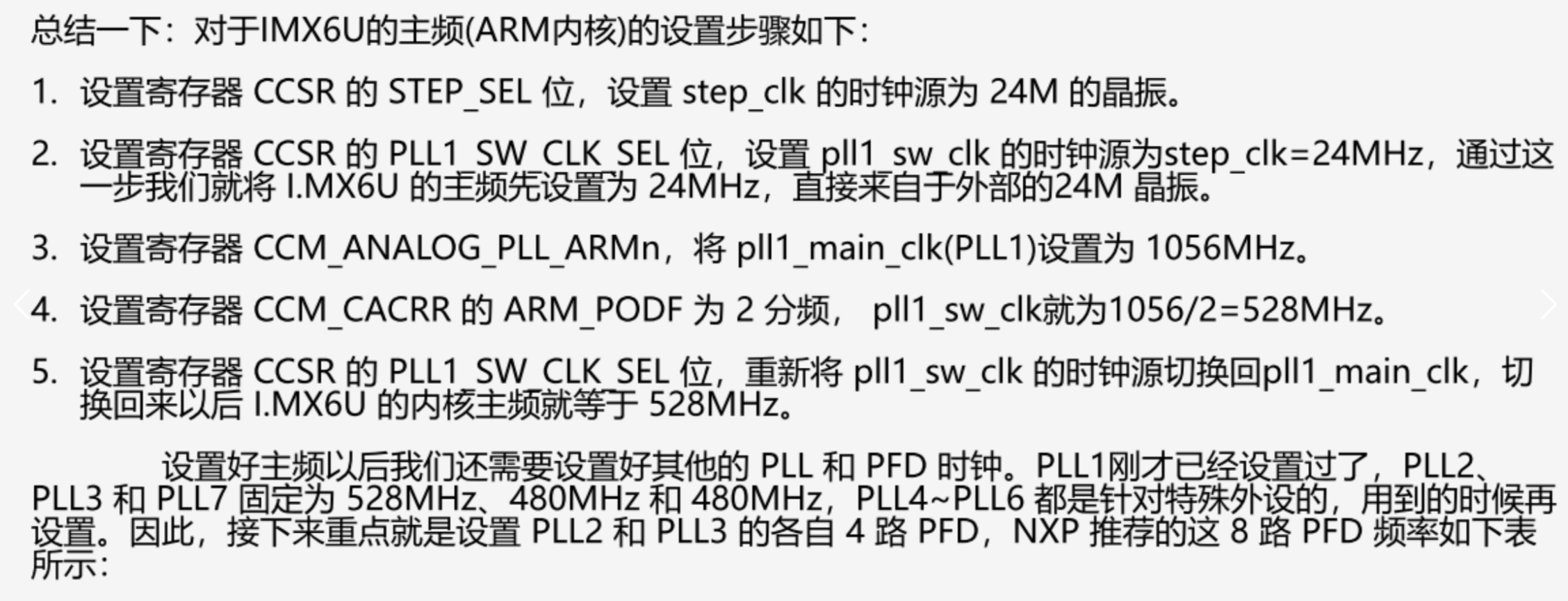

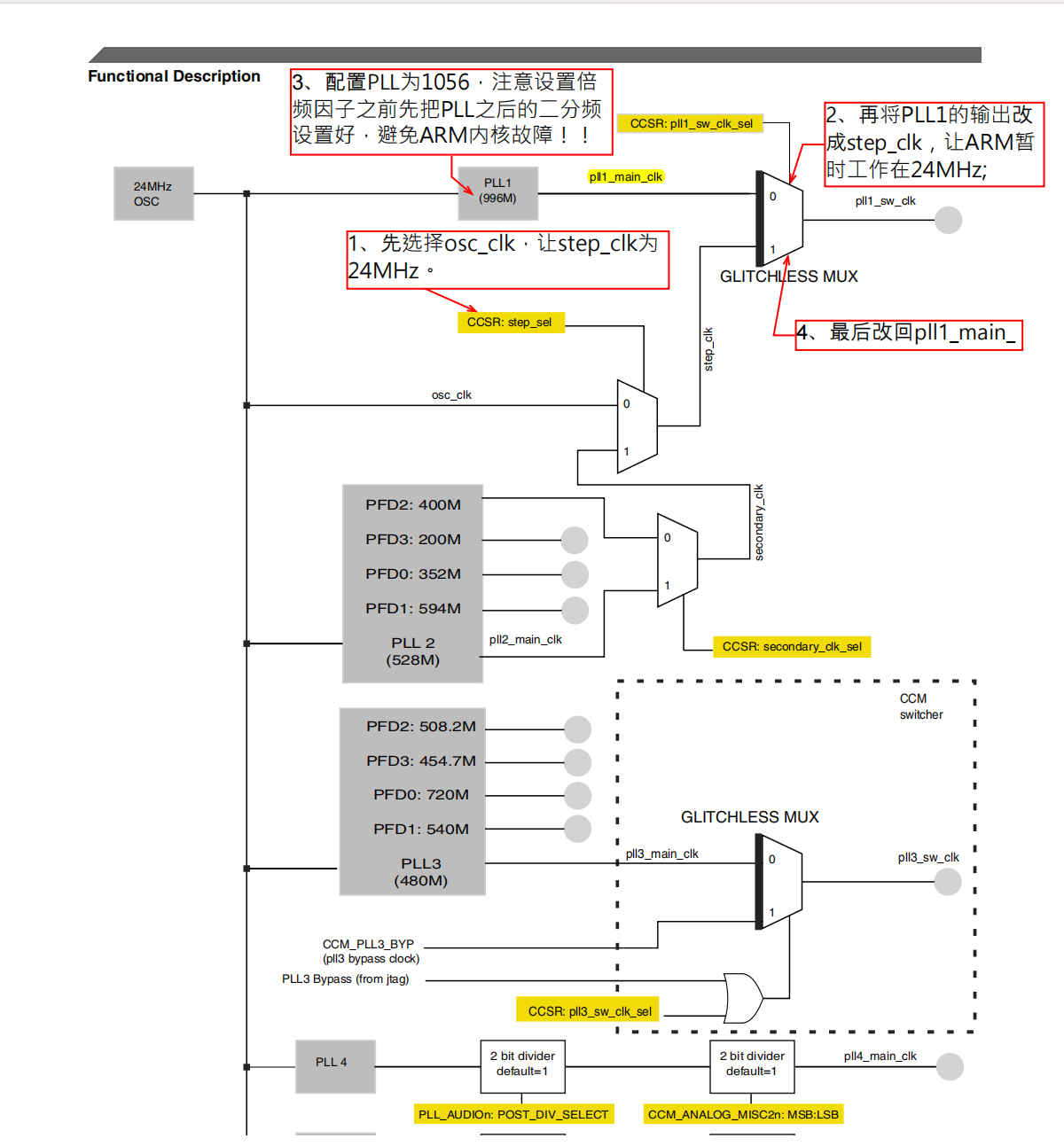

(1) 配置PLL1、PLL2、PLL3

(2)、配置时钟生成树CLOCK ROOT GENERATOR

(3)验证配置(使用EPIT外设)

6.EPIT设置步骤

- 设置 EPIT1 的时钟源;

- 设置分频值 ;

- 设置工作模式;

- 设置计数器的初始值来源;

- 使能比较中断;

- 设置加载值和比较值;

- 设置EPIT1 中断服务函数;

- 使能 EPIT1 定时器。

三、GPT通用目的寄存器

输入捕获,输出比较

IMX6U有两个GPT,全称为 General Purpose Timer(通用目的的定时器)。GPT 定时器是一个 32 位向上定时器(也就是从 0X00000000 开始向上递增计数),GPT 定时器也可以跟一个值进行比较,当计数器值和这个值相等的话就发生比较事件,产生比较中断。GPT 定时器有一个 12 位的分频器,可以对 GPT 定时器的时钟源进行分频。

GPT 定时器特性如下:

① 一个可选时钟源的 32 位向上计数器;

② 两个输入捕获通道,可以设置触发方式;

③ 三个输出比较通道,可以设置输出模式;

④ 可以生成捕获中断、比较中断和溢出中断;

⑤ 计数器可以运行在重新启动(restart)或(自由运行)free-run 模式。

GPT主要使用最主要的寄存器是GPT Control Register (GPTx_CR)寄存器主要的域有:

• SWR(bit15):复位 GPT 定时器,向此位写 1 就可以复位 GPT 定时器,当 GPT 复位完成以后此为会 自动清零。

• FRR(bit9):运行模式选择,当此位为 0 的时候比较通道 1 工作在重新启动(restart)模式。当此位为 1的时候所有的三个比较通道均工作在自由运行模式(free-run)。

• CLKSRC(bit8:6):GPT 定时器时钟源选择位,为 0 的时候关闭时钟源;为 1 的时候选择ipg_clk 作为时钟源;为 2 的时候选择 ipg_clk_highfreq 为时钟源;为 3 的时候选择外部时钟为时钟源;为 4 的时候选择 ipg_clk_32k 为时钟源;为 5 的时候选择 ip_clk_24M 为时钟源。我们选择 ipg_clk 作为 GPT定时器的时钟源,因此此位设置位 1(0b001)。

• ENMOD(bit1):GPT 使能模式,此位为 0 的时候如果关闭 GPT 定时器,计数器寄存器保存定时器关闭时候的计数值。此位为 1 的时候如果关闭 GPT 定时器,计数器寄存器就会清零。

• EN(bit):GPT 使能位,为 1 的时候使能 GPT 定时器,为 0 的时候关闭 GPT 定时器。

GPT Prescaler Register (GPTx_PR)用于保存分频值,PRESCALER(bit11:0),这就是 12 位分频值,可设置 0~4095,分别对应 1~4096 分频