上一篇我简要介绍了rf data converter这个ip核的整体功能,这一篇我着重讲一下ip核的时钟结构,由于网上的教程参差不齐,商家给的例程也没有很好的解释,导致我本人走了不少弯路,摸了将近一个月才勉强把时钟树给理解透了

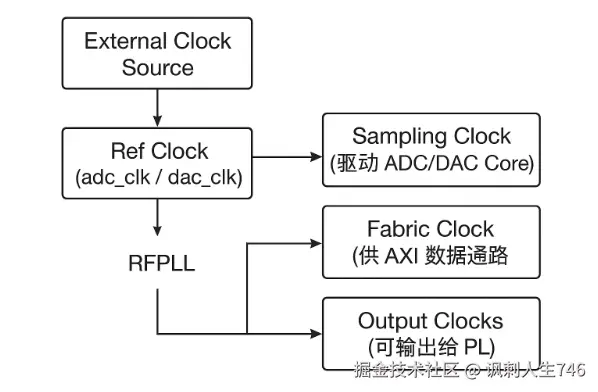

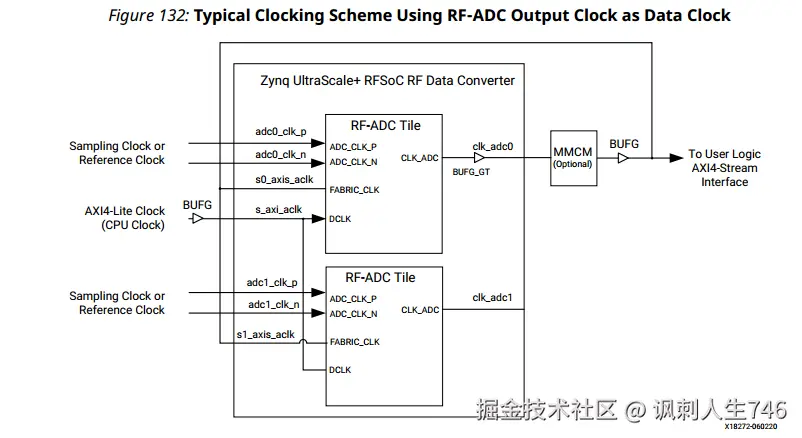

在pg269这个文档里面,对于这个ip核总体的时钟框图大致是这样的

我们可以看到主要是分了几级的时钟,分别是

Sampling clk:ADDA的采样时钟,就是等于他们的采样率(GSPS),在配置ip核时钟的时候可以直接写数值进去

Reference clk:是每个PLL的输入时钟,频率需要与Fabric clk,m_axis_aclk的频率一致,他的值取决于采样率的大小,在配置界面更改采样率的时候reference clk也会变,大小通常为MHz级别,是生成采样时钟的参考时钟

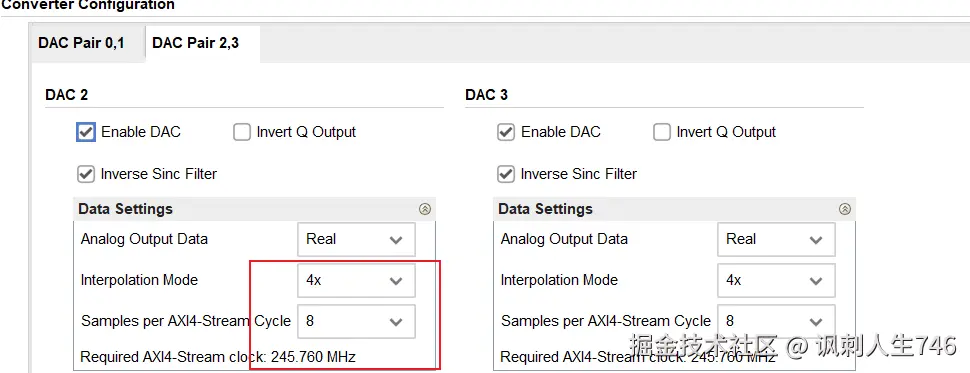

Fabric clk: 这是在所选tile的AXI流时钟输入上提供的时钟频率。由采样速率配置中的设置确定。由于所有tile上的所有AXI流端口共享一个公共AXI流时钟,因此所有fabric clk配置必须要求相同。其值计算方法为

<math xmlns="http://www.w3.org/1998/Math/MathML"> F a x i = f s a m p l e N i n t e r p ⋅ N a x i F_{axi} = \frac{f_{sample}}{N_{interp} \cdot N_{axi}} </math>Faxi=Ninterp⋅Naxifsample

<math xmlns="http://www.w3.org/1998/Math/MathML"> N i n t e r p N_{interp} </math>Ninterp 插值倍数,也是DAC端每个输入样点扩展为N个采样点

<math xmlns="http://www.w3.org/1998/Math/MathML"> N d e c i m N_{decim} </math>Ndecim 抽取倍数,也是ADC端每N个采样点输出一个点

<math xmlns="http://www.w3.org/1998/Math/MathML"> N _ a x i N\_{axi} </math>N_axi 在ip核是 Samples per AXI cycle ,意思是每个AXI时钟周期传输多少个样点

以DAC为例,整个数据通路是这样工作的,例如DDS在FPGA 在每个 AXI 时钟周期(245.76 MHz)送出个 <math xmlns="http://www.w3.org/1998/Math/MathML"> N _ a x i N\{axi} </math>N_axi 个样点,然后RFDC 的 Interpolation Filter将每个样点插值成 <math xmlns="http://www.w3.org/1998/Math/MathML"> N i n t e r p N{interp} </math>Ninterp 倍;插值后的采样流被送往 DAC 核心,运行在 <math xmlns="http://www.w3.org/1998/Math/MathML"> f s a m p l e f_{sample} </math>fsample 时钟下;这样就实现了从 FPGA 低速到 DAC 高速的时域扩展,ADC则是反过来同理

这里需要注意的点就是Fabric clk的配置需要与Ref clk一致,至少要成整数比,因为RFDC Tile 内部的 RF PLL 用 Ref clk 作为参考源来合成高速采样时钟,同时,Fabric clk 可以选择由 Tile PLL 输出的一个分频支路,若 Fabric clk 与 Ref clk 不成整数比,则PLL 输出的相位参考无法对齐,Fabric clk 与 Sampling clk 间出现亚稳态,导致 AXI 接口出现非确定性延迟,数据时序会漂移

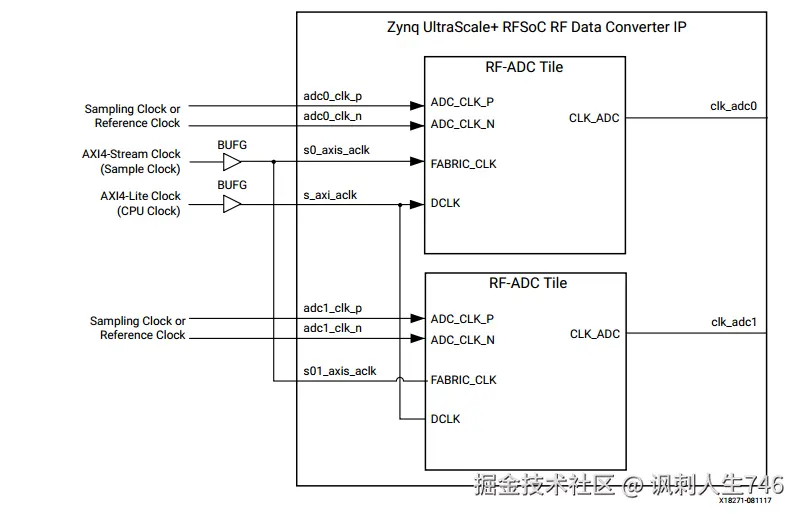

clk_adc/dac: 是作为IP核的输出时钟,可以随着采样率而设置,此时钟可用于驱动AXI 4-Stream时钟输入,就是作为m_axis_aclk的输入,Xilinx官方也给出了这样的图示

sysref clk: 由PL产生,用于多通道同步,这个信号很重要,所有的ADC/DAC tile需通过sysref信号进行时间对齐,这个信号通常很小,是上述所有信号的公约数,大概在10MHz以内,后面讲多片时钟同步的时候会着重讲到这个信号

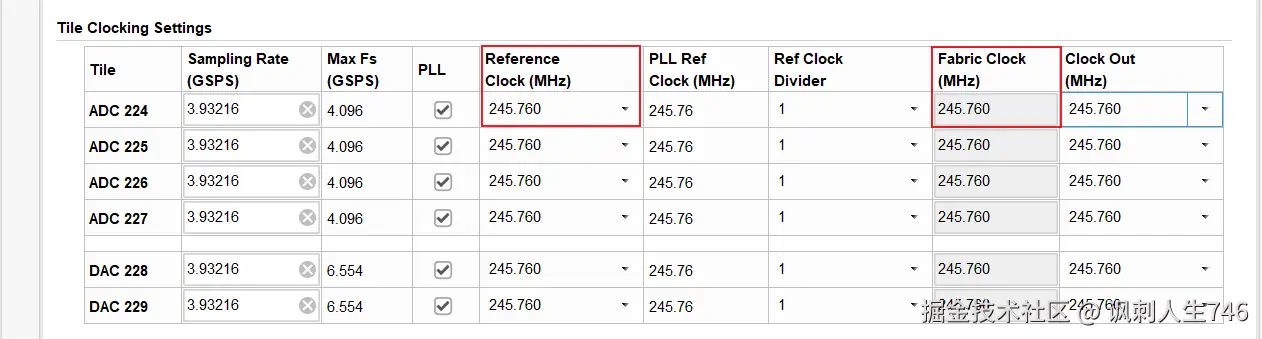

所以在ip核的配置中,如图所示,在设置完采样率之后,Fabric clk是被锁死的,因为由前页的插值抽取倍数和采样周期点数决定,而ref clk和clk out都是可以自己选的,建议reference clk和fabric clk配置成一样的频率

在这里由于LTE 5G系统里通信系统的标准采样基准是30.72*N MHz,所以这里选用3.93216ghz作为采样率来往下配置下面的频率

下一篇会讲解如何通过TICS PRO这个软件配置上述时钟

总结

所以在IP核中,时钟的结构是这样的四层结构