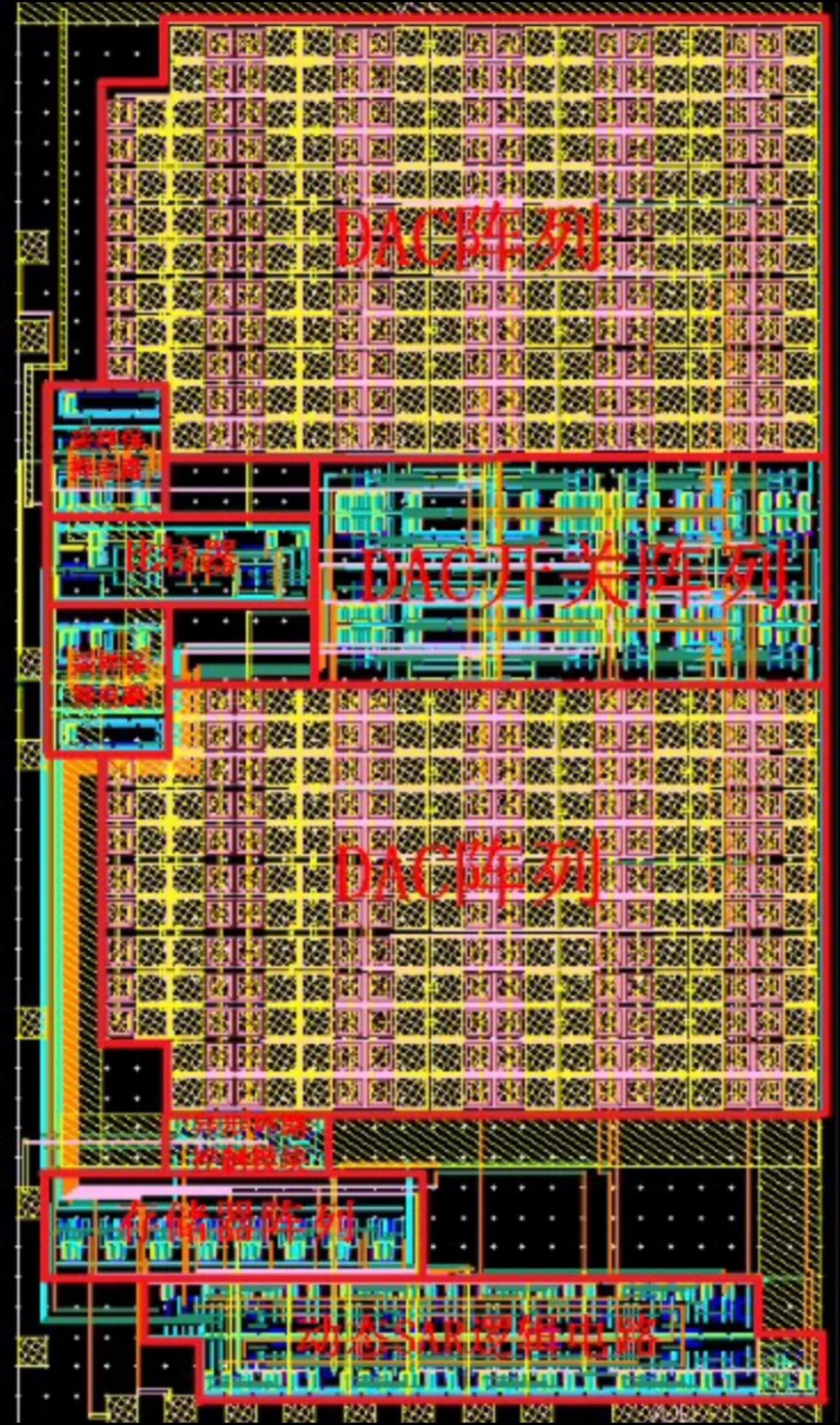

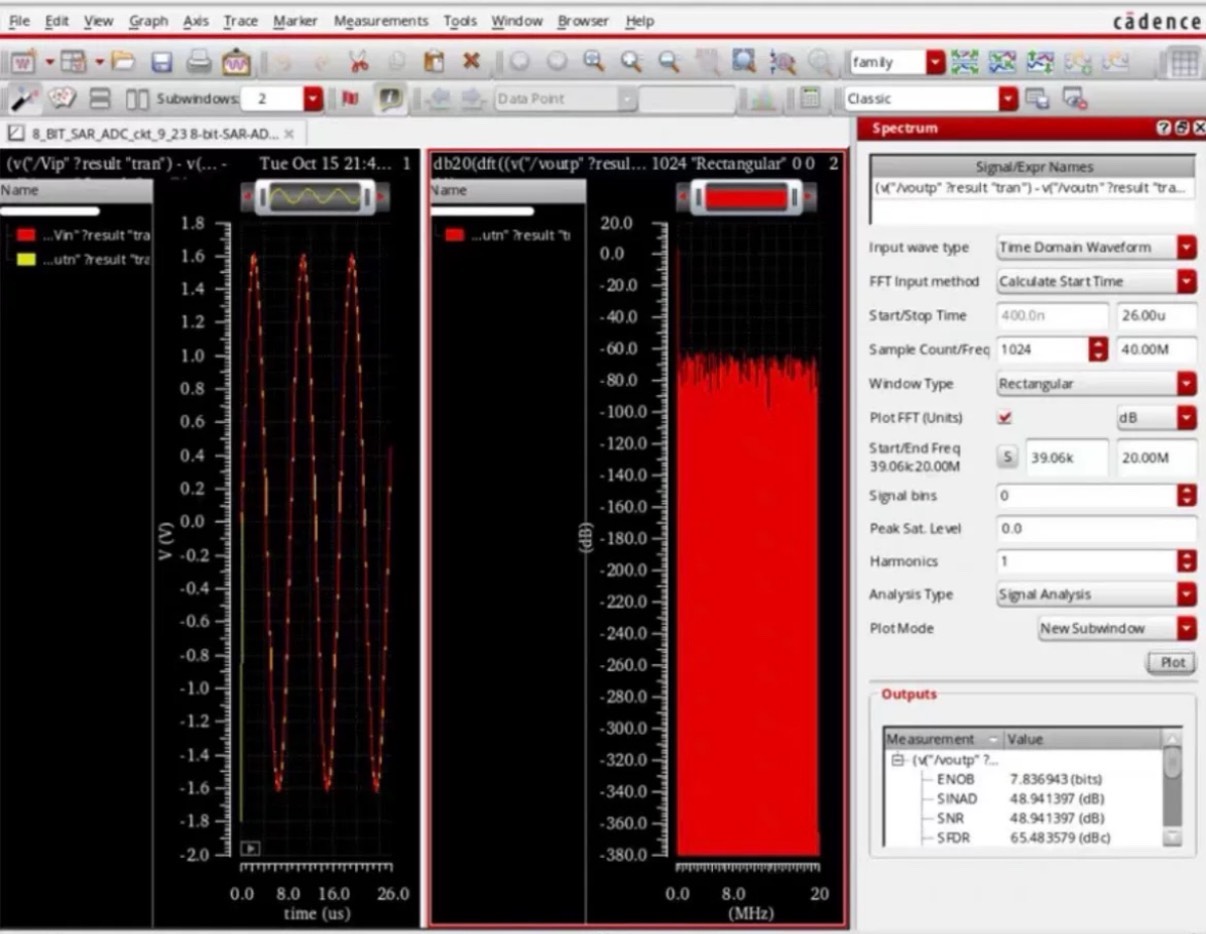

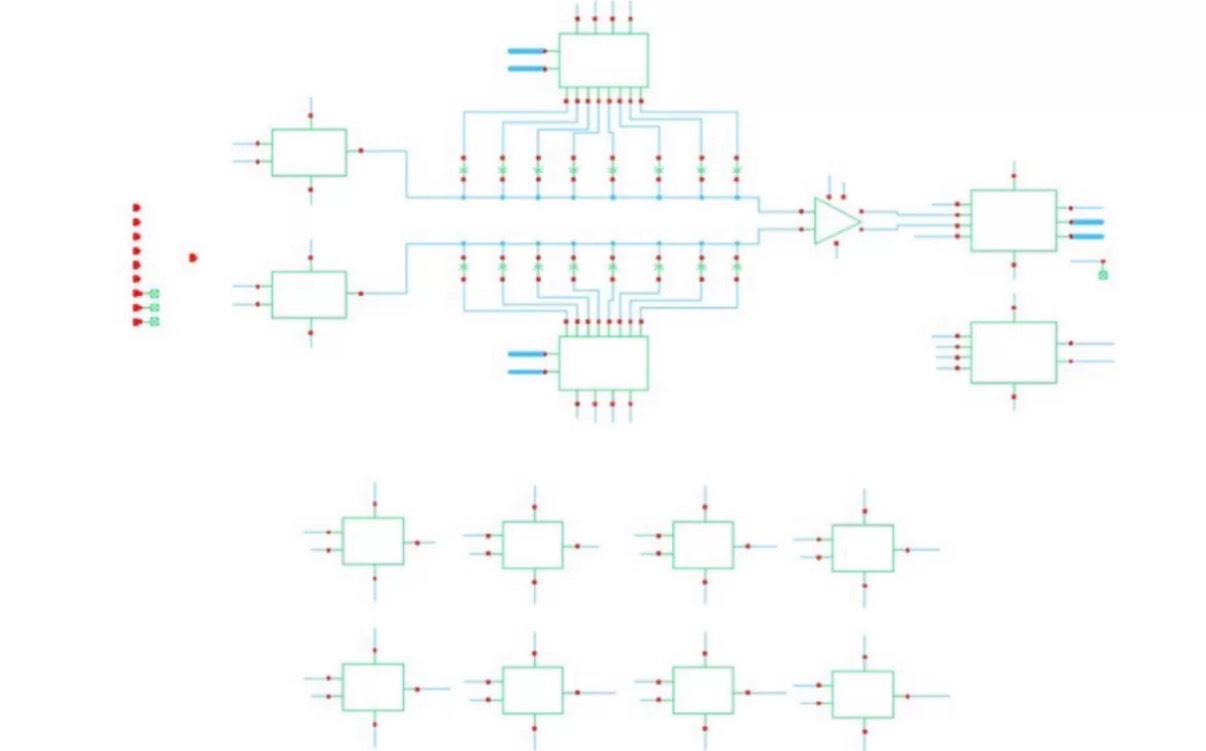

已经完成的流片项目8bit 40M采样频率 异步SAR ADC设计 包括核心电路的原理图和版图(DRC LVS ANT都过了)有测试电路和后仿文件 带详细设计仿真文档 smic18mmrf工艺,有工艺库,有电路工程文件,提供仿真状态,可以直接导入自己的cadence运行仿真 前仿有效位数ENOB=7.84(电路里新的ADE可以到7.94) 后仿ENOB7.377,适合入门SAR ADC 顶层电路包括: 栅压自举开关Bootstrap Vcm_Based开关时序 上级板采样差分CDAC阵列 两级动态比较器 比较器高速异步时钟 动态sar逻辑 8位DFF输出 8位理想DAC。 带详细说明,告诉你各个模块怎么设计,原理是什么,有哪些注意事项,怎么仿真,包看包会。 包括详细仿真文档,原理介绍,完整电路图,仿真参数已设好,可直接使用,在自己的电脑上就可以运行仿真。

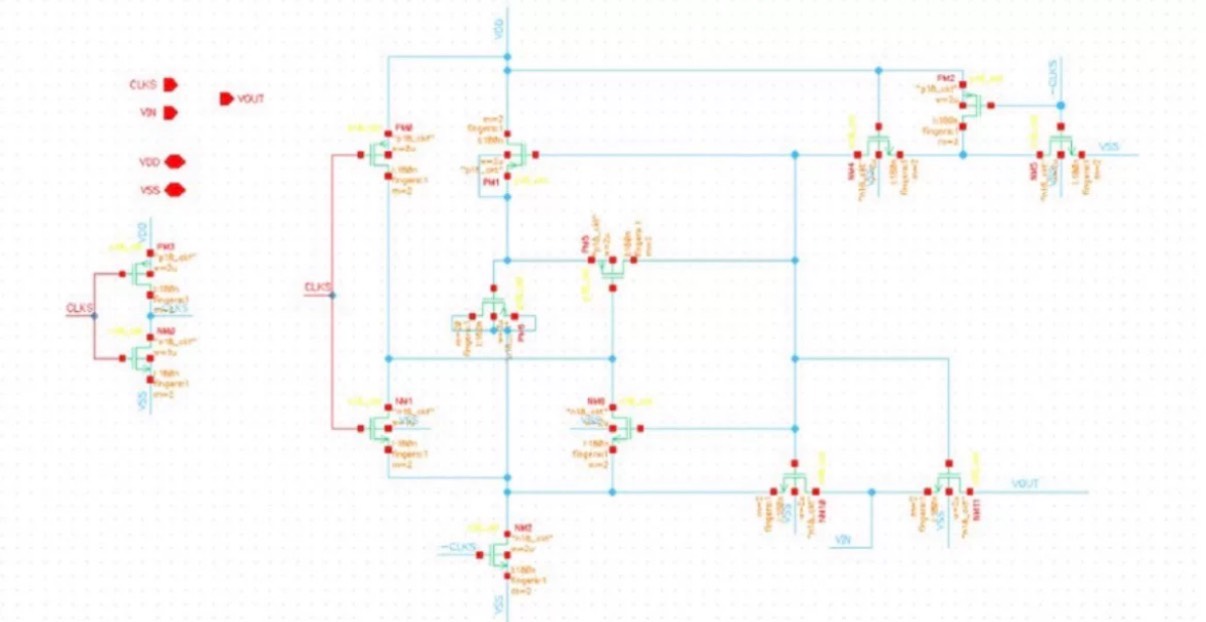

这玩意儿做起来是真上头。咱们直接说干货,这个40M采样的8bit异步SAR ADC,核心就靠四个字------动态互怼。先看这个栅压自举开关,这货是采样质量的门神。用交叉耦合的PMOS/NMOS组合,关键得让栅源电压随输入信号浮动。代码里这个boot_clock信号得特别注意上升沿斜率,不然电荷注入能把ENOB直接干下去0.2bit。

CDAC阵列玩的是跷跷板游戏,这里用的Vcm-Based结构省了俩电容。看这段switch控制代码:

always @(posedge clk) begin

sampphase <= ~compout;

dacctrl <= sampphase ? vcm : vref;

end

这个时序控制要是差了200ps,DNL直接崩给你看。建议跑蒙特卡洛的时候把工艺角开到SS_125,这时候INL还能保持在±0.8LSB以内。

比较器就是个暴脾气,两级动态结构得把preamp增益控在15dB左右。注意看这个再生阶段的时序:

assign latchen = asyncclk & ~reset;

总延迟要压在1.2ns以内,不然采样窗口关门前结果出不来。实测过当输入差分电压到0.8mV时,误判率会飙到3%,所以前仿得把失调电压校准到±5mV范围。

异步时钟生成是精髓所在,这个环形振荡器代码:

module asyncclkgen(

input comp_ready,

output logic clk_phase

);

always @(negedge comp_ready) begin

#1.7 clkphase <= ~clkphase; // 工艺相关延迟

end

endmodule

1.7ns的延迟参数得根据实际布线调整,后仿时候要特别注意clock jitter对ENOB的影响。实测当电源噪声超过50mVpp时,采样率得降到35M才能保证7bit有效位数。

仿真文档里有个彩蛋------在testbench目录下藏了个noiseinject.pl脚本,运行perl noiseinject.pl -mode random能模拟电源干扰。跑完看眼图会发现当噪声频率接近20MHz时,谐波失真会突然增大,这时候得回去调电源去耦电容的位置。

最后说个骚操作:把DFF输出接的ideal DAC换成实际电路时,记得在tb里加上这段代码:

initial begin

force tb.adctop.dacmodel.resolution = 8;

#100 release tb.adctop.dacmodel.resolution;

end

这是对付某些仿真器单位初始化问题的祖传偏方。整个工程在i5-8265U上跑完所有corner大概要6小时,建议用nohup挂后台,别傻等着。

实测数据挺有意思:当输入信号频率到18MHz时ENOB开始跳水,这时候把采样率降到32M又能回血到7.2bit。这说明工艺的寄生电容比想象中猛,下次改版得在CDAC的顶板走线上加shielding。整套资料已经打包成docker镜像,新人用cadence -i sar_adc.img直接开搞,连PDK都封装好了,绝对不坑队友。