1、简介

在实际的驱动开发中, 涉及到的网络硬件知识和缩写,总是记不住,现在写一篇文章,用于记录硬件组成和连接接口,包括接口缩写的全程介绍。

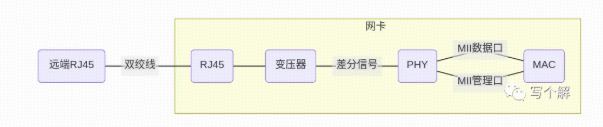

2、MAC和PHY 的系统连接图

2.1 网卡的基本组成单元4个:MAC、PHY、变压器、RJ45。

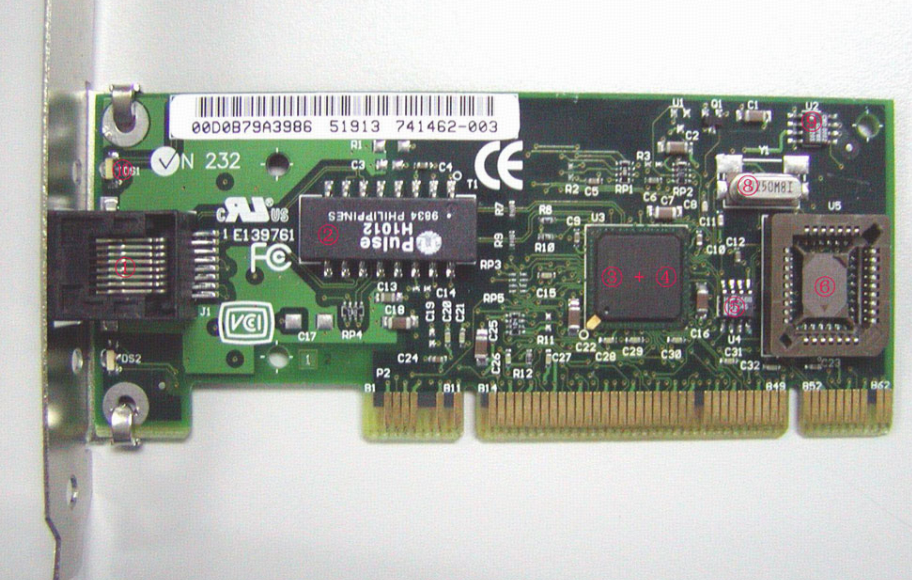

MAC和PHY集成在一颗芯片的以太网卡:

上图中各部件为:

①RJ-45接口

②Transformer(隔离变压器)

③PHY芯片

④MAC芯片

⑤EEPROM

⑥BOOTROM插槽

⑧晶振

⑨电压转换芯片

⑩LED指示灯

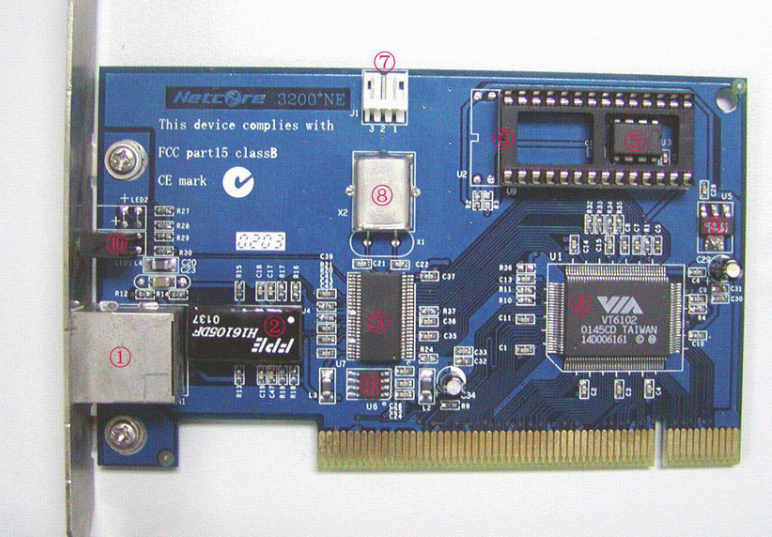

MAC和PHY分开的以太网卡:

上图中各部件为:

①RJ-45接口

②Transformer(隔离变压器)

③PHY芯片

④MAC芯片

⑤EEPROM

⑥BOOTROM插槽

⑦WOL接头

⑧晶振

⑨电压转换芯片

⑩LED指示灯

框图里舍去晶振、电源、存储设备、LED等外设,根据方案差异,某些数字电路部分不同程度的整合到一个芯片内。

基本链路流程:

网卡上至少有两个LED灯,分别表示Link(链路正常)和数据传输或数据速率选择(10M/100M)。

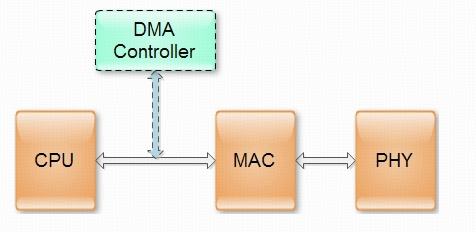

2.2 系统框图

对于上述的三部分,并不一定都是独立的芯片,根据组合形式,可分为下列几种类型:

- CPU集成MAC与PHY;

- CPU集成MAC,PHY采用独立芯片;

- CPU不集成MAC与PHY,MAC与PHY采用集成芯片;

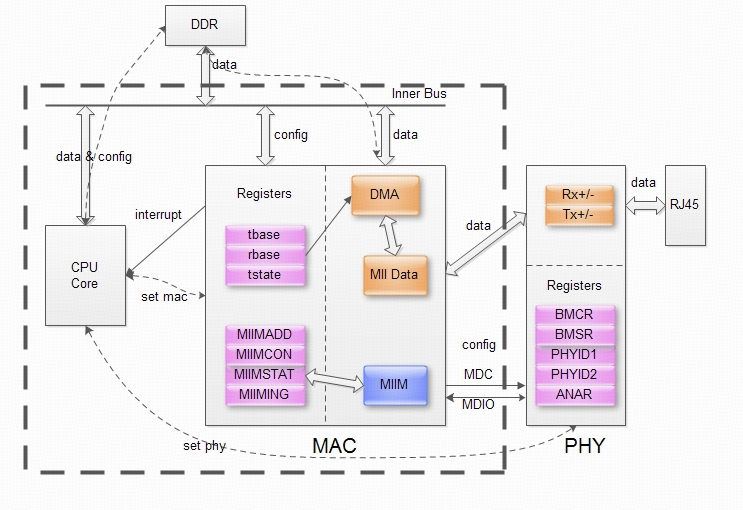

下图是采用方案二的网络硬件结构图.虚框表示CPU,MAC集成在CPU中.PHY芯片通过MII接口与CPU上的Mac连接.

在软件上对网口的操作通常分为下面几步:

- 为数据收发分配内存;

- 初始化MAC寄存器;

- 初始化PHY寄存器(通过MIIM);

- 启动收发;

3、网络硬件术语缩写

| 缩写 | 英文全称 | 中文全称 | 主要应用和描述 |

|---|---|---|---|

| MAC | Media Access Control | 介质访问控制层 | 数据链路层的下半部分。负责: • 帧组装/解组装 :将数据封装成帧或从帧中提取数据。 • 寻址 :添加源和目的 MAC 地址。 • 错误检测 :通常通过帧校验序列(FCS)。 • 信道访问控制:控制设备何时在共享介质上发送数据(如 CSMA/CD, CSMA/CA)。 |

| PHY | Physical Layer | 物理层 | OSI模型的最底层。负责: • 编解码 :将数字比特转换为适合在物理介质上传输的信号(如曼彻斯特编码, PAM4)。 • 收发信号 :实际驱动信号通过电缆、光纤或无线电磁波。 • 链路建立与同步:建立和维护物理连接。 |

| MII | Media Independent Interface | 介质无关接口 | 经典以太网(10/100Mbps)的标准接口。它将 MAC 与各种类型的 PHY(铜缆、光纤)连接起来,实现"介质无关"。 |

| RMII | Reduced Media Independent Interface | 精简介质无关接口 | MII 的简化版本。引脚数减少一半,同样支持 10/100Mbps。成本更低,但时序要求更严格。 |

| GMII | Gigabit Media Independent Interface | 千兆介质无关接口 | 用于 千兆以太网(1000Mbps)。数据通道比 MII 更宽,以支持更高的速率。 |

| RGMII | Reduced Gigabit Media Independent Interface | 精简千兆介质无关接口 | 最常用的千兆以太网接口。GMII 的简化版,引脚数减少约一半,通过双边沿采样(DDR)技术实现。 |

| SGMII | Serial Gigabit Media Independent Interface | 串行千兆介质无关接口 | 一种串行接口(与上述并行接口相对)。引脚数更少,速率适应性更强,常用于连接 MAC 和交换机芯片,或用于 1G/2.5G 应用。 |

| XGMII | 10 Gigabit Media Independent Interface | 万兆介质无关接口 | 用于 10G 以太网 的标准并行接口。数据通道很宽,引脚数多,通常用于芯片内部或极短距离连接。 |

| XAUI | XGMII Extender Sublayer | XGMII 扩展子层接口 | 一种串行接口,用于扩展 XGMII。通常通过光纤或背板传输,比 XGMII 的传输距离更长。发音为 "Zowie"。 |

| USXGMII | Universal Serial 10 Gigabit Media Independent Interface | 通用串行万兆介质无关接口 | 一种通用的串行接口,支持从 10Mbps 到 10Gbps 的多种速率,旨在取代 SGMII、XSGMII 和 XAUI 等。 |

| SerDes | Serializer/Deserializer | 串行器/解串器 | 这不是一个标准化的接口"名字",而是一种关键技术。许多高速接口(如 SGMII, XAUI, PCIe, SATA)在物理层面都使用 SerDes 技术将并行数据转换为高速串行流进行传输。 |

| PCS | Physical Coding Sublayer | 物理编码子层 | 功能: 处理与 MAC 层的接口(如 MII, RGMII, SGMII)并进行编解码 。 • 发送方向: 从 MAC 接收数据,进行扰码 (避免长串的0或1),然后转换成适合通道的编码(如对于千兆以太网的 8B/10B 编码,对于万兆的 64B/66B 编码)。 • 接收方向: 执行相反的过程,包括解码、解扰,并将数据传递给 MAC。 • 自协商: 通常也由 PCS 层管理,用于与链路对端协商速率、双工模式等能力。 |

| PMA | Physical Medium Attachment | 物理介质附着子层 | 功能: 位于 PCS 和 PMD 之间,进行并串/串并转换。 • 发送方向: 将 PCS 传来的并行编码数据,通过 SerDes 转换为高速串行数据流。 • 接收方向: 将 PMD 传来的高速串行数据流,通过 CDR 恢复出时钟和数据,并将其转换为并行数据送给 PCS。 |

| PMD | Physical Medium Dependent | 物理介质相关子层 | 功能: 驱动物理介质(发送)和感知物理介质上的信号(接收)。 • 发送方向: 将 PMA 传来的串行比特流,转换成在特定介质上传输的 electrical levels 或 optical modulation。 • 接收方向: 感知介质上的信号,并将其转换为比特流送给 PMA。 |

| MDI | Medium Dependent Interface | 介质相关接口 | 这实际上是芯片的外部引脚 ,是信号物理离开芯片的接口。对于铜缆以太网,MDI 就是连接至网络变压器 和 RJ-45 接口 的引脚。 |

| Auto-Negotiation | 自协商 | 虽然逻辑上属于 PCS,但它是一个关键功能。PHY 通过发送特定的脉冲序列,与链路对端的设备(如交换机)自动协商出双方都支持的最高性能模式(速率、全双工/半双工)。 | |

| CSMA/CD | Carrier Sense Multiple Access with Collision Detection | 载波侦听多路访问/冲突检测 | * 载波侦听 : 在发送数据之前,以及发送过程中,站点会持续监听共享传输介质(如同轴电缆)上是否有其他站点正在发送信号(即"载波")。 * 多路访问 : 多个网络设备(站点)共同连接在同一个共享介质上,所有站点都有平等的权利访问这个介质。 * 冲突检测 : 如果检测到有两个或更多的站点同时 在发送数据,导致了信号冲突(即"碰撞"),那么所有正在发送的站点都会立即停止发送。 * 简单来说,CSMA/CD 是一种用来管理多个设备如何共享同一根"线路"进行通信的"交通规则",它主要应用于早期的以太网中。 * CSMA/CD 的工作流程可以概括为 "先听后发、边发边听、冲突退避" 这十二个字 * CSMA/CD 在现代网络中已经基本被淘汰,主要原因如下: * 基本已过时 。由于全双工通信 和交换机的全面普及,冲突域被缩小到单个端口,CSMA/CD已无必要。在现代千兆以太网(1000BASE-T)及更高速率的标准中,CSMA/CD仅作为可选功能或已被移除。 |

4、MAC组成

4.1 MAC控制器内部电路组成

这部分都是硬件设计, 以符合MAC协议。后面补充。

4.2 什么是MAC?

首先我们来说说以太网卡的MAC芯片的功能。以太网数据链路层其实包含MAC(介质访问控制)子层和LLC(逻辑链路控制)子层。一块以太网卡MAC芯片不但要实现MAC子层和LLC子层的功能,还要提供符合规范的PCI界面以实现和主机的数据交换。

MAC从PCI总线(或者是AXI总线)收到IP数据包(或者其他网络层协议的数据包)后,将之拆分并重新打包成最大1518Byte,最小64Byte的帧。这个帧里面包括了目标MAC地址、自己的源MAC地址和数据包里面的协议类型(比如IP数据包的类型用80表示),最后还有一个DWORD(4Byte)的CRC码。

可是目标的MAC地址是哪里来的呢?这牵扯到一个ARP协议(介乎于网络层和数据链路层的一个协议)。第一次传送某个目的IP地址的数据的时候,先会发出一个ARP包,其MAC的目标地址是广播地址,里面说到:"谁是这个IP地址的主人?"因为是广播包,所有这个局域网的主机都收到了这个ARP请求。收到请求的主机将这个IP地址和自己的相比较,如果不相同就不予理会,如果相同就发出ARP响应包。这个IP地址的主机收到这个ARP请求包后回复的ARP响应里说到:"我是这个IP地址的主人"。这个包里面就包括了他的MAC地址。以后的给这个IP地址的帧的目标MAC地址就被确定了。(其它的协议如IPX/SPX也有相应的协议完成这些操作。)

IP地址和MAC地址之间的关联关系保存在主机系统里面,叫做ARP表,由驱动程序和操作系统完成。在Microsoft的系统里面可以用 arp -a 的命令查看ARP表。收到数据帧的时候也是一样,做完CRC以后,如果没有CRC效验错误,就把帧头去掉,把数据包拿出来通过标准的借口传递给驱动和上层的协议客栈,最终正确的达到我们的应用程序。还有一些控制帧,例如流控帧也需要MAC直接识别并执行相应的行为。

以太网MAC芯片的一端接计算机PCI总线,另外一端就接到PHY芯片上。以太网的物理层又包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。而PHY芯片是实现物理层的重要功能器件之一,实现了前面物理层的所有的子层的功能。

4.3 MAC是OSI模型中功能

MAC属于OSI七层网络模型中的数据链路层。数据链路层其实包含MAC(介质访问控制)子层和LLC(逻辑链路控制)子层。

重点: MAC以上的层是内核软件协议栈,MAC以下包括MAC是网络协议硬件。MAC驱动仅仅是把数据地址告诉DMA,MAC才是网络协议中重要的部分,是如何把数据组成网络协议帧,都是这个MAC控制器实现的。phy仅仅是传输数据,对phy来说,都是数据,不管地址还是CRC。

MAC的功能之一:把数据封装成帧, 包括对帧进行界定, 实现帧同步, 对目的MAC地址和源MAC地址进行处理, 在与PHY发生传输错误时对帧进行处理。

MAC的功能之二:对PHY的进行控制

5、PHY的组成

物理层位于OSI最底层,物理层协议定义电气信号、线的状态、时钟要求、数据编码和数据传输用的连接器。 物理层的器件称为PHY。

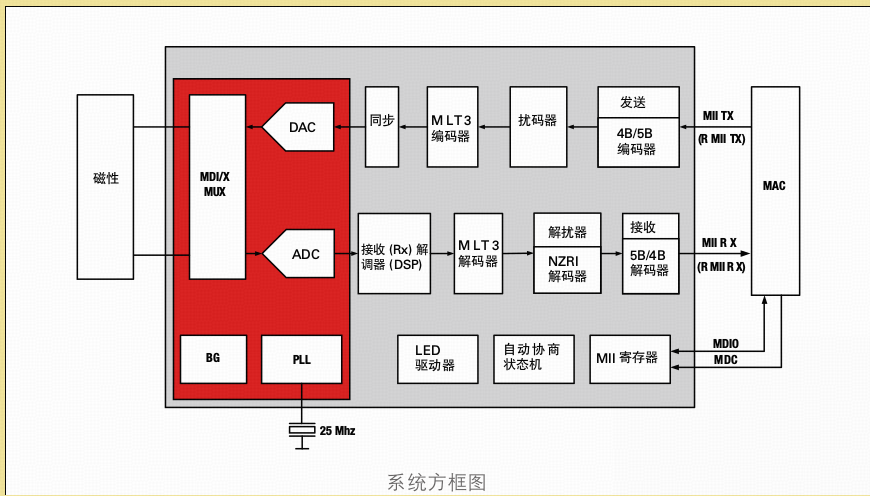

5.1 PHY组成的系统框图

上图里的灰色方框图里的就是PHY芯片内部模块图。 MAC器件通过MII接口来与PHY进行数据交换。 从图中可以看到向外发送数据和从外部接收数据时PHY所要做的一些工作。 可以简单理解成:

- 向外部发送数据时, MAC通过MII向PHY传送数据, 这些数据通过编码等处理, 最后再转成模拟信号发送出去。

- 从外部接收数据时,模拟信号先转成数字信号,再经过解码得到数据, 经过MII送到MAC。

IEEE-802.3标准定义了以太网PHY包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。

5.2 PHY数据传输的流程

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC),每4bit就增加1bit的检错码,然后把并行数据转化为串行流数据,再按照物理层的编码规则(10Based-T的NRZ编码或100based-T的曼彻斯特编码)把数据编码,再变为模拟信号把数据送出去。收数据时的流程反之。

PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两块网卡碰巧同时送出数据,那将造成冲突,这时冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

许多网友在接入Internt宽带时,喜欢使用"抢线"强的网卡,就是因为不同的PHY碰撞后计算随机时间的方法设计上不同,使得有些网卡比较"占便宜"。不过,抢线只对广播域的网络而言的,对于交换网络和ADSL这样点到点连接到局端设备的接入方式没什么意义,而且"抢线"也只是相对而言的,不会有质的变化。

PHY还提供了和对端设备连接的重要功能并通过LED灯显示出自己目前的连接的状态和工作状态让我们知道。当我们给网卡接入网线的时候,PHY不断发出的脉冲信号检测到对端有设备,它们通过标准的"语言"交流,互相协商并却定连接速度、双工模式、是否采用流控等。通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为AutoNegotiation或者NWAY,它们是一个意思--自动协商。

具体传输过程为,发送数据时,网卡首先侦听介质上是否有载波(载波由电压指示),如果有,则认为其他站点正在传送信息,继续侦听介质。一旦通信介质在一定时间段内(称为帧间缝隙IFG=9.6微秒)是安静的,即没有被其他站点占用,则开始进行帧数据发送,同时继续侦听通信介质,以检测冲突。在发送数据期间,如果检测到冲突,则立即停止该次发送,并向介质发送一个"阻塞"信号,告知其他站点已经发生冲突,从而丢弃那些可能一直在接收的受到损坏的帧数据,并等待一段随机时间(CSMA/CD确定等待时间的算法是二进制指数退避算法)。在等待一段随机时间后,再进行新的发送。如果重传多次后(大于16次)仍发生冲突,就放弃发送。接收时,网卡浏览介质上传输的每个帧,如果其长度小于64字节,则认为是冲突碎片。如果接收到的帧不是冲突碎片且目的地址是本地地址,则对帧进行完整性校验,如果帧长度大于1518字节(称为超长帧,可能由错误的LAN驱动程序或干扰造成)或未能通过CRC校验,则认为该帧发生了畸变。通过校验的帧被认为是有效的,网卡将它接收下来进行本地处理。

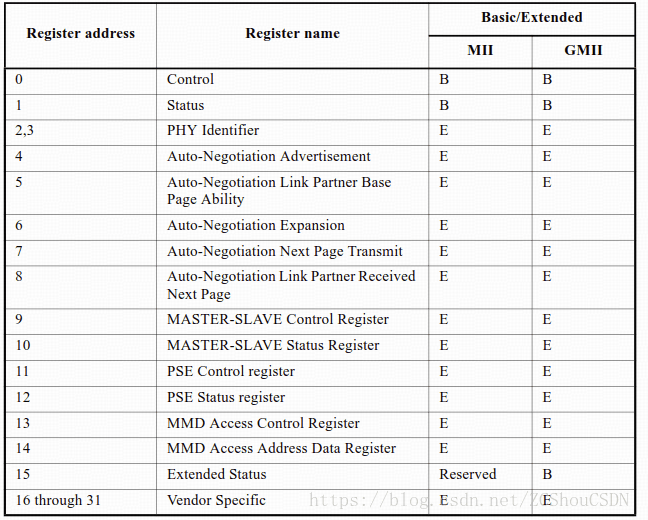

5.3 PHY寄存器

PHY寄存器的地址空间为5位,从0到31最多可以定义32个寄存器(随着芯片功能不断增加,很多PHY芯片采用分页技术来扩展地址空间以定义更多的寄存器),IEEE802.3定义了地址为0-15这16个寄存器的功能,地址16-31的寄存器留给芯片制造商自由定义,如下表所示。

(1)官方介绍请参考IEEE802.3标准的 22.2.4 Management functions 节。

(2)上图的B和E表示了,在特定接口下,寄存器是基本的还是扩展的。例如:MII接口下只有0和1寄存器是基本的,其它的是扩展的。注意:所为扩展是指留给IEEE以后的扩展特性用,不是给PHY厂商的扩展,PHY厂商自定义的只能是16~31号寄存器

(3)在IEEE标准文档及某些PHY手册中,某寄存器的比特(bit)用X.y表示,如0.15表示第0寄存器的第15位。

参考具体网友对寄存器的解释:

以太网详解(一)-MAC/PHY/MII/RMII/GMII/RGMII基本介绍(转) - 二虎 - 博客园

仅靠这 16个寄存器完全可以驱动起PHY芯片,至少能保证基本的网络数据通信。因此 Linux 内核有通用 PHY 驱动,按道理来讲,不管你使用的哪个厂家的 PHY 芯片,都可以使用 Linux 的这个通用 PHY 驱动来验证网络工作是否正常。事实上在实际开发中可能会遇到一些其他的问题导致 Linux 内核的通用 PHY 驱动工作不正常,这个时候就需要驱动开发人员去调试了。

随着现在PHY芯片性能越来越强大,32个寄存器已经无法满足厂商的需求,因此很多厂商采用了分页机制来开展寄存器地址空间,以求定义更多的寄存器。这些多出来的几次器可以实现厂商特有的一些技术,因此在Linux内核里面可以看到很多具体的PHY芯片驱动源码。

6、MDI

MDI口是快速以太网100BASE-T定义的与介质有关接口(Media Dependent Interface)。MDI是指通过收发器发送的100BASE-T信号,即100BASE-TX、FX、T4或T2信号。将集线器连接网络接口卡时,其发送和接收对通常是相互连接的。集线器之间连接时,通常需要一条跨接电缆,其中的发送和接收对是反接的。MDI是正常的UTP或STP连接,而MDI-X连接器的发送和接收对是在内部反接的,这就使得不同的设备(如集线器-集线器或集电器-交换机),可以利用常规的UTP或STP电缆实现背靠背的级联。"

7、MAC和PHY接口类型

MAC与PHY之间通过两个接口连接,分别为控制接口和数据接口。

- 传输数据的接口:MII叫做介质独立接口,以太网MAC通过该接口发出数据帧经过PHY后传输到其他网络节点上,同时其他网络节点的数据先经过PHY后再由MAC接收;

- MAC控制PHY的接口:SMI叫做是串行管理接口,以太网MAC通过该接口可以访问PHY的寄存器,通过对这些寄存器操作可对PHY进行控制和管理。

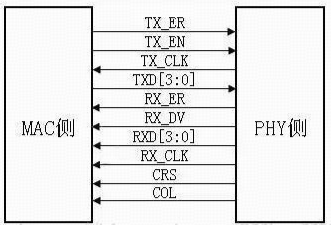

7.1 MII接口

MII(Media Independent Interface)即媒体独立接口,MII接口是MAC与PHY连接的标准接口。它是IEEE-802.3定义的以太网行业标准。MII接口提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术,该接口支持10Mb/s与100Mb/s的数据传输速率,数据传输的位宽为4位。媒体独立表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作,802.3协议最多支持32个PHY,但有一定的限制:要符合协议要求的connector特性。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。MII接口有MII、RMII、SMII、SSMII、SSSMII、GMII、SGMII、RGMII等.

MII接口主要包括以下三个部分:

- 从MAC层到PHY层的发送数据接口

- 从PHY层到MAC层的接收数据接口

- 从MAC层和PHY层之间寄存器控制和信息获取的MDIO接口

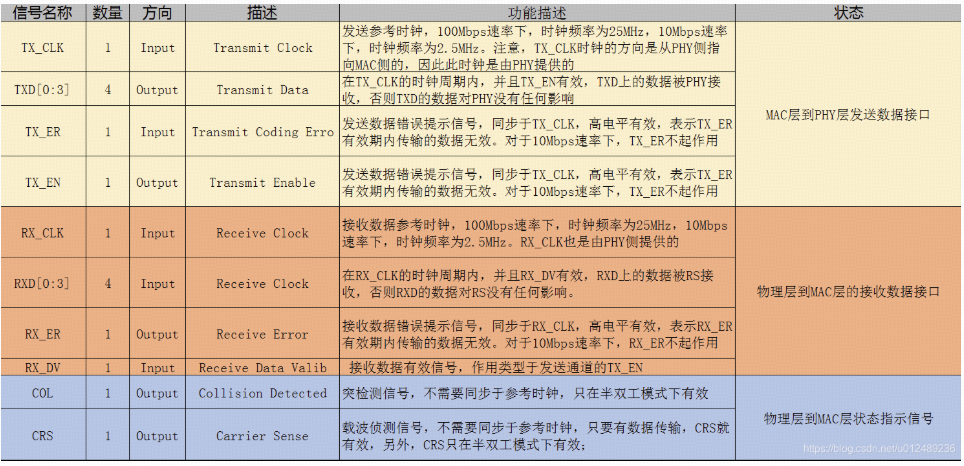

MII接口如下:

首先来看看MII的MAC层定义接口:

MII 数据接口总共需要 16 个信号,包括 TX_ER,TXD[3:0],TX_EN,TX_CLK,COL,RXD[3:0],RX_ER,RX_CLK,CRS,RX_DV 等。MII的时钟为25MHz,传输速率为10/100Mbps。所以MII的特性如下:

- 支持10Mb/s和100Mb/s的数据速率

- 100M工作模式下,参考时钟是25MHz;10M工作模式下,信号参考时钟是2.5MHz

- 支持全双工、半双工两种工作模式

- 发送和接收数据时采用,4bit方式

MII接口的信号说明:

- 数据接口: 包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号,包括

- TX_ER(transmit coding error): TX_ER同步于TX_CLK,在数据传输过程中,如果TX_ER有效超过一个时钟周期,并且此时TX_EN是有效的,则数据通道中传输的数据是无效的,没用的。注:当TX_ER有效并不影响工作在10Mb/s的PHY或者TX_EN无效时的数据传输。在MII接口的连线中,如果TX_ER信号线没有用到,必须将它下拉接地。

- TXD<3:0>(transmit data): TXD由RS驱动,同步于TX_CLK,在TX_CLK的时钟周期内,并且TX_EN有效,TXD上的数据被PHY接收,否则TXD的数据对PHY没有任何影响。

- TX_EN: 发送使能。TX_EN由Reconciliation子层根据TX_CLK上升沿同步进行转换,时序如图22-16所示。

- TX_CLK(transmit clock): TX_CLK (Transmit Clock)是一个连续的时钟信号(即系统启动,该信号就一直存在),它是TX_EN, TXD, and TX_ER(信号方向为从RS到PHY)的参考时钟,TX_CLK由PHY驱动TX_CLK的时钟频率是数据传输速率的25%,偏差±100ppm。例如,100Mb/s模式下,TX_CLK时钟频率为25MHz,占空比在35%至65%之间。

- COL(collision detected): COL不需要同步于参考时钟。The behavior of the COL signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation。即半双工模式信号有效,全双工模式信号无效。

- RXD<3:0>(receive data): RXD由RS驱动,同步于RX_CLK,在RX_CLK的时钟周期内,并且RX_DV有效,RXD上的数据被RS接收,否则RXD的数据对RS没有任何影响。While RX_DV is de-asserted, the PHY may provide a False Carrier indication by asserting the RX_ER signal while driving the value <1110> onto RXD<3:0>。

- RX_ER(receive error): RX_ER同步于RX_CLK,其在RX通道中的作用类似于TX_ER对于TX通道数据传输的影响。

- RX_CLK: 它与TX_CLK具有相同的要求,所不同的是它是RX_DV, RXD, and RX_ER(信号方向是从PHY到RS)的参考时钟。RX_CLK同样是由PHY驱动,PHY可能从接收到的数据中提取时钟RX_CLK,也有可能从一个名义上的参考时钟(e.g., the TX_CLK reference)来驱动RX_CLK。

- CRS(carrier sense): CRS不需要同步于参考时钟,只要通道存在发送或者接收过程,CRS就需要有效。The behavior of the CRS signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation,即半双工模式信号有效,全双工模式信号无效。

- RX_DV(Receive Data Valid): RXD_DV同步于RX_CLK,被PHY驱动,它的作用如同于发送通道中的TX_EN,不同的是在时序上稍有一点差别:为了让数据能够成功被RS接收,要求RXD_DV有效的时间必须覆盖整个FRAME的过程,即starting no later than the Start Frame Delimiter (SFD) and excluding any End-of-Frame delimiter。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。 - MII管理接口: 是个双信号接口,通过管理接口,MAC就能监视和控制PHY。其管理是使用SMI(Serial Management Interface) 总线通过读写PHY的寄存器来完成的。一个是时钟信号(***MDC (management data clock)***)。另一个是数据信号(***MDIO (management data input/output)***)。

- MDC: 由站管理实体向PHY提供,作为在MDIO信号上传送信息的定时参考。 MDC是一种非周期性的信号,没有最高或最低时间。 无论TX_CLK和RX_CLK的标称周期如何,MDC的最小高低时间应为160 ns,MDC的最小周期为400 ns。

- MDIO: 是PHY和STA之间的双向信号。 它用于在PHY和STA之间传输控制信息和状态。 控制信息由STA同步地针对MDC驱动并且由PHY同步地采样。 状态信息由PHY针对MDC同步驱动并由STA同步采样。

PHY 里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC 通过SMI 总线不断的读取PHY 的状态寄存器以得知目前PHY 的状态。例如连接速度、双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的。例如流控的打开关闭、自协商模式还是强制模式等。不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是由IEEE的规范的。因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

MII支持10Mbps和100Mbps的操作,一个接口由14根线组成,它的支持还是比较灵活的。但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线。一般按照这个接口做交换机是不太现实的。所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

一个端口就是一组MII数据接口负责。

7.2 RMII(Reduced Media Independant Interface)

简化媒体独立接口是标准的以太网接口之一,比MII有更少的I/O传输。RMII口是用两根线来传输数据的,MII口是用4根线来传输数据的,GMII是用8根线来传输数据的。MII/RMII只是一种接口,对于10Mbps线速,MII的时钟速率是2.5MHz就可以了,RMII则需要5MHz;对于100Mbps线速,MII需要的时钟速率是25MHz,RMII则是50MHz。

MII/RMII用于传输以太网包,在MII/RMII接口是4/2bit的,在以太网的PHY里需要做串并转换,编解码等才能在双绞线和光纤上进行传输,其帧格式遵循IEEE 802.3(10M)/IEEE 802.3u(100M)/IEEE 802.1q(VLAN)。以太网帧的格式为:前导符+开始位+目的mac地址+源mac地址+类型/长度+数据+padding(optional)+32bitCRC。如果有vlan,则要在类型/长度后面加上2个字节的vlan tag,其中12bit来表示vlan id,另外4bit表示数据的优先级!

7.3 GMII(Gigabit MII)

后来为了支持千兆网口,也就开始有了千兆网的MII接口,也就是GMII接口。现在比较常用的是RGMII,减小了MAC和PHY之间的引脚数量。数据信号和控制信号混合在一起,并且在工作时钟的上升沿和下降沿同时采样,其对应关系图如下:

- 10M带宽对应的是2.5MHz,因为4bit*2.5M=10Mbps

- 100M带宽对应的是25MHz,因为4bit*25M=100Mbps

- GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps,8bit*125M = 1000Mbps

GMII硬件设计以太网标准接口:

- 发送器: 在千兆速率下,向PHY提供GTXCLK信号、TXD、TXEN、TXER信号与此时钟信号同步。否则在10/100Mbps速率下,PHY提供TXCLK时钟信号,其它信号与此信号同步。其工作频率为25MHz(100M网络)或2.5MHz(10M网络)。

- GTXCLK------吉比特TX...信号的时钟信号(125MHz)

- TXCLK------10/100Mbps信号时钟

- TXD[7...0]------被发送数据 (8位)

- TXEN------发送器使能信号

- TXER------发送器错误(用于破坏一个数据包)

- 接收器:

- RXCLK------接收时钟信号(从收到的数据中提取,因此与GTXCLK无关联)

- RXD[7...0]------接收数据 (8位)

- RXDV------接收数据有效指示

- RXER------接收数据出错指示

- COL------冲突检测(仅用于半双工状态)

- 管理配置: 管理配置接口控制PHY的特性。该接口有32个寄存器地址,每个地址16位。其中前16个已经在"IEEE 802.3,2000-22.2.4 Management Functions"中规定了用途,其余的则由各器件自己指定。

- MDC------配置接口时钟

- MDIO------配置接口I/O

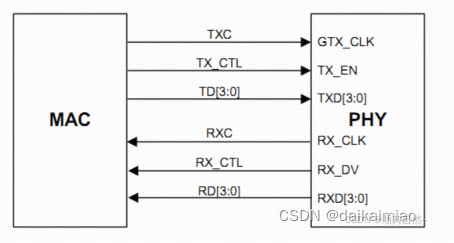

7.4 RGMII (Reduced Gigabit MII )

精简千兆媒体独立接口,现在比较常用的是RGMII,减小了MAC和PHY之间的引脚数量。数据信号和控制信号混合在一起,并且在工作时钟的上升沿和下降沿同时采样,其对应关系图如下:

- 10M带宽对应的是2.5MHz,因为4bit*2.5M=10Mbps

- 100M带宽对应的是25MHz,因为4bit*25M=100Mbps

- 1000M带宽对应的是125MHz,因为250MHz频率太高,所以采用双边沿采样技术(会带来设计复杂度)。4bit125M2=1000Mbps 。

Reduced GMII,GMII采用8位数据传输,RGMII采用4位数据传输,所以这个按字面意思理解就是减少的GMII。这个是因为RGMII在时钟的上升沿和下降沿均采样数据,所以数据位减少一般的情况下还是可以达到千兆的速率。其工作时钟125兆,兼容MII规定的10/100Mbps,

RX_CTL-:接收数据控制信号。

RD:四位并行的接收数据线。

TX_CTL:发送数据控制信号。

TD:四位并行的发送数据线。

由GMII的24线简化为14线,TX/RX数据宽度从8为变为4位。

使能和error合到一根线上:

TX_EN信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,下降沿发送TX_ER;RX同理。

7.5 接口类型对比

| 接口 | 引脚 | 速度支持(Mbps) | 利 | 弊 |

|---|---|---|---|---|

| MII | RX_D[3:0] RX_CLK, RX_DV, CRS, COL TX_D[3:0], TX_CLK, TX_EN (14) | 10, 100 | 普通引脚分配、低速、便于布线、最低延迟 | 无1-Gbps支持, |

| MII减少(RMII) | RX_D[1:0], CRS_DV, TX_D[1:0], TX_EN (6) | 10, 100 | 引脚计数减少 | 确定性延迟低 (由于先进、先出),无1-Gbps支持 |

| 千兆位MII(GMII) | RX_D[7:0], GRX_CLK, RX_CTRL, TX_D[7:0], GTX_CLK, TX_CTRL (20) | 10, 100, 1000 | 1-Gbps支持,低延迟 | 高引脚计数,一般不支持 |

| 千兆位MII减少(RGMII) | RX_D[3:0], RX_CLK, RX_CTRL, TX_D[3:0], TX_CLK, TX_CTRL (12) | 10, 100, 1000 | 1-Gbps支持,普通引脚分配 | 脚分配 布线困难,电磁兼容性(EMC)差 |

| 串行千兆位MII(SGMII) | SO_P, SO_M, SI_P, SI_M (4) | 10, 100, 1000 | 1-Gbps支持,普通引脚分配,电磁兼容性优良,易于布线 | 集成电路更昂贵 |

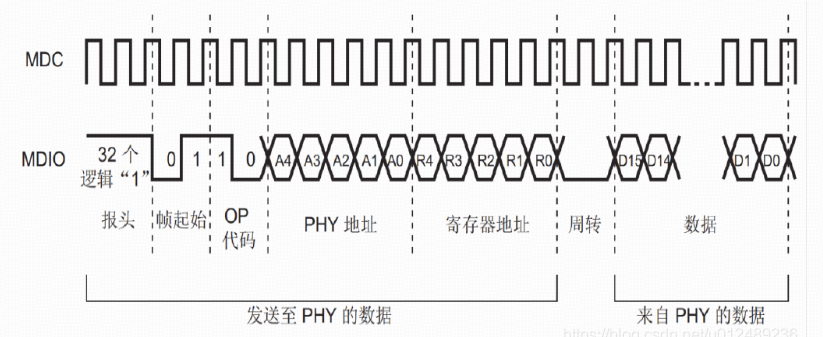

7.6 SMI(Serial Management Interface)接口

SMI是MAC内核访问PHY寄存器接口,它由两根线组成,双工,MDC为时钟,MDIO为双向数据通信,原理上跟I2C总线很类似,也可以通过总线访问多个不同的phy。

MDC/MDIO基本特性:

- 两线制:MDC(时钟线)和MDIO(数据线)。

- 时钟频率:2.5MHz

- 通信方式:总线制,可同时接入的PHY数量为32个

- 通过SMI接口,MAC芯片主动的轮询PHY层芯片,获得状态信息,并发出命令信息。

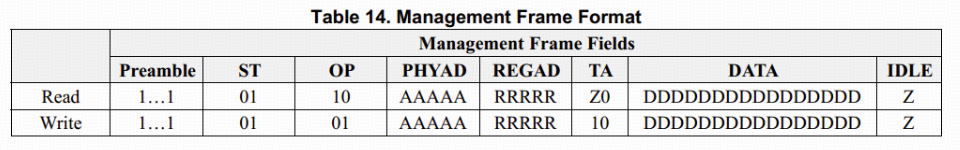

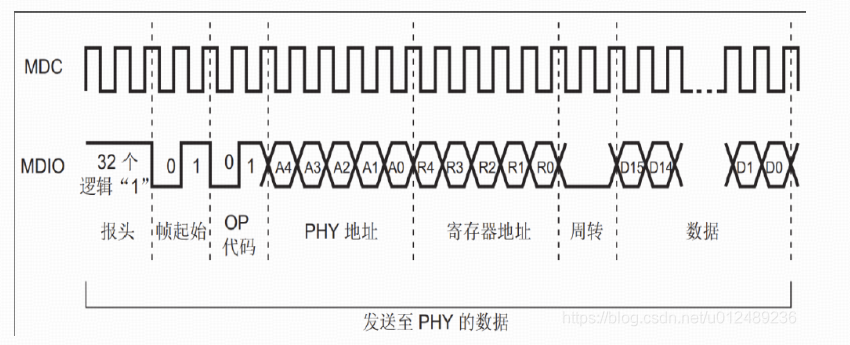

管理帧格式:

读操作时序:

写操作时序:

- 报头: 每个读写均可通过报头字段启动,报头字段对应于MDIO线上32个连续的逻辑"1"位以及MDC的32个周期,该字段用于与PHY设备建立同步

- 起始: 起始由<01>模式定义

- 操作: 定义读写类型

- PADDR: PHY地址由5位,可构成32个唯一PHY地址

- RADDR: 寄存器地址有5位

- TA:

- 数据: 数据字段为16位

- 空间: MDIO线驱动为高阻态,三态驱动器必须禁止,PHY的上拉电阻使线路保持高阻态

8、Transfomer (隔离变压器)

现在来了解PHY的输出后面部分。一颗CMOS制程的芯片工作的时候产生的信号电平总是大于0V的(这取决于芯片的制程和设计需求),但是这样的信号送到100米甚至更长的地方会有很大的直流分量的损失。而且如果外部网现直接和芯片相连的话,电磁感应(打雷)和静电,很容易造成芯片的损坏。

再就是设备接地方法不同,电网环境不同会导致双方的0V电平不一致,这样信号从A传到B,由于A设备的0V电平和B点的0V电平不一样,这样会导致很大的电流从电势高的设备流向电势低的设备。我们如何解决这个问题呢?

这时就出现了Transformer(隔离变压器)这个器件。它把PHY送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到连接网线的另外一端。这样不但使网线和PHY之间没有物理上的连接而换传递了信号,隔断了信号中的直流分量,还可以在不同0V电平的设备中传送数据。

隔离变压器本身就是设计为耐2KV~3KV电压的,也起到了防雷感应(个人认为这里用防雷击不合适)保护的作用。有些朋友的网络设备在雷雨天气时容易被烧坏,大都是PCB设计不合理造成的,而且大都烧毁了设备的接口,很少有芯片被烧毁的,就是隔离变压器起到了保护作用。

9、以太网标准对比:100BASE-TX vs 1000BASE-T vs 10GBASE-T

经常会看到上面所述的字眼, 他们是定义了在物理层(PHY)的IEEE标准,说明了数据如何在线缆上传输。

那以1000BASE-T为例;

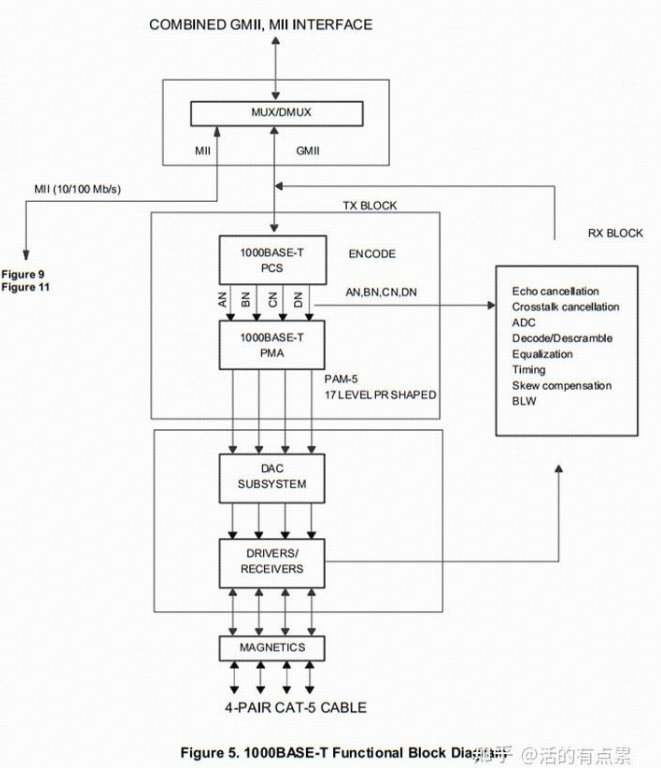

在1000BASE-T下,一个发送(TX)的数据从MII(并行,半字节 4B编码)传输到PCS层(转换为5B 编码),再经过PMA层转串行(编码机制为PAM-5),然后将数据给到高速DAC子系统通过双绞线发出。而数据接收(RX)路径原理类似。

PCS和PMA两个层的TX和RX块及其功能,配合如下框图可以更清晰的理解如上内容:

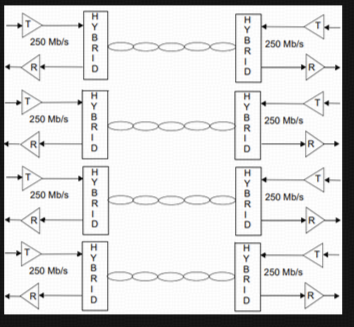

1000BASE-T PHY 是高速 CSMA/CD 网络规范的千兆以太网系列之一。 1000BASE-T 物理编码子层 (PCS)、物理介质附件 (PMA) 和基带介质规范适用于希望通过 5 类平衡双绞线布线系统实现 1000 Mb/s 性能的用户。

1000 Mb/s 的速率是通过每对线以 250 Mb/s的数据速率传输来实现的,如图所示:网线

对应上面的网速要求或者要达到phy 设计的高速率,那么双绞线也有相应 的标准和类型:

目前基于双绞线的以太网主流技术是基于 802.3ab 标准的千兆以太网,其可在超过 100m的5类双绞线上传输 1000Mbit/s 的数据流,大多数企业在组建网络时将千兆以太网作为首选高速网络技术。万兆网络端口需要配套 Cat6/6a 或以上线缆。

CAT-5 /CAT-6是双绞线的类型代表。cat5 有上面所需的4对双绞线。

10、关于传输介质

隔离变压器本身是个被动元件,只是把PHY的信号耦合了到网线上,并没有起到功率放大的作用。那么一张网卡信号的传输的最长距离是谁决定的呢?

一张网卡的传输最大距离和与对端设备连接的兼容性主要是PHY决定的。但是可以将信号送的超过100米的PHY其输出的功率也比较大,更容易产生EMI的问题。这时候就需要合适的Transformer与之配合。作为PHY的老大公司Marvell的PHY,常常可以传送180~200米的距离,远远超过IEEE的100米的标准。

RJ-45的接头实现了网卡和网线的连接。它里面有8个铜片可以和网线中的4对双绞(8根)线对应连接。其中100M的网络中1、2是传送数据的,3、6是接收数据的。1、2之间是一对差分信号,也就是说它们的波形一样,但是相位相差180度,同一时刻的电压幅度互为正负。这样的信号可以传递的更远,抗干扰能力强。同样的,3、6也一样是差分信号。

网线中的8根线,每两根扭在一起成为一对。我们制作网线的时候,一定要注意要让1、2在其中的一对,3、6在一对。否则长距离情况下使用这根网线的时候会导致无法连接或连接很不稳定。

现在新的PHY支持AUTO MDI-X功能(也需要Transformer支持)。它可以实现RJ-45接口的1、2上的传送信号线和3、6上的接收信号线的功能自动互相交换。有的PHY甚至支持一对线中的正信号和负信号的功能自动交换。这样我们就不必为了到底连接某个设备需要使用直通网线还是交叉网线而费心了。这项技术已经被广泛的应用在交换机和SOHO路由器上。

在1000Basd-T网络中,其中最普遍的一种传输方式是使用网线中所有的4对双绞线,其中增加了4、5和7、8来共同传送接收数据。由于1000Based-T网络的规范包含了AUTO MDI-X功能,因此不能严格确定它们的传出或接收的关系,要看双方的具体的协商结果。

11、网卡上的EEPROM

有一颗EEPROM芯片,通常是一颗93C46。里面记录了网卡芯片的供应商ID、子系统供应商ID、网卡的MAC地址、网卡的一些配置,如SMI总线上PHY的地址,BOOTROM的容量,是否启用BOOTROM引导系统等东西。

很多网卡上还有BOOTROM这个东西。它是用于无盘工作站引导操作系统的。既然无盘,一些引导用必需用到的程序和协议栈就放到里面了,例如RPL、PXE等。实际上它就是一个标准的PCI ROM。所以才会有一些硬盘写保护卡可以通过烧写网卡的BootRom来实现。其实PCI设备的ROM是可以放到主板BIOS里面的。启动电脑的时候一样可以检测到这个ROM并且正确识别它是什么设备的。AGP在配置上和PCI很多地方一样,所以很多显卡的BIOS也可以放到主板BIOS里面。这就是为什么板载的网卡我们从来没有看到过BOOTROM的原因。

12、网卡的供电

最后就是电源部分了。大多数网卡现在都使用3.3V或更低的电压。有的是双电压的。因此需要电源转换电路。

而且网卡为了实现Wake on line功能,必须保证全部的PHY和MAC的极少一部分始终处于有电的状态,这需要把主板上的5V Standby电压转换为PHY工作电压的电路。在主机开机后,PHY的工作电压应该被从5V转出来的电压替代以节省5V Standby的消耗。(许多劣质网卡没有这么做)。

有Wake on line功能的网卡一般还有一个WOL的接口。那是因为PCI2.1以前没有PCI设备唤醒主机的功能,所以需要着一根线通过主板上的WOL的接口连到南桥里面以实现WOL的功能。

新的主板合网卡一般支持PCI2.2/2.3,扩展了PME#信号功能,不需要那个接口而通过PCI总线就可以实现唤醒功能。