图1、Read The Official Manual 阅读官方手册:

----Yosys is A Free Verilog Synthesis Suite 2013 by C.Wolf and J. Glaster.

----Yosys是一个免费的Verilog综合工具。

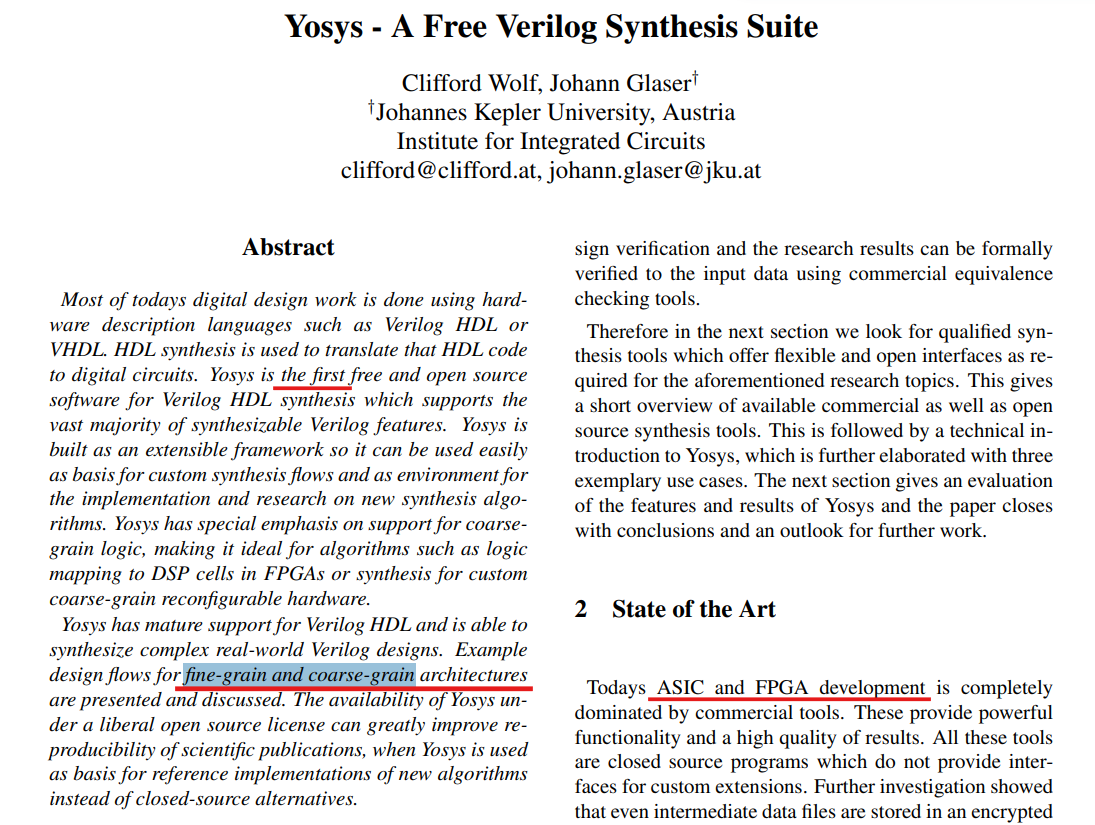

图2、Yosys的2013年论文:

----Todays ASIC and FPGA development is competely dominated by commercial tools. 完全由商业工具主导!主导玩家自然就是那三家巨头。

----Yosys has mature support for Verilog HDL and is able to synthesize complex real-world Verilog designs. //Yosys具有成熟的技术支持Verilog HDL,能对实际的Verilog的复杂项目进行综合。这一描述还是很有自信也很给开源社区信心的。

----Example design flows for fine-grain and coarse-grain architectures are presented and discussed. //这里说的细颗粒度架构(fine-grain architectures)和粗颗粒度架构(coarse-grain architectures)分别和ASIC和FPGA对应。因为将Verilog综合为ASIC需要更加细粒度(最终到每一个晶体管以及晶体管级的连接),而综合为FPGA则通常粗颗粒度一些(最终到每一个CLB/LUT并且也不必做实际的物理连线而只需要通过BitStream体现为Configuration Bits)。

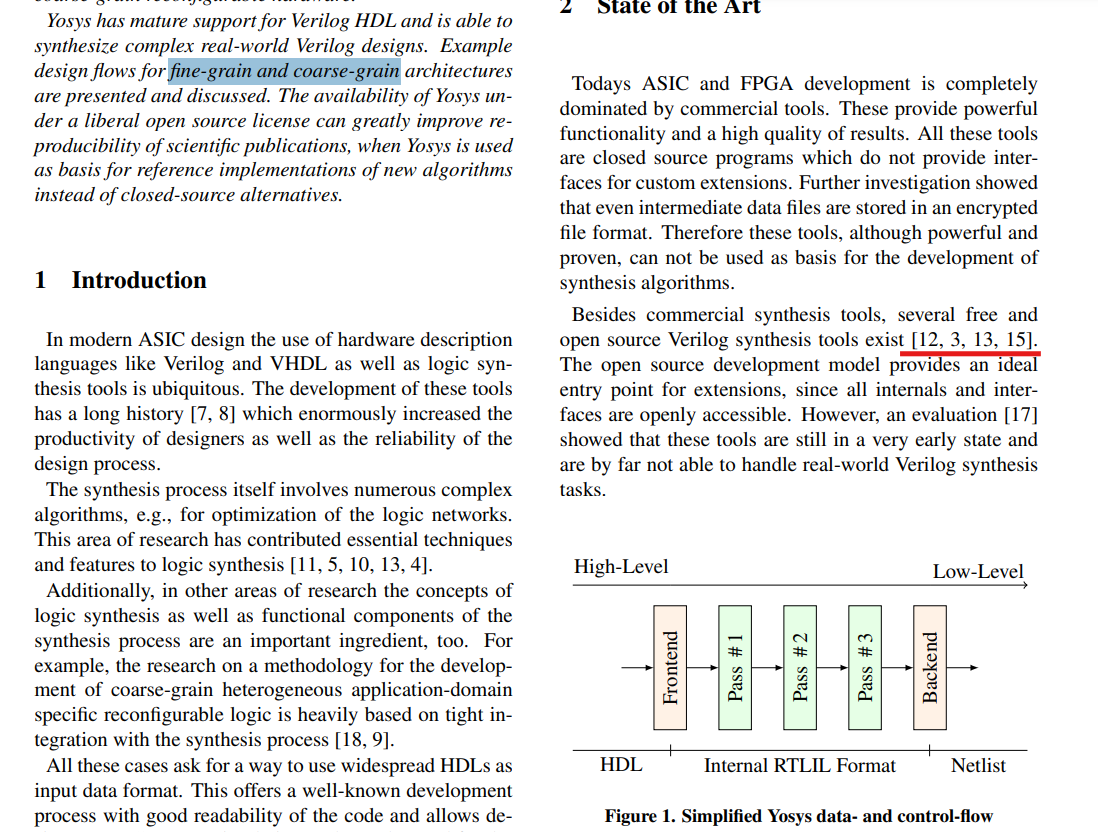

图3、开源IC综合工具的艺术(State of the Art)

----还有一些开源的综合工具介绍。这里就不展开了,因为这些工具都没有Yosys好使----all these tools are still in a very early state and are by far not able to handle real-world Verilog synthesys tasks. 只有Yosys相对成熟。

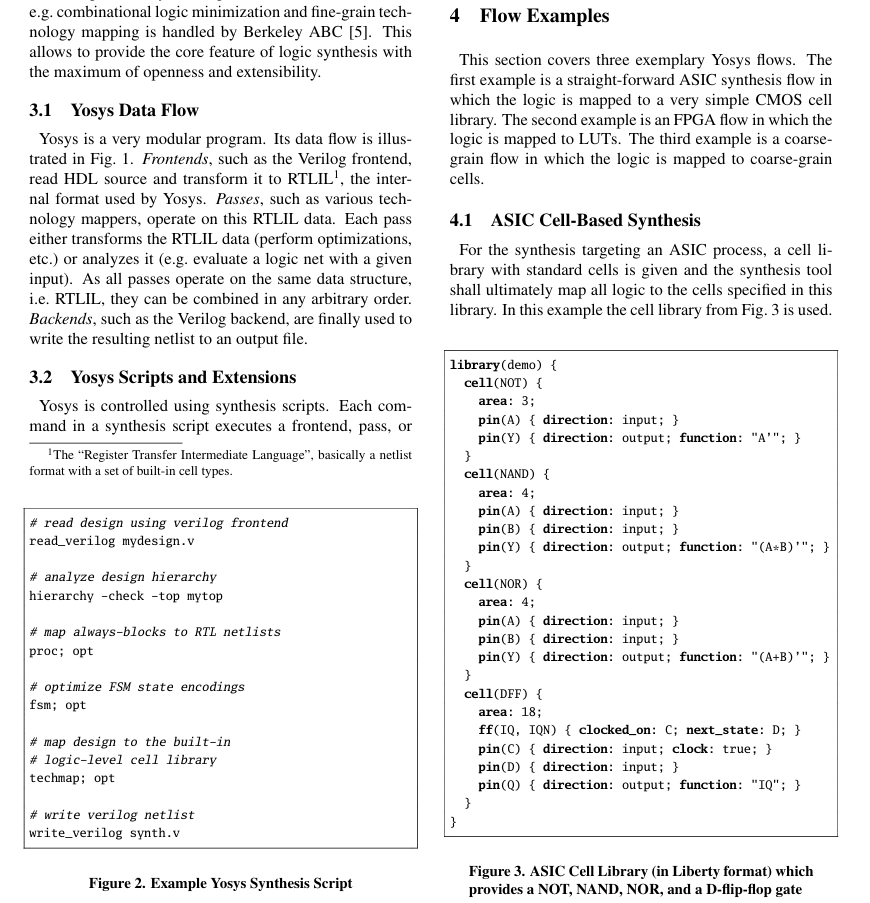

图4、Yosys Data flow通过Yosys Scripts实现。

----第三章The Yosys Data Flow通过图2展示得比较清楚!一切都放在命令行脚本中顺次完成,形成所谓的Flow!

----第4.1节ASIC Cell-based Synthesis就是细粒度的综合!The synthesis shall ultimately map all logic to the cells specified in the library (with standard cells given)!

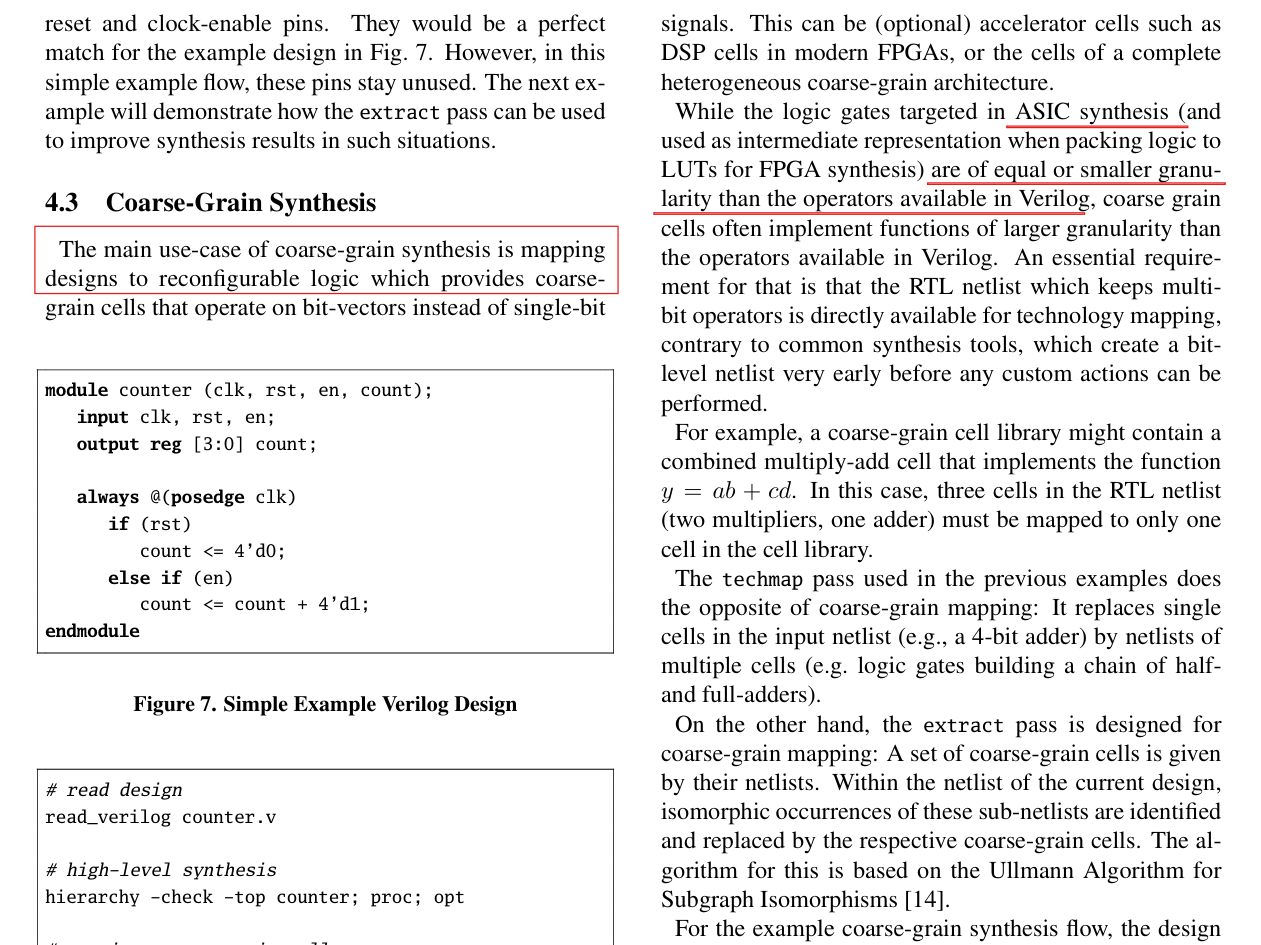

图5、ASIC综合脚本和FPGA综合脚本

----图4和图5分别列出了ASIC综合脚本和FPGA综合脚本!

----ASIC综合中,使用ABC这个工具将Verilog代码映射到asic_cells.lib,是为细粒度综合。

----FPGA综合中,使用ABC这个工具将Verilog代码映射到LUTs和fpga_cells.v,是为粗粒度综合。

----这里牵涉到另一个关键工具是Berkeley ABC。Yosys和ABC两个工具的项目大概是开源综合工具中的SOTA(State-of-the-art最高水平),他们相互配合而不是相互替代。

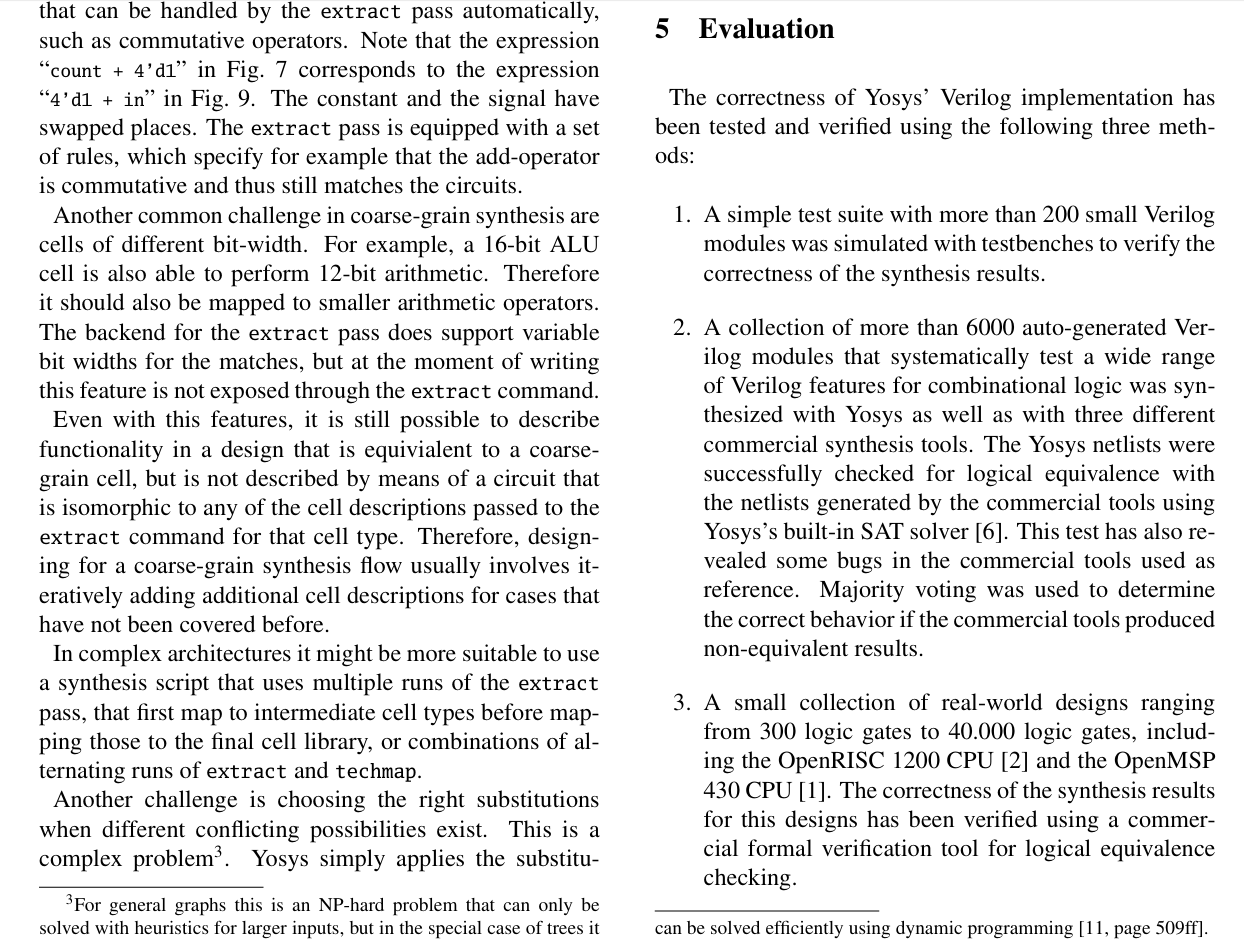

图6、粗颗粒综合和细颗粒综合

----The main use-case of coarse-grain synthesis is mapping designs to reconfigurable logic. //粗颗粒综合的的主要用例,就是把设计映射到可重配置逻辑(也就是FPGA)上~!

----While the logic gates targeted in ASIC synthesis are of equal or smaller granularity than the operators available in Verilog, coarse grain cells often implement functions of larger granularity than the operators available in Verilog. //ASIC综合就是更小的颗粒度,而粗颗粒度综合则是更大的颗粒度。

图7、比对的方法是IC设计的常用方法也是开源EDA软件的评估方法。

----Yosys逻辑综合也面临着许多的挑战,其中的一个挑战是NP-hard problem。

----Yosy逻辑综合实现到底正确不正确、靠谱不靠谱,在第5章中介绍了一些使用Yosys的实验,其中第2个实验是手机了6000个auto-generated Verilog modules,然后synthesized with Yos as well as with three different commercial synthesis tools,然后进行比对!

----The Yosys netlists were successfully checked for logic equivalence with the netlists generated by the commercial tools using Yosys's built-in solver. 这个是横向的Apple-to-Apple的比对。

----This test has also revealed some bugs in the commercial tools used as reference. 这个没有(也不适合)披露商业软件的具体什么bug,但这个说法写在正式的论文里,对将Yosys作为候选工具的芯片开发者来说是比较有说服力的。

----在芯片开发中通过比对进行芯片测试验证的方法是很很很常见的。比如RISC-V的测试使用的riscv-spike就是作为RISC-V逻辑测试的一个reference进行比对的,也属于同一个层次下的功能结果比对(待测的功能结果vs参考标准所提供的功能结果)。还有一种比对不是Apple-to-Apple的比对,而是将不同阶段的代码进行逻辑等价性比对,以保证综合前和综合后的逻辑等价,或者说综合的过程没有导致逻辑被破坏。

图8、Yosys的官方教程。

----Yosys的官方使用手册!Getting started with Yosys则正是入门上手所需要的。

图9、Yosys的交互式命令行。

----在Linux命令行输入Yosys fifo.v。请注意这时候不要期待像日常简单的命令行一样输出结果然后结束程序的运行!它的实际运行是,读取fifo.v文件,并进入到Yosys自己的交互式命令行环境中!然后可以进一步使用Elaboration中所示的Yosys的交互式命令行(read_verilog, hierarchy, proc等)。

----也可以在命令行中直接敲Yosys,进入Yosys的交互式命令行环境之后再执行read_verilog fifo.v以及Elaboration的中所示的后续命令行。

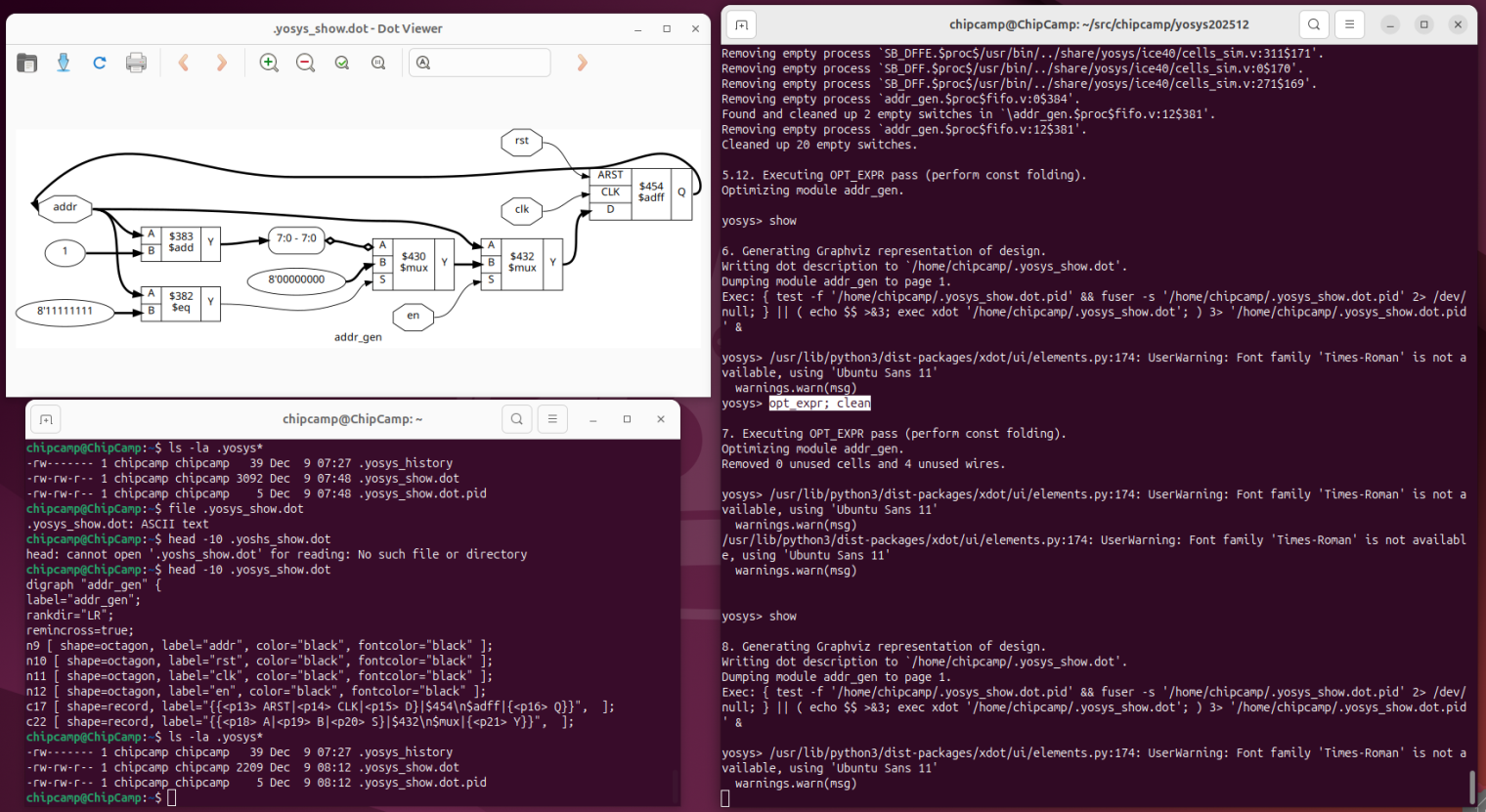

图10、Yosys的实操体验和总结。

----如图所示是20251209对Yosys的实操体验,把fifo.v的addr_gen模块,综合为电路图(网表)!这个电路图网表是一个.dot格式的文件,这个.dot格式的文件再通过Linux下的dot软件(dot命令行)打开!

----这个dot文件是一个文本文件,里面描述了各个节点名称属性以及节点之间的连接关系。而dot软件则可以把这个文本文件显示为图形。这个图形就是fifo.v模块(通常是behavior-level)所定义的芯片/电路的gate-level netlist。

----可以和PCB进行对比!这个netlist相当于原理图(Schematic),要把这些逻辑上节点和连线,变成物理上的节点和连线也就是PCB,则需要进行Place & Route的操作,包括每个节点多大的尺寸具体放在PCB的哪个位置(Place),连线具怎么走(Route)。

----对IC设计来说,这就需要后续的Place&Route软件了,而后续【挂接】P&R软件等工作,则属于IC设计的Design Flow了。Yosys作为Design Flow上的关键一个环节,Place-and-Route则是Design Flow上的后续关键环节。

----把Yosys和Place-and-Route等等各个环节的工具集合并形成Design Flow的工具,则是OpenROAD和OpenFPGA等更上层的工具了(分别面向ASIC开发和FPGA开发)。这些工具的底层,则是Yosys和Berkeley ABC这样的底层工具。

----至此可以看出Yosys在开源EDA工具链中的核心作用,就是把行为级/寄存器传输级的Verilog HDL程序,综合为代表电路结构的网表!对ASIC来说,这个网表是细粒度的Standard-cell。对FPGA来说,这个网表是粗粒度的CLB/LUT。对于设计人员来说,这个网表是一个可以进行图形化展示的dot文件。

<<<<<<<<完>>>>>>>>

摘要:Yosys是一款开源的Verilog综合工具,支持ASIC和FPGA设计流程。它通过脚本实现细粒度(ASIC)和粗粒度(FPGA)综合,与Berkeley ABC工具配合使用。Yosys能够处理复杂的Verilog设计,并通过与商业工具的对比验证其可靠性。其工作流程包括将行为级Verilog转换为门级网表(.dot格式),后续可结合Place & Route工具完成完整IC设计流程。Yosys在开源EDA工具链中扮演核心角色,为OpenROAD和OpenFPGA等上层工具提供基础支持。