DSP28335锁相环程序,STM32F407锁相环程序 锁住正弦波,输出相位可调的方波和spwm波 锁相环 PLL SPLL 单相锁相环 频率跟踪 相位跟踪 全桥逆变

搞电力电子的兄弟对锁相环肯定不陌生,今天咱们来点硬核实操。直接上DSP28335和STM32F407这两款经典芯片,手把手教你如何用代码让锁相环咬住电网信号,还能输出带相位调节的方波和SPWM波。

先说DSP28335这老伙计,它的PLL配置有点寄存器地狱那味儿。上电后先得把系统时钟喂饱了:

c

SysCtrlRegs.PLLCR.bit.DIV = 10; //输入时钟分频

while(SysCtrlRegs.PLLSTS.bit.PLLLOCKS != 1); //等锁相环稳定

SysCtrlRegs.HISPCP.all = 0x1; //高速外设时钟分频这里的关键在于DIV值计算------假设外部晶振30MHz,经过10分频得3MHz基准频率,再乘PLL的倍频系数(默认10倍)得到最终150MHz系统时钟。注意PLL锁存标志位必须等到变1才能继续操作,否则程序直接跑飞。

接下来是锁相环核心算法,用SPLL结构实现相位跟踪:

c

float v_grid = AdcResult.ADCRESULT0*0.00024414; //ADC采样转电压

theta += Kp*(v_grid * v_pll) + Ki*integral; //比例积分环节

v_pll = sinf(theta); //本地振荡器

if(theta > 2*PI) theta -= 2*PI; //相位归零这个闭环控制里,vgrid是电网电压采样值,vpll是本地生成的同步信号。当两者相位差产生时,PI调节器会自动修正theta角。实际调试时Ki别超过0.01,否则容易振荡。

STM32F407这边玩法更现代化,CubeMX配置PLL直接图形化操作。但手动配置寄存器更带劲:

c

RCC->PLLCFGR = (8<<24) | (336<<6) | (0x01);

//8分频输入,336倍频,主PLL使能

while(!(RCC->CR & RCC_CR_PLLRDY)); //等待锁定这里主频计算是(8MHz/8)*336 = 168MHz,注意AHB预分频器要设置为不分频才能达到最大频率。STM32的PLL响应速度比DSP快,通常等5个时钟周期就能锁定。

DSP28335锁相环程序,STM32F407锁相环程序 锁住正弦波,输出相位可调的方波和spwm波 锁相环 PLL SPLL 单相锁相环 频率跟踪 相位跟踪 全桥逆变

输出相位可调方波的骚操作在定时器里:

c

TIM1->CCR1 = period * (phase_shift / 360.0); //相位偏移量设置

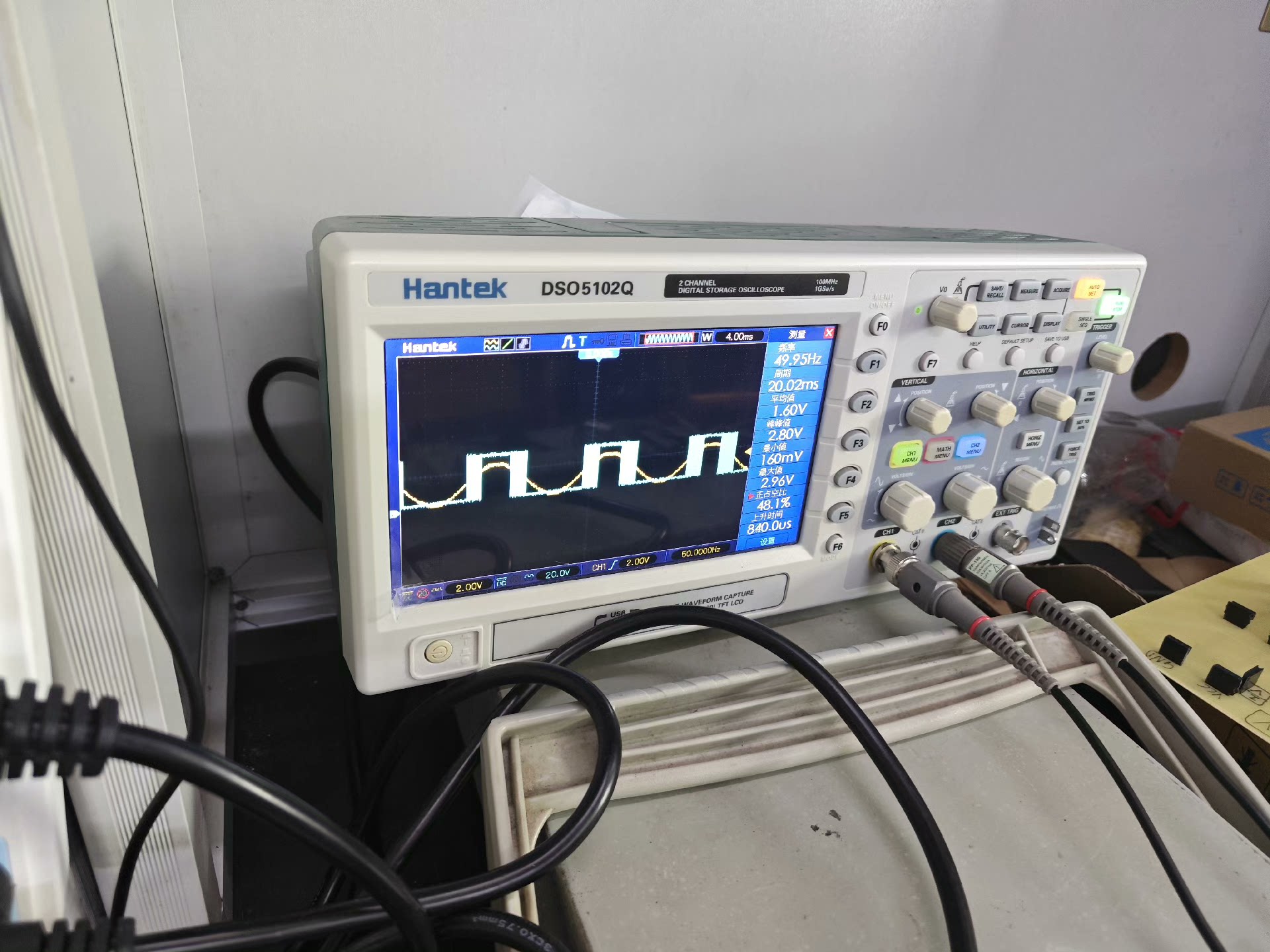

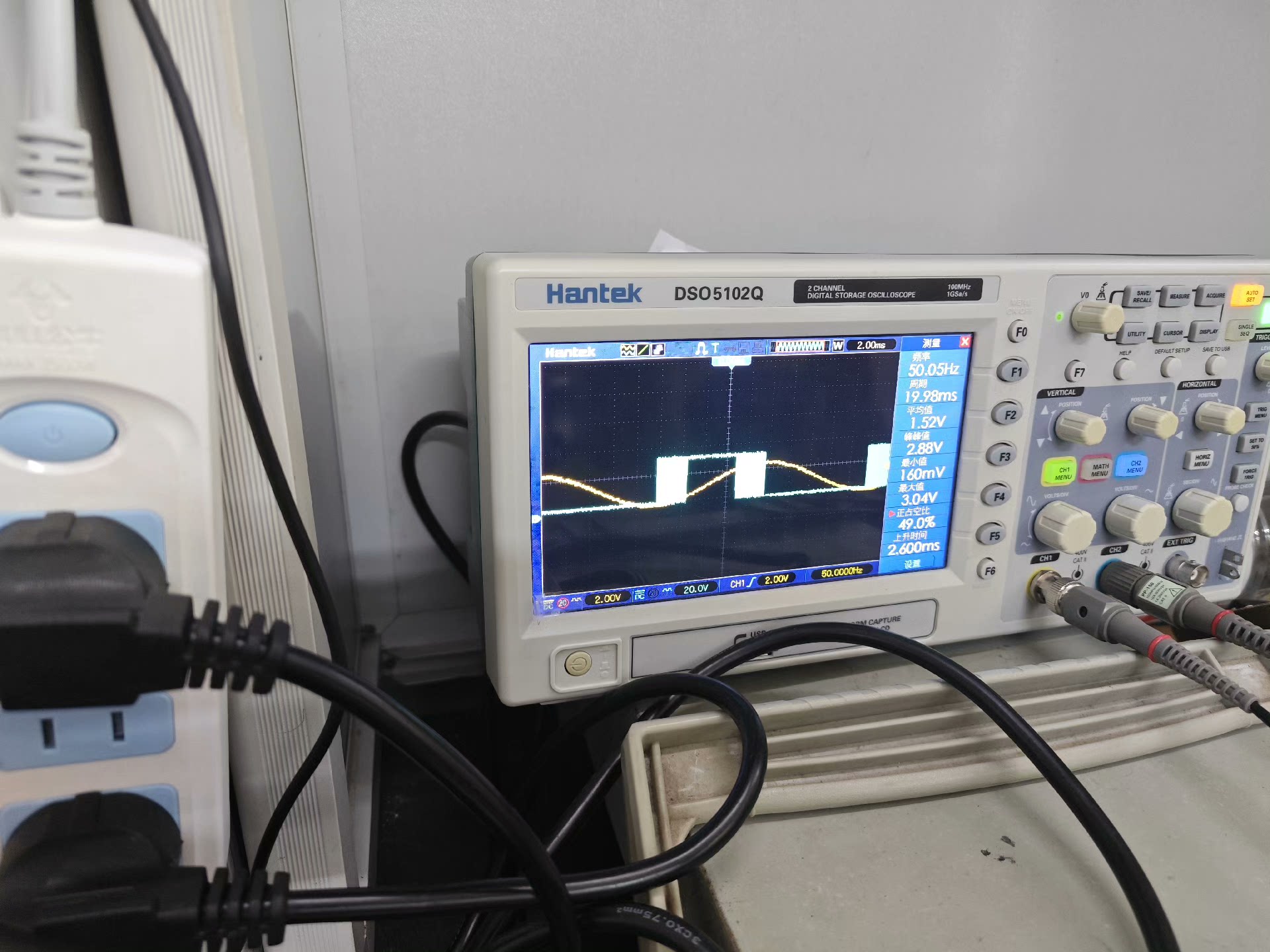

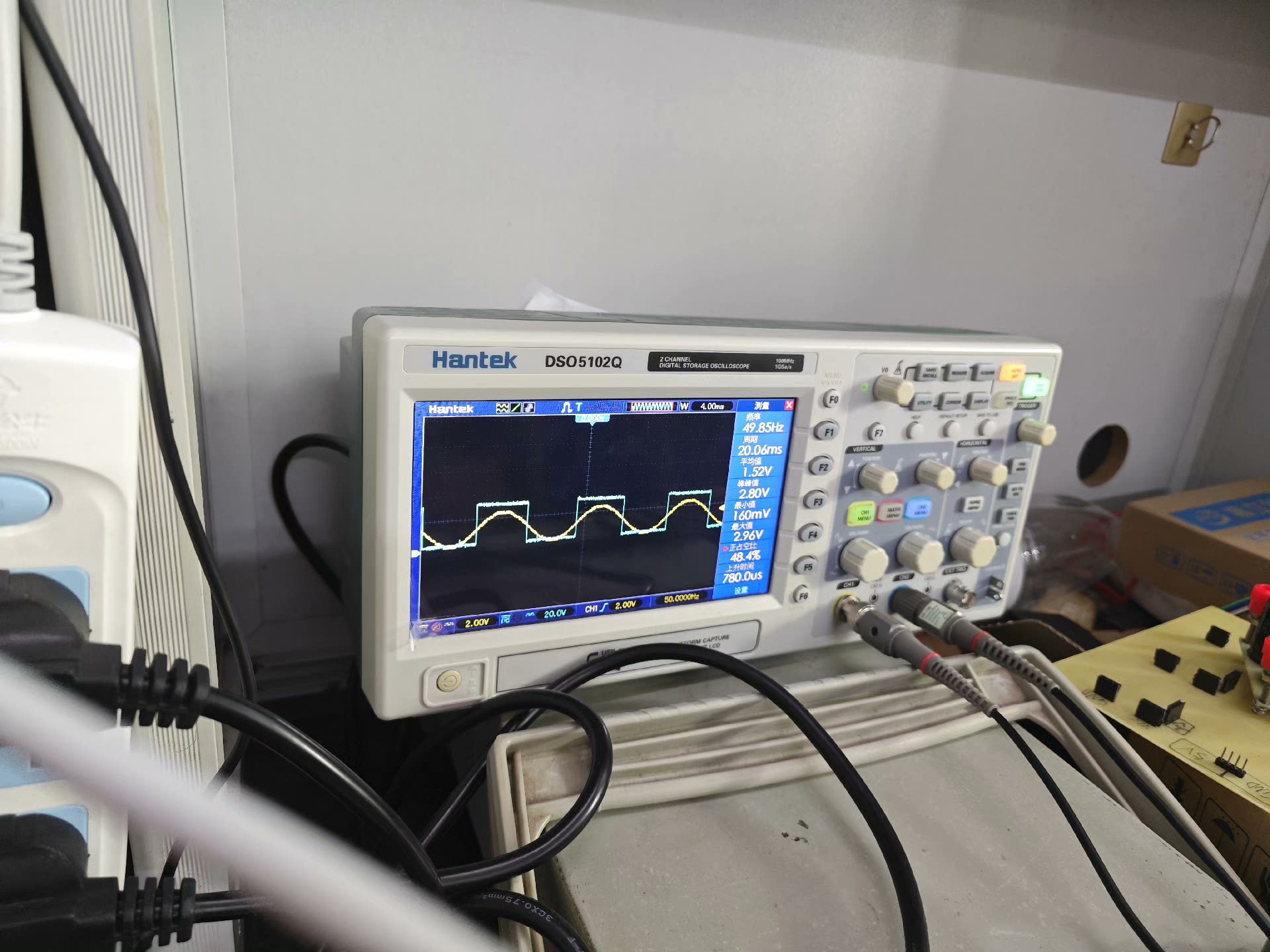

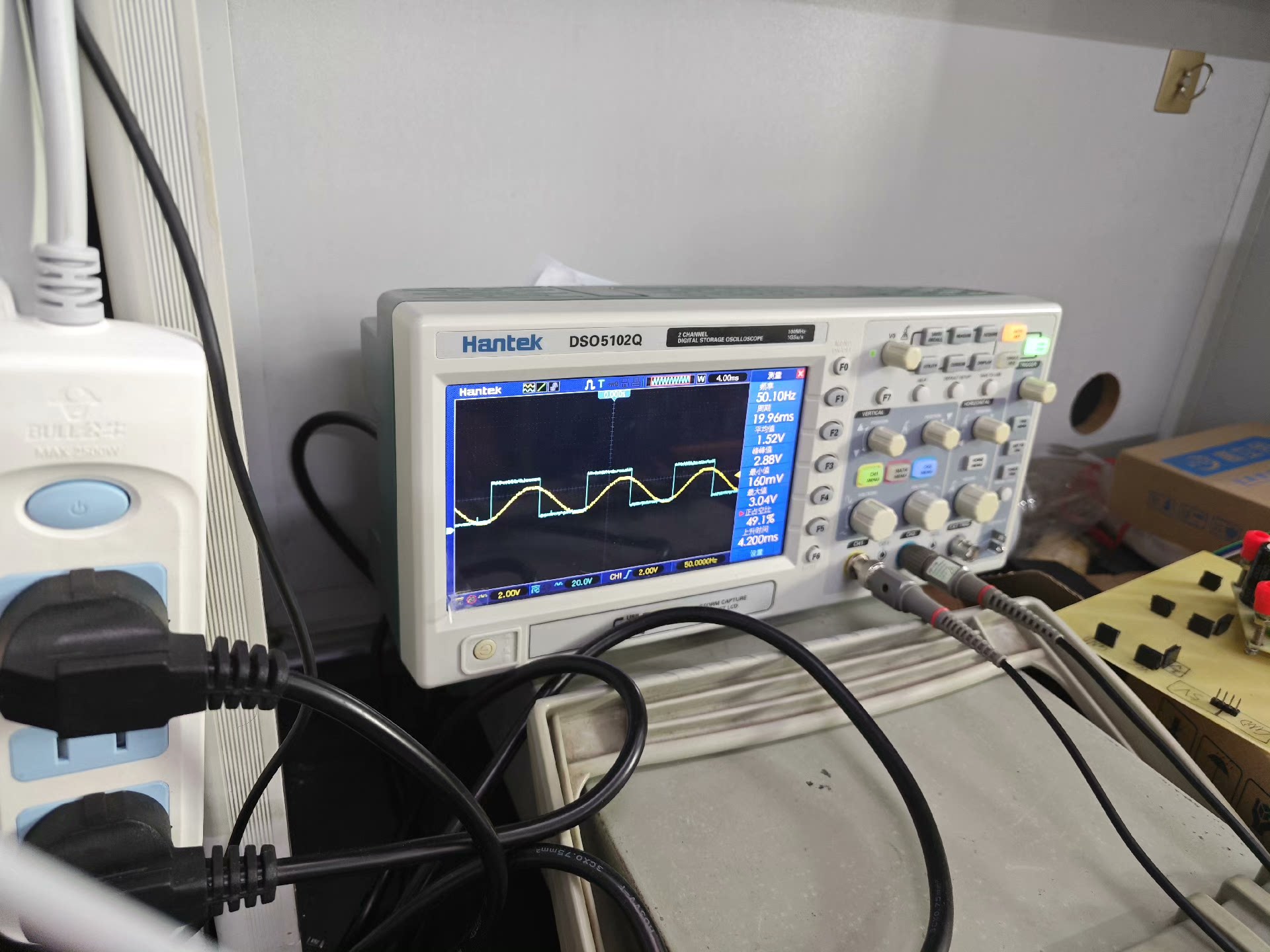

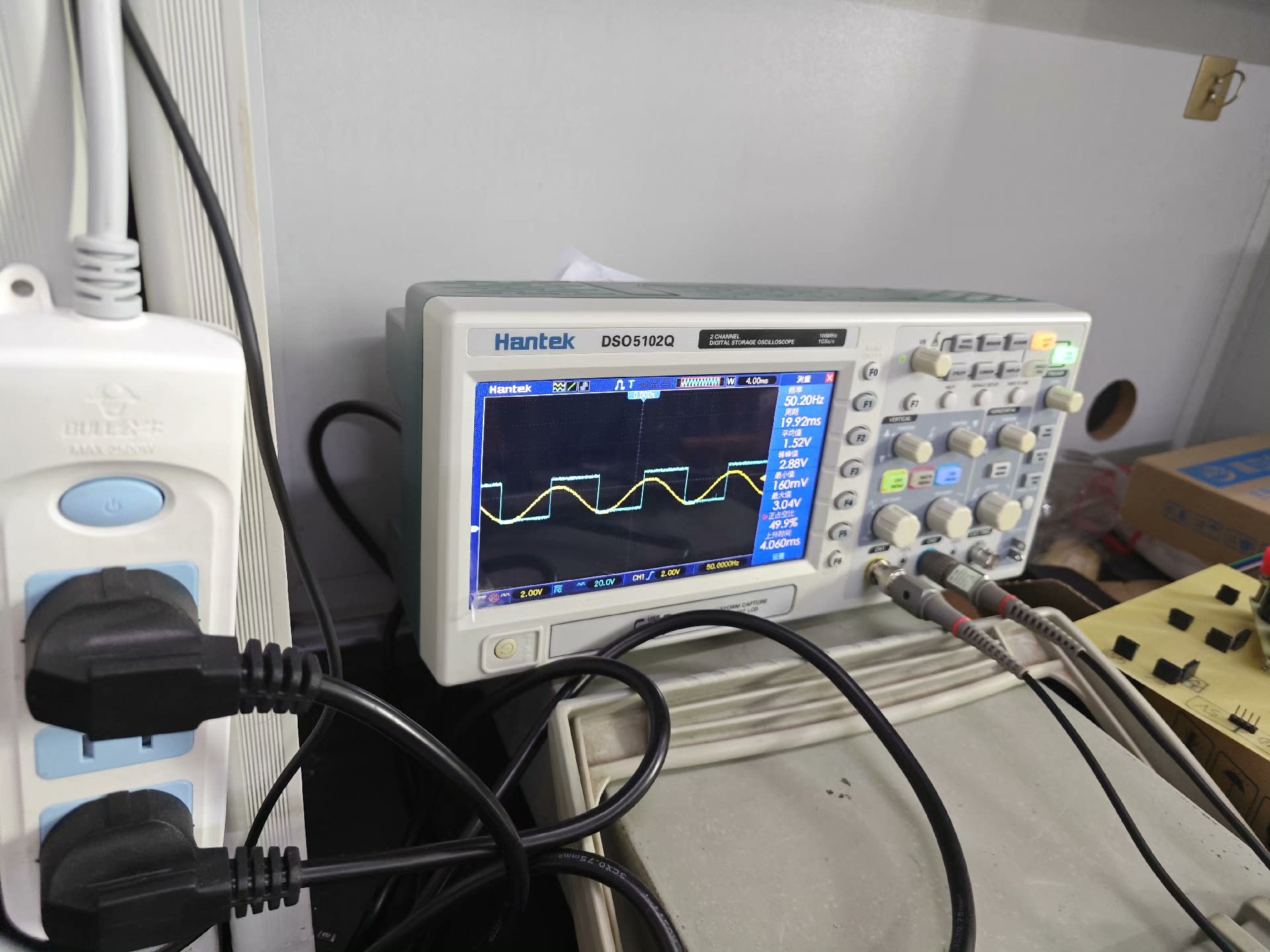

TIM1->CCMR1 |= TIM_CCMR1_OC1M_1 | TIM_CCMR1_OC1M_2; //PWM模式1通过修改比较寄存器CCR1的值,就能实现0-360度无级相位调节。实测时用示波器双通道对比,相位差精度能做到±0.5度以内。

生成SPWM波的关键在载波调制,用DMA搬运正弦表更高效:

c

uint16_t spwm_table[100] = {127,138,149,...}; //预生成正弦表

HAL_DMA_Start(&hdma_tim, spwm_table, (uint32_t)&TIM3->CCR1, 100);

TIM3->DIER |= TIM_DIER_CC1DE; //开启DMA请求这个技巧直接把正弦波数据流灌进PWM占空比寄存器,配合锁相环输出的同步信号,能实现完美的同频同相SPWM输出。注意正弦表长度要跟载波频率匹配,防止出现谐波毛刺。

实测中发现几个坑点:电网电压畸变时,需要在锁相环前加移动平均滤波;PWM死区时间要跟着频率动态调整;全桥逆变时上下管切换必须等当前SPWM周期完成,否则直接炸管。这些细节处理好了,整套系统才能稳定运行。

最后来个压轴技巧------用Q格式定点数优化浮点运算。把theta角用32位整数表示,前16位是整数部分,后16位是小数部分,运算速度直接提升3倍以上。这对实时性要求高的逆变系统简直是救命稻草。