fpga 以太网w5500 SPI传输80MHz FPGA verilog TCP客户端驱动源码,8个SOCKET都可用,SPI频率80MHZ,硬件验证以通过 。 w5500 ip 核 w5500 软核,还有TCP服务端和UDP模式,联系联系我要那个,默认发TCP客户端。 这个代码是用fpga驱动和使用w5500模块,做过优化,可能以达到w5500最高传输速度,学习必用之良品

概述

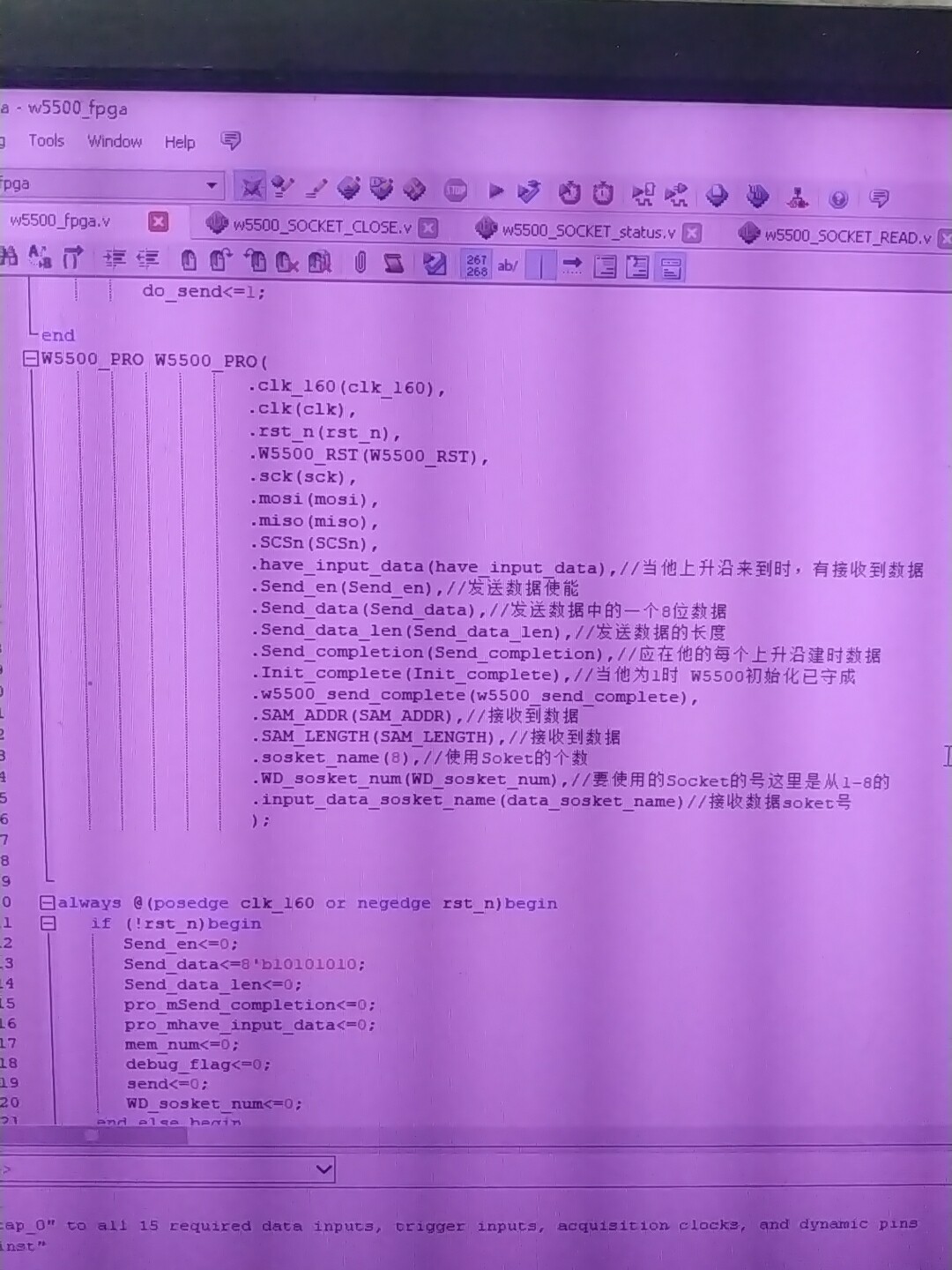

本文档详细描述了一套基于 FPGA 实现的 W5500 以太网控制器驱动系统 。该系统支持 SPI 接口频率高达 80MHz ,可同时管理 最多 8 个独立 SOCKET ,并已通过硬件验证。整体架构采用模块化设计,涵盖 SPI 通信控制、W5500 初始化、中断处理、数据收发控制 等核心功能,适用于 TCP 客户端、TCP 服务器及 UDP 三种网络通信模式。

fpga 以太网w5500 SPI传输80MHz FPGA verilog TCP客户端驱动源码,8个SOCKET都可用,SPI频率80MHZ,硬件验证以通过 。 w5500 ip 核 w5500 软核,还有TCP服务端和UDP模式,联系联系我要那个,默认发TCP客户端。 这个代码是用fpga驱动和使用w5500模块,做过优化,可能以达到w5500最高传输速度,学习必用之良品

系统以 160MHz 主时钟 为基础,通过内部状态机精确控制 SPI 时序,确保在高速下稳定运行。驱动逻辑完全由硬件状态机实现,不依赖外部处理器干预,适用于高性能嵌入式或 FPGA 网络应用。

系统架构

整个驱动系统由以下关键模块构成:

- SPI 通信子系统:负责与 W5500 芯片的底层 SPI 交互,包括时钟生成、片选控制、数据串行化/反串行化。

- W5500 初始化模块:完成芯片的通用寄存器配置(如 IP、网关、MAC)及各 SOCKET 的独立初始化。

- 中断处理模块:轮询并解析 W5500 的中断状态寄存器,识别各 SOCKET 的连接、接收、发送完成等事件。

- 读写控制模块:根据中断事件或上层指令,执行数据接收(从 W5500 缓存读取)或数据发送(写入 W5500 缓存并触发发送)。

- 顶层协调器:统筹各模块工作流程,实现"初始化 → 中断轮询 → 数据处理"的闭环控制。

核心功能详解

1. 高速 SPI 通信控制

SPI 子系统是整个驱动的基石。其设计重点在于:

- 精确的时序控制:通过计数器生成符合 W5500 要求的 SPI 时钟(SCK)和片选(SCSn)信号。在 160MHz 系统时钟下,SCK 频率可达 80MHz。

- 灵活的数据帧处理:支持多种 SPI 操作模式,包括:

- 固定长度读写(1~6 字节)

- 可变长度读写(由

rxsize**或customdata_len动态指定) - 双沿数据采样/驱动:在 SCK 的下降沿驱动 MOSI(主出),在上升沿采样 MISO(主入),符合 W5500 的 SPI 模式 0(CPOL=0, CPHA=0)要求。

- 状态机驱动 :通过

IDLE → COUNT → ...状态机管理整个 SPI 事务的生命周期,确保命令、地址、数据的有序传输。

2. W5500 芯片初始化

初始化过程分为两个阶段,确保芯片处于可工作状态:

2.1 通用寄存器初始化

- 硬件复位 :拉低

W5500_RST引脚至少 50ms,随后释放。 - 网络连接检测:读取 PHY 状态寄存器,确认物理链路已连通。

- 软件复位与配置:通过 SPI 写入通用寄存器,设置:

- 本机 IP 地址 (

SIPR) - 子网掩码 (

SUBR) - 网关地址 (

GAR) - MAC 地址 (

SHAR) - 重发时间 (

RTR) 与重发次数 (RCR)

2.2 SOCKET 寄存器初始化

对每个启用的 SOCKET(最多 8 个)进行独立配置:

- 缓冲区分配:为每个 SOCKET 分配 2KB 的发送和接收缓冲区。

- 端口与目标地址设置 :配置本机端口 (

SnPORT*)、目标 IP (Sn*DIPR) 和目标端口 (Sn_DPORTR)。 - 工作模式设定 :根据用户选择(UDP / TCP Client / TCP Server),向模式寄存器 (

Sn_MR) 写入相应值,并执行OPEN命令激活 SOCKET。

3. 中断驱动的数据收发

系统采用 轮询中断标志 的方式工作,避免了对硬件中断引脚的依赖,提高了系统的通用性。

3.1 中断处理流程

- 读取全局中断寄存器 (

SIR):确定哪个 SOCKET 产生了中断。 - 读取对应 SOCKET 的中断源寄存器 (

Sn_IR):判断中断类型(连接成功、断开、接收数据、发送完成、超时等)。 - 清除中断标志 :向

Sn_IR写回中断状态值,以清除中断。 - 状态更新 :将中断事件转换为内部状态(如

SCONN*,S*RECEIVE,S_TRANSMITOK),供读写控制模块使用。

3.2 数据接收

当检测到 IR_RECV 中断时:

- 读取接收数据大小 (

SnRXRSR):获取待读取的字节数。 - 读取接收读指针 (

SnRXRD):确定数据在接收缓冲区中的起始地址。 - 从缓冲区读取数据:根据地址和长度,通过 SPI 读取实际数据。

- 更新读指针并通知芯片 :将新的读指针写回

SnRXRD,并发送RECV命令,通知 W5500 释放已读数据。

3.3 数据发送

当上层有数据需要发送时:

- 读取发送写指针 (

SnTXWR):确定数据在发送缓冲区中的写入地址。 - 写入数据到缓冲区:将待发送数据通过 SPI 写入发送缓冲区。

- 更新写指针 :将新的写指针写回

SnTXWR。 - 触发发送 :向命令寄存器 (

Sn_CR) 写入SEND命令,启动硬件发送过程。 - 等待发送完成中断 :系统会轮询到

IRSENDOK中断,标志着本次发送成功。

4. 多 SOCKET 管理与模式支持

- UDP 模式:配置简单,无连接状态。发送数据只需指定目标地址和端口,接收数据时通过 SOCKET 号区分来源。

- TCP 客户端模式 :主动向服务器发起

CONNECT请求,建立连接后进行数据收发。 - TCP 服务器模式 :配置为

LISTEN状态,被动等待客户端连接。连接建立后,同样进行数据收发。 - 灵活的发送策略:支持两种发送模式:

- 指定 SOCKET 发送:由用户明确指定使用哪个 SOCKET 发送数据。

- 自动负载均衡发送:系统自动选择可用的 SOCKET 进行发送,以提高吞吐量。

总结

本 W5500 FPGA 驱动系统是一套完整、高效、稳定的硬件 IP。它通过精细的状态机设计和高速 SPI 控制,充分发挥了 W5500 芯片的多 SOCKET 并发能力,为 FPGA 平台提供了强大的网络通信基础。其模块化的设计也便于集成到更复杂的系统中,满足工业控制、数据采集、视频传输等多种应用场景的需求。