目录

[1. 架构 (Architecture)](#1. 架构 (Architecture))

[(1). 模拟前端与 Easy Drive (信号的入口与调理)](#(1). 模拟前端与 Easy Drive (信号的入口与调理))

[(2). SAR 转换核心 (模拟转数字的核心)](#(2). SAR 转换核心 (模拟转数字的核心))

[(3). 数字信号处理模块 (数据的精加工)](#(3). 数字信号处理模块 (数据的精加工))

[(4). 数据封装与状态监测 (信息的完善)](#(4). 数据封装与状态监测 (信息的完善))

[(5). Flexi-SPI 接口 (数据的最终传输)](#(5). Flexi-SPI 接口 (数据的最终传输))

[2. 特点 (Features)](#2. 特点 (Features))

[3. 引脚功能 (Pin Configuration)](#3. 引脚功能 (Pin Configuration))

[4.1 接口拓扑模式 (Data Lane Modes)](#4.1 接口拓扑模式 (Data Lane Modes))

[4.2 时钟架构模式 (Clocking Modes)](#4.2 时钟架构模式 (Clocking Modes))

[4.2.1. 标准 SPI 模式 (Standard SPI)](#4.2.1. 标准 SPI 模式 (Standard SPI))

[4.2.2. 回声时钟模式 (Echo Clock Mode) ------ 建议 FPGA 选用](#4.2.2. 回声时钟模式 (Echo Clock Mode) —— 建议 FPGA 选用)

[4.2.3. 主机时钟模式 (Host Clock Mode)](#4.2.3. 主机时钟模式 (Host Clock Mode))

[4.3 数据速率模式 (Data Rate Modes)](#4.3 数据速率模式 (Data Rate Modes))

[4.4 核心时序解析 (Timing Stages)](#4.4 核心时序解析 (Timing Stages))

[4.5 寄存器配置模式 (Register Configuration)](#4.5 寄存器配置模式 (Register Configuration))

[5.1 30 位精度的理论推导](#5.1 30 位精度的理论推导)

[5.1.1. 理论基础:噪声的统计学特性](#5.1.1. 理论基础:噪声的统计学特性)

[5.1.2. 增加位数的数学公式](#5.1.2. 增加位数的数学公式)

[5.1.3. 为什么硬件是 24 位,输出能给 30 位?](#5.1.3. 为什么硬件是 24 位,输出能给 30 位?)

[5.1.4. 实现 30 位精度的前提条件](#5.1.4. 实现 30 位精度的前提条件)

[5.1.5. 30 位精度的实际意义](#5.1.5. 30 位精度的实际意义)

前言

针对 AD4030-24(2MSPS) 这款高性能 24 位 SAR ADC,本文将从架构、特点、引脚、时序四个核心维度进行深度的笔记学习。

1. 架构 (Architecture)

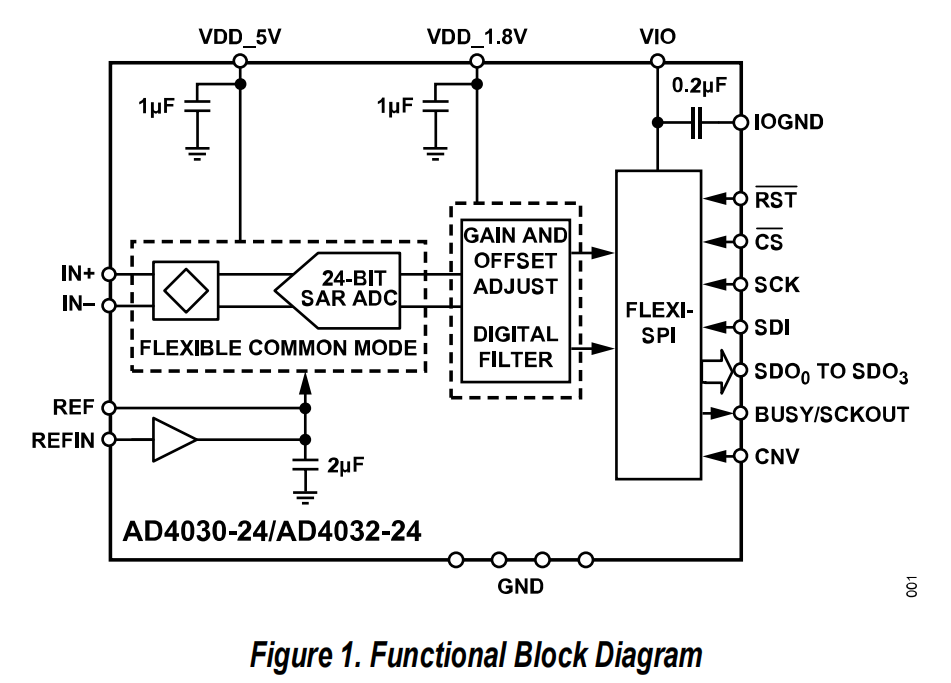

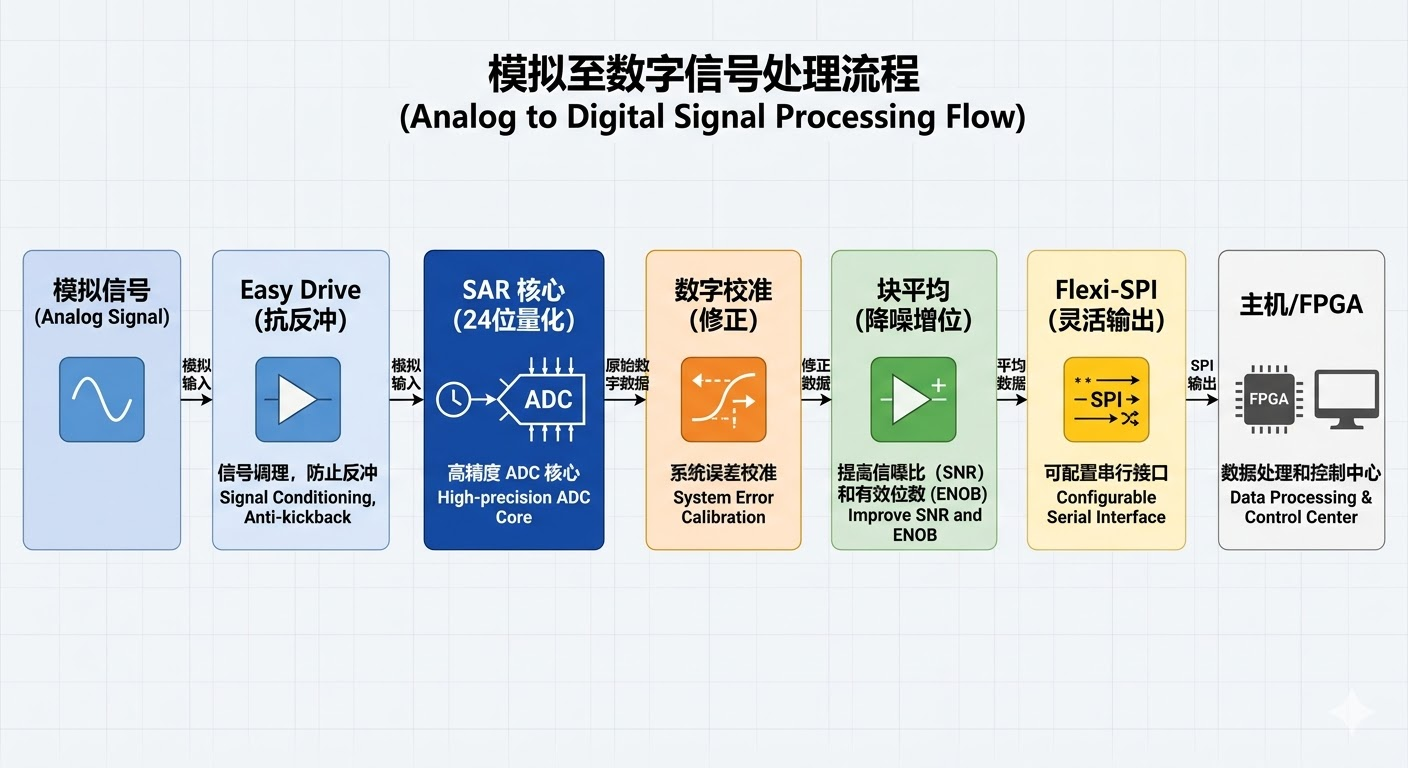

AD4030-24芯片的架构如图1-1所示。

图1-1 AD4030-24芯片的架构

图1-1 AD4030-24芯片的架构

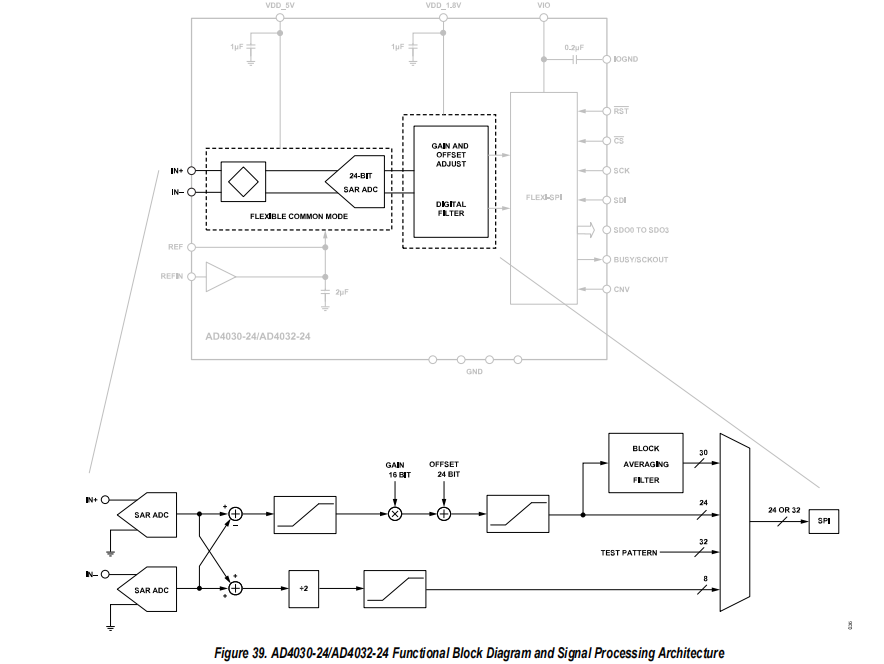

AD4030-24 采用了先进的逐次逼近寄存器 (SAR) 型架构,其内部设计不仅包含高精度的转换核心,还集成了丰富的信号调理和数字处理功能。将 AD4030-24 的工作流程从模拟信号输入 到数字数据输出进行拆解,可以看作是一场信号的"数字化之旅"。以下是按信号流向排列的各模块功能深度解析,结构图和流程图分别如图1-2、如图1-3所示:

图 1-2 AD4030-24/AD4032-24功能框图与信号处理架构

图 1-2 AD4030-24/AD4032-24功能框图与信号处理架构

图 1-3 采样流程图

图 1-3 采样流程图

(1). 模拟前端与 Easy Drive (信号的入口与调理)

-

模拟输入引脚 (IN+/IN-):接收全差分信号。

-

预充电缓冲器 (Precharge Buffer):

-

功能:在采样电容与外部电路接通前的瞬间,先由内部缓冲器将电容充电至上一周期的电压值。

-

意义:消除采样时刻产生的动态电荷反冲(Kickback)。这使得即使前端驱动放大器的带宽较低,信号也能快速稳定,从而保证了 2 MSPS 下的高精度。

-

(2). SAR 转换核心 (模拟转数字的核心)

-

采样保持 (Sample-and-Hold) :由 CNVI 信号的上升沿触发,将当前的模拟电压"冻结"在内部电容阵列(CDAC)上。

-

逐次逼近 (Successive Approximation):

-

功能:内部高速比较器配合逻辑电路,像"天平称重"一样,通过 24 次比较(由高位到低位),确定输入电压对应的 24 位二进制代码。

-

基准电压缓冲器 (Reference Buffer) :转换过程中,CDAC 需要频繁从基准源抽取电荷。内置的缓冲器和 2 µF 去耦电容提供了极快的电流响应,确保每一位转换的电平参考都是绝对稳定的。

-

(3). 数字信号处理模块 (数据的精加工)

转换得到的原始 24 位数据进入数字域,进行增强处理:

-

偏移与增益校准 (Offset & Gain Correction):

- 功能:根据寄存器中预设的校准值,自动通过硬件加法器和乘法器修正系统误差(如传感器带来的固有偏置)。

-

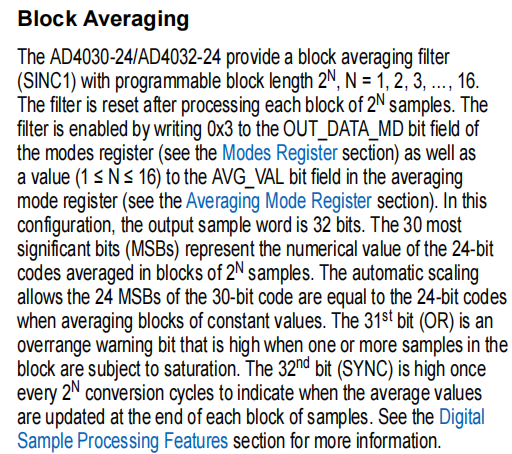

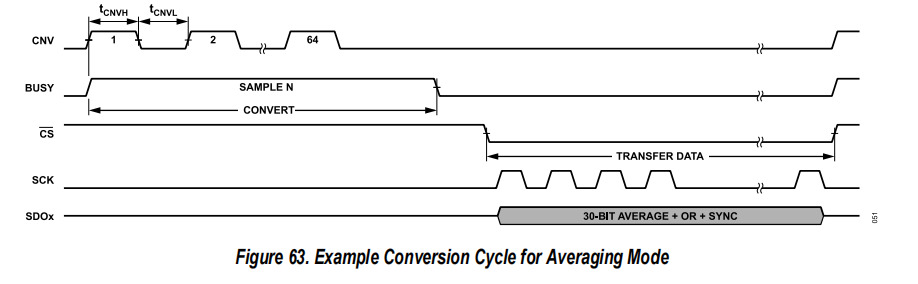

块平均滤波器 (Block Averaging Filter):

-

功能 :对连续的

(N 最大为 16)个样本进行求和平均。

-

意义 :类似于"过采样"技术,它能滤除宽带白噪声。通过大量平均,数据的有效位数(ENOB)显著增加,输出精度可从 24 位提升至 30 位 。速度换取精度,AD4030-24 的硬件核心始终以最高 2 MSPS(即每秒 200 万次)的速度对模拟信号进行"抓取"和量化。

-

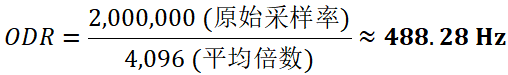

原始数据(24-bit) :频率为 2 MSPS。

精度提升需求 :增加 6 位(

)。

平均倍数(Decimation Ratio) :根据

理论,需要平均

个样本。

最终输出速率:

结论: 当你想要稳稳地拿到 30 位 精度的数据时,ADC 每秒钟只会给你发送约 488 个 数据点。

其实这个地方有点奇怪,已经可以达到30位的精度了。为什么最大是对

样本进行求和平均呢?

在 AD4030-24 的数字处理模块中,设置

次和

次块平均(Block Averaging)的核心区别在于"牺牲速度换取精度的程度"。

根据数据手册(第 21-23 页及性能表),这两者的具体差异如下表所示:

核心参数对比表(以 AD4030-24 的 2 MSPS 采样率为准)

特性参数 212 次平均 (N=12) 216 次平均 (N=16) 区别与影响 平均样本数 4,096 个样本 65,536 个样本 是

的 16 倍

输出数据速率 (ODR) 488.3 Hz 30.5 Hz 极慢,仅适用于准静态信号

理论处理增益 理论上比

多降噪 12 dB

典型动态范围 (DR) 约 145 dB 155.5 dB 达到了芯片的物理极限

有效分辨率增量 增加 6 位 (理论) 增加 8 位 (理论) 两者均输出 30-bit 字长,但 更稳

测量群延迟 约 2.05 ms 约 32.8 ms 的实时性极差,响应延迟大

(1)噪声底(Noise Floor)与动态范围

次平均:能显著滤除宽带白噪声。对于大多数深空探测中的精密传感器,145 dB 的动态范围已经远超模拟电路前端的信噪比上限,能够看到非常细微的信号波动。

次平均 :这是该芯片的极限模式。此时 1/f 噪声(闪烁噪声)开始成为主导因素。虽然理论上应增加 48 dB 增益,但手册显示实际动态范围为 155.5 dB(相对于 109 dB 的原生值增益了 46.5 dB),说明最后那 2 位提升已经由于 1/f 噪声而产生了收益递减。

(2). 输出数据频率(ODR)

(488 Hz):这个频率下,你仍然可以捕捉到一些超低频的机械振动或缓慢变化的物理场。

(30 Hz) :数据刷新率极低,每秒仅 30 个点。这通常用于极高精度的基准校准,或者监测像行星际磁场这种变化极其缓慢的物理量。

(3). 30位字长的填充质量

虽然在这两种模式下,芯片通过 SPI 发送的都是 30-bit 的数据包,但:

在

模式下,最后几位(LSBs)仍然会有明显的随机跳动。

在

模式下,由于平均点数巨大,输出的数值会表现得像"定格"一样稳定,这种稳定性对于需要极高单调性的算法(如搜索淹没在底噪中的单音信号)非常有益。

2026-03-23-lhw:目前还没找到原因。

(4). 数据封装与状态监测 (信息的完善)

在输出前,芯片会为转换结果添加"元数据":

-

过压检测 (Overrange Bit):实时监测输入信号是否超出量程,并以状态位形式告知主机。

-

同步标志 (SYNC Bit):在执行块平均时,标记一组平均数据的开始。

(5). Flexi-SPI 接口 (数据的最终传输)

-

串行序列化 (Serializer):将并行计算好的 24-bit(或 30-bit)数据转换为串行流。

-

多通道分发 (SDO Lanes):

-

功能:可以配置 1 个、2 个或 4 个数据引脚同时输出。

-

意义:在 2 MSPS 的高流速下,通过增加"车道"(SDO 通道),可以降低单根线的时钟频率(SCK),从而减少电磁干扰(EMI)并降低对 FPGA 接口速率的要求。

-

-

时钟模式控制:

- 回声时钟 (Echo Clock):在输出数据的同时,送出一个同步时钟。这对于通过数字隔离器传输数据的系统至关重要,能完美补偿信号延迟。

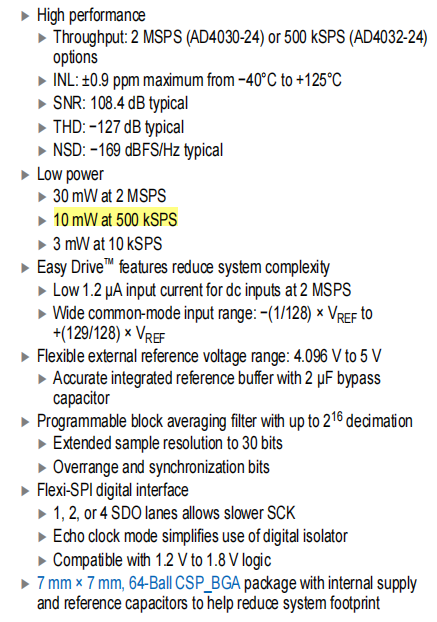

2. 特点 (Features)

该芯片的主要技术指标使其处于精密测量领域的前沿:

-

极高的线性度 :最大积分非线性 (INL) 仅为 ±0.9 ppm,且保证 24 位无丢码,适合极高精度的直流和低频信号测量。

-

卓越的动态性能:

-

典型信噪比 (SNR) 为 108.4 dB。

-

通过内置滤波器平均后,动态范围最高可达 155.5 dB。

-

-

Easy Drive 技术:支持更长的采集相位,允许使用更低带宽、更低功耗的驱动放大器,甚至可以直接由高阻抗源驱动。

-

Flexi-SPI 接口:支持 1、2 或 4 个 SDO 通道,允许以较低的时钟频率读取高速转换数据,降低系统 EMI。

-

低功耗 :在 2 MSPS 满速运行时,总功耗仅约 30 mW,非常适合高密度多通道系统。

-

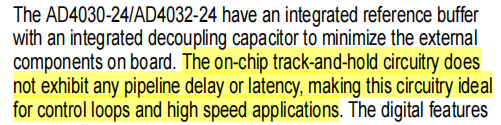

低延迟:从采集到输出仅有0.3us的延迟。

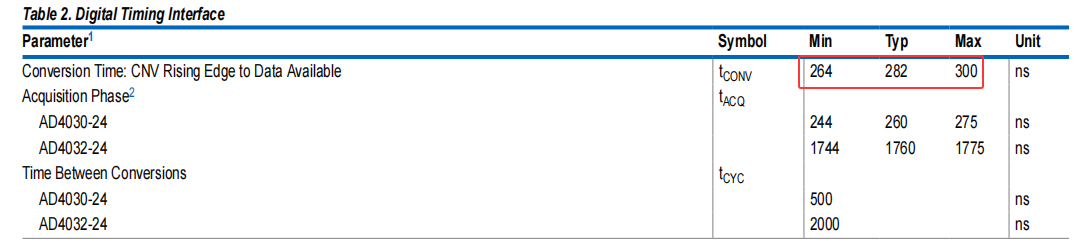

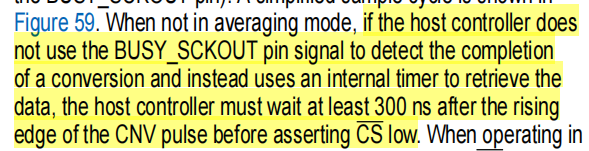

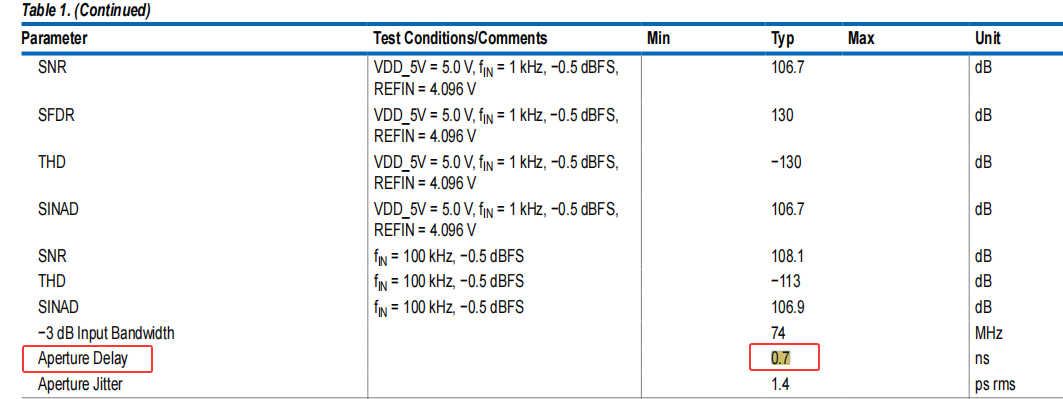

该系列 ADC 的采样输出延时主要体现在以下几个方面:

流水线延迟 (Pipeline Delay): 该器件的片内跟踪保持电路不具备任何流水线延迟或延迟 (latency) 。转换结果在单次转换完成后即可立即读取 。

转换时间 (Conversion Time,

): 指从 CNV 上升沿到数据可用的时间。其典型值为 282 ns ,最大值为 300 ns 。

在转换完成(BUSY 信号变为低电平)后,主机控制器可以立即开始读取数据。如果主机不使用 BUSY 信号而是通过内部定时器触发读取,则必须在 CNV 脉冲上升沿之后等待至少 300 ns 才能将 拉低 。

- 孔径延迟 (Aperture Delay): 指从 CNV 输入上升沿到输入信号被保持用于转换之间的时间,典型值为 0.7 ns 。

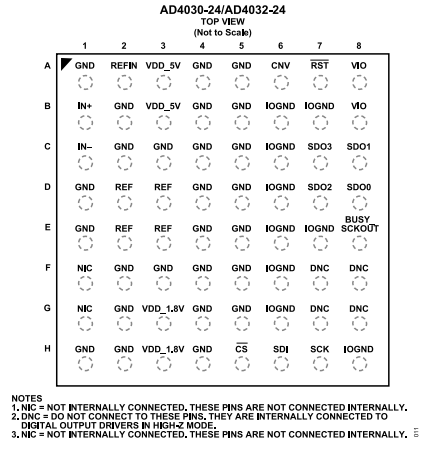

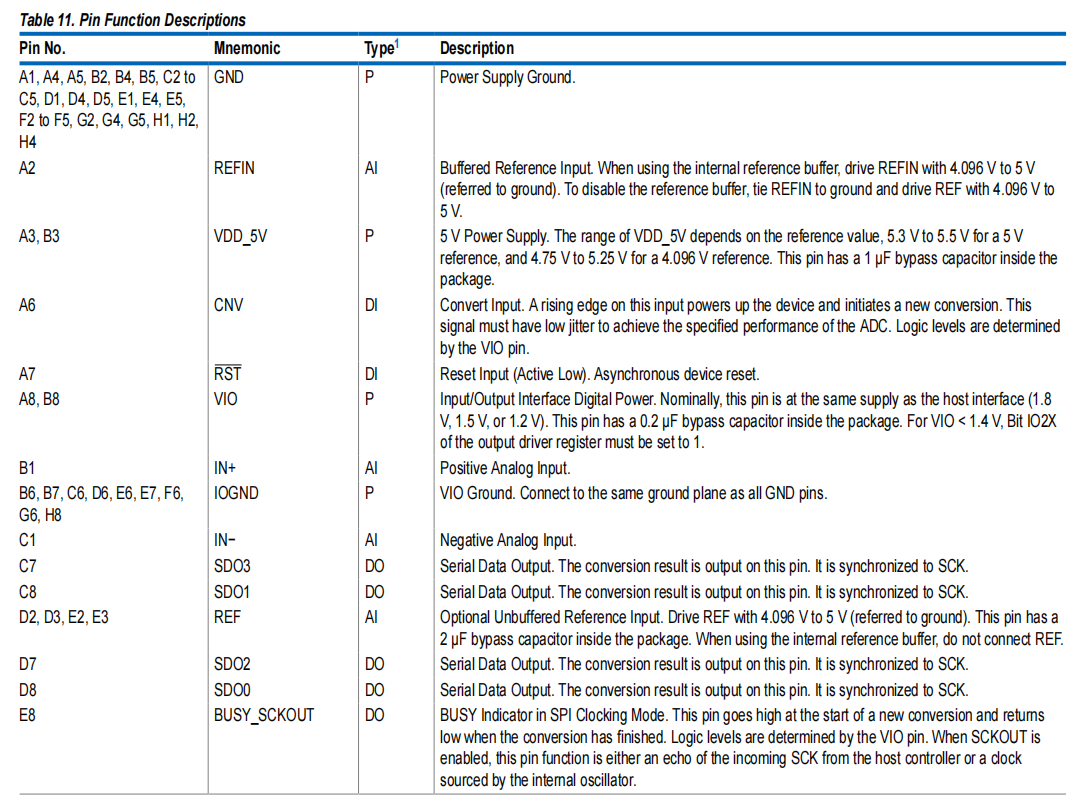

3. 引脚功能 (Pin Configuration)

AD4030-24 采用 7 mm × 7 mm, 64-Ball CSP_BGA 封装。引脚可分为模拟、电源和数字接口三大类:

-

模拟接口:

-

IN+, IN-:全差分模拟输入端。

-

REF, REFGND:基准电压输入及回流地。

-

REFIN:内置基准缓冲器的输入端。

-

-

电源引脚:

-

VDD_5V:模拟 5V 电源。

-

VDD_1.8V:数字核心电源。

-

VIO:数字接口电源(支持 1.2V 至 1.8V 逻辑电平)。

-

-

数字接口 (Flexi-SPI):

-

CNVI:转换开始信号输入,上升沿触发采样和转换。

-

SCK:串行数据时钟。

-

SDO0 - SDO3:多通道串行数据输出。

-

SDI:串行数据输入,用于配置寄存器。

-

BUSY/GP01:状态指示引脚,可配置为忙状态输出、回声时钟(Echo Clock)或通用 I/O。

-

4.运行模式

AD4030-24 的数字接口被称为 Flexi-SPI ,它的"模式"可以从物理连接(通道数) 、时钟架构 和采样处理 三个维度来划分。对于 FPGA 设计来说,最需要关注的是串行接口模式,因为这直接决定了你的 Verilog 状态机逻辑。

4.1 接口拓扑模式 (Data Lane Modes)

根据你FPGA 的 IO 资源紧张程度,可以配置 SDO 引脚的数量:

| 模式 | SDO 引脚占用 | 特点 | 适用场景 |

|---|---|---|---|

| 1-Lane | SDO0 | 标准 SPI,速率要求最高 | 低采样率或高速时钟主控 |

| 2-Lane | SDO0, SDO1 | 数据吞吐量翻倍 | 兼顾布线与速度 |

| 4-Lane | SDO0 - SDO3 | 吞吐量 4 倍,SCK 频率最低 | 2 MSPS 全速采样,降低 EMI |

时序逻辑:在多通道模式下,24 位(或 30 位)数据会分发到不同线路上。例如 4-Lane 模式下,SCK 只需要 6(或 8)个时钟周期就能读完一帧数据。

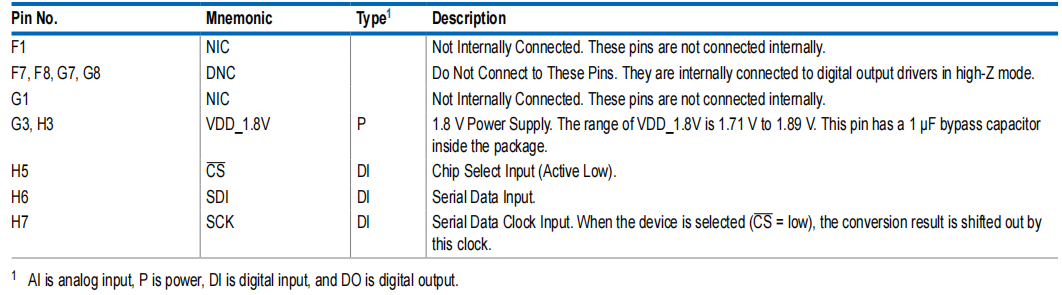

4.2 时钟架构模式 (Clocking Modes)

图 4-1 MODES寄存器

图 4-1 MODES寄存器

这是 Flexi-SPI 的核心,决定了数据与时钟的对齐方式:

4.2.1. 标准 SPI 模式 (Standard SPI)

-

时序:典型的从机模式。FPGA 提供 SCK,ADC 在 SCK 下降沿移出数据,FPGA 在上升沿采样。

-

挑战:由于存在传播延迟(T_{co}),在高速(>50MHz)时,FPGA 很难对齐数据。

4.2.2. 回声时钟模式 (Echo Clock Mode) ------ 建议 FPGA 选用

-

时序 :ADC 在输出数据的同时,在 BUSY/GP01 引脚上输出一个与数据完全同步的反向时钟(Echo Clock)。

-

优势:抵消了 PCB 走线和隔离器的延迟。FPGA 将此回声时钟作为随路时钟,使用其边沿直接锁存数据,非常适合 100MHz 以上的高速传输。

4.2.3. 主机时钟模式 (Host Clock Mode)

-

时序:ADC 使用内部振荡器产生位时钟。

-

场景:适用于异步采集系统,FPGA 无需提供高速位时钟。

4.2.4模式推荐

针对 FPGA + 空间应用 背景:

-

首选配置 :4-Lane + Echo Clock + DDR。

-

理由:深空探测系统对 EMI 极其敏感。这种模式可以用最低的物理时钟频率(SCK)实现最高的数据吞吐量,且 Echo Clock 能保证在辐射环境导致的时延偏移下,数据依然能被 FPGA 准确捕获。

4.3 数据速率模式 (Data Rate Modes)

-

SDR (Single Data Rate):每个 SCK 周期传输 1 bit。

-

DDR (Double Data Rate):在时钟的上升沿和下降沿同时传输数据。

- 注:DDR 通常与回声时钟模式配合使用,进一步降低 SCK 物理频率。

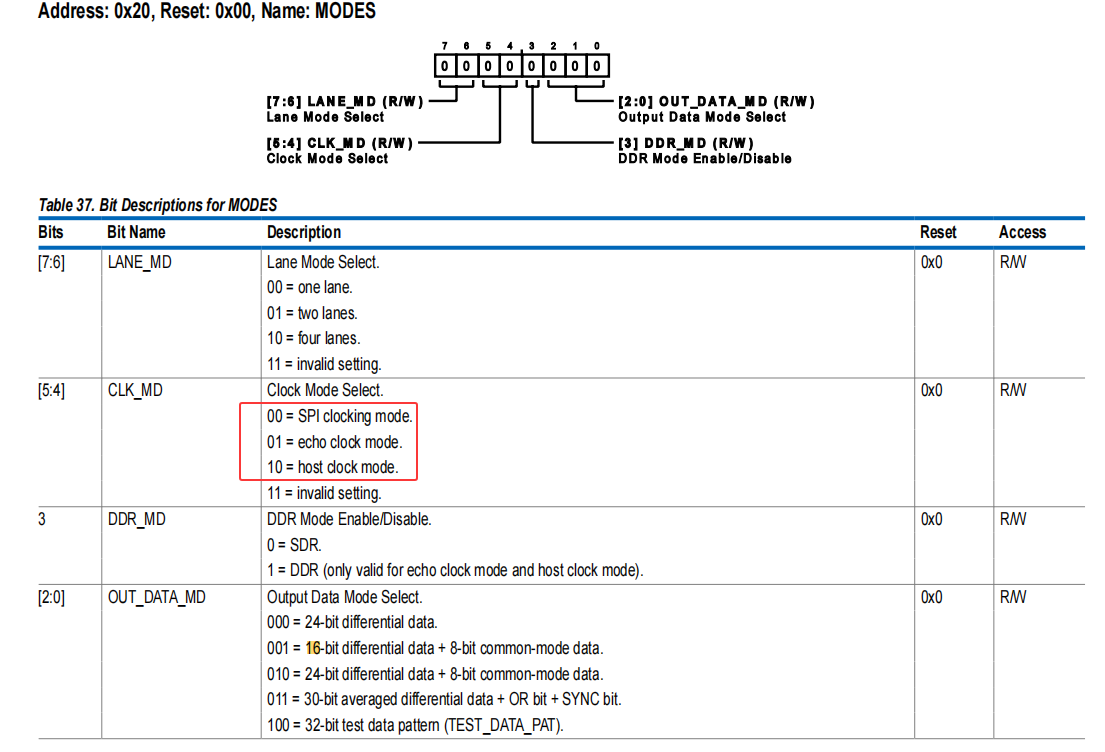

4.4 核心时序解析 (Timing Stages)

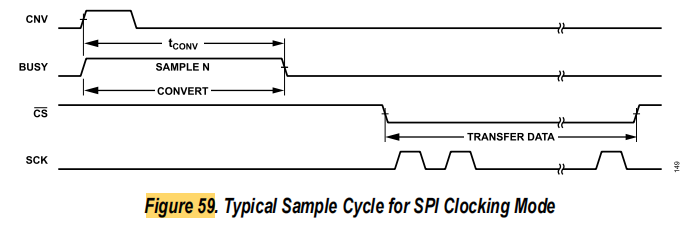

无论哪种模式,一个完整的采样周期都遵循以下时序:

Typical Sample Cycle for SPI Clocking Mode

Typical Sample Cycle for SPI Clocking Mode

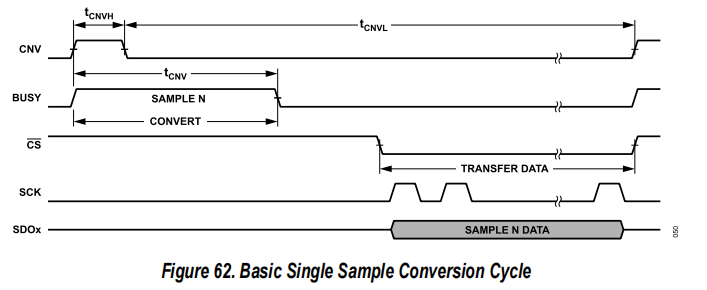

Basic Single Sample Conversion Cycle

Basic Single Sample Conversion Cycle

Example Conversion Cycle for Averaging Mode

Example Conversion Cycle for Averaging Mode

-

转换阶段 (Conversion Phase):

-

CNVI 上升沿 :启动转换。此时 BUSY 变高。

-

转换时间 (

):约 290ns 到 350ns。此阶段内部进行 SAR 逻辑判断。

-

-

采集/读取阶段 (Acquisition/Read Phase):

-

BUSY 下降沿:表示转换完成,数据已准备好。

-

读取窗口:你可以选择在 BUSY 为高时读取(会有轻微噪声干扰)或在 BUSY 为低时读取(最干净)。

-

CNVI 下降沿:控制采样开关再次闭合,开始给电容充电(Easy Drive 开始工作)。

-

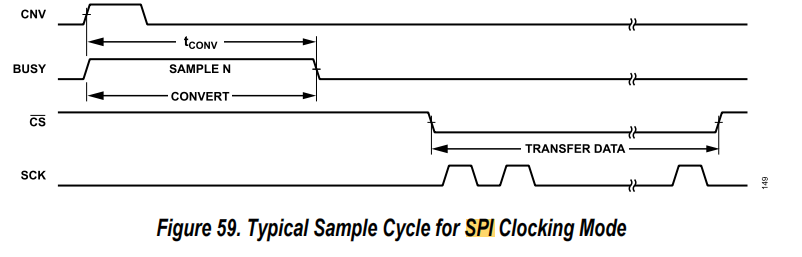

4.5 寄存器配置模式 (Register Configuration)

通过 SDI 引脚,你可以将芯片设为:

-

基本模式:只输出 24 位原始数据。

-

增强模式:输出 30 位平均数据 + 8 位状态字节(包含过压标志、配置验证等)。

5.拓展

5.1 30 位精度的理论推导

从 24 位提升到 30 位精度的核心原理在于过采样(Oversampling)和数字平均(Averaging)。这不仅仅是简单的数值堆砌,而是利用数学和统计学原理从噪声中"挤"出更多的信息。能达到 30 位精度的原因解析:

5.1.1. 理论基础:噪声的统计学特性

ADC 的测量结果通常包含:真实信号 + 量化噪声 + 热噪声(白噪声)。

在理想情况下,白噪声是随机且均匀分布的。如果我们对同一个信号进行多次测量并求平均:

-

真实信号:是相干的,多次累加后会线性增长。

-

白噪声 :是不相干的,正负随机抵消。根据统计学中的中心极限定理 ,

个样本平均后,噪声的幅度(标准差)会降低到原来的

。

5.1.2. 增加位数的数学公式

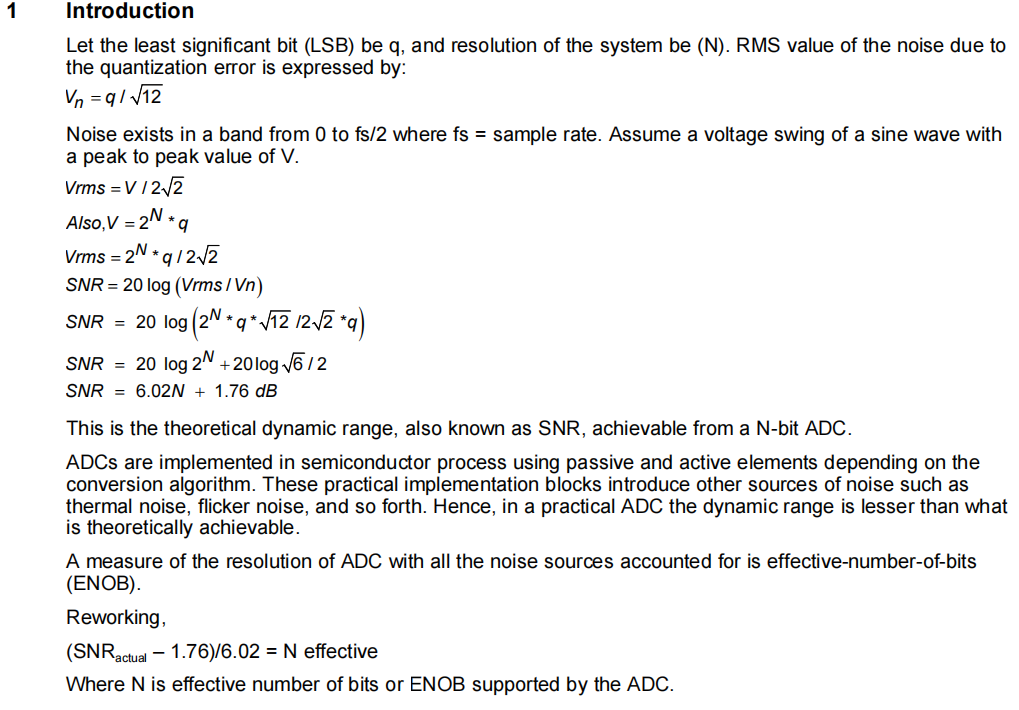

工业界标准文档参考文献如下:

- Analog Devices (ADI) - MT-001 Tutorial : 题目为 "Taking the Mystery out of the Infamous Formula, 'SNR = 6.02N + 1.76dB'"。这是 ADI 最著名的技术指南之一,详细解释了量化噪声、过采样以及处理增益(Process Gain)。链接如下:

- Analog Devices (ADI) - 《Data Conversion Handbook》: 由 Walt Kester 编写,被誉为数据转换领域的"圣经"。书中第 2 章和第 3 章详尽推导了过采样如何降低带宽内的噪声底。链接如下:

The Data Conversion Handbook, 2005 | Analog Devices

- Texas Instruments (TI) - Application Report SLOA249 : 题目为 "Improving Resolution of SAR ADC"。这份报告直接证明了对于 SAR 架构 ADC(如你正在看的 AD4030),通过 OSR=4 的方式可以实现 1-bit 的分辨率增强。链接如下:

Improving Resolution of SAR ADC

本文以Improving Resolution of SAR ADC为例子:

Improving Resolution of SAR ADC

Improving Resolution of SAR ADC

-

理想 ADC 的信噪比公式:

(其中

是位数。可以看到,位每增加 1 bit ,SNR 增加约 6.02 dB。)

Improving Resolution of SAR ADC

Improving Resolution of SAR ADC

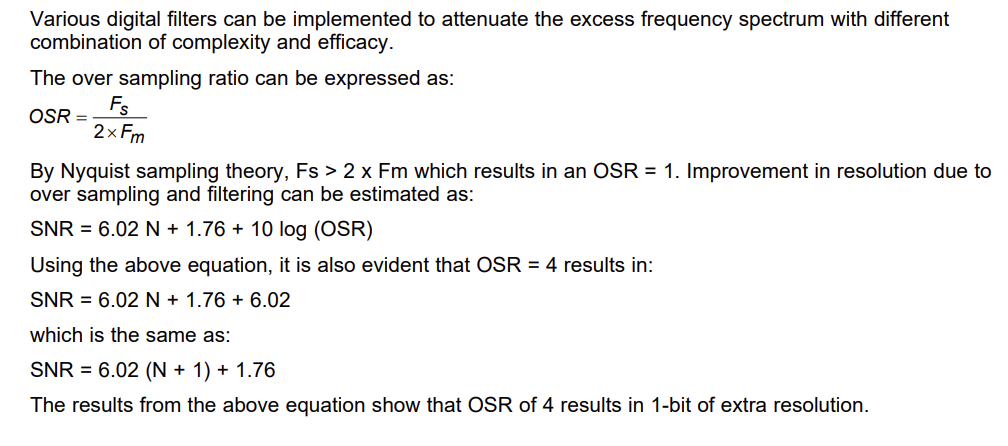

-

带过采样的信噪比改进公式:

(其中

是过采样率。当

时,

,正好补偿了增加 1 bit 所需的信噪比。)

根据信号处理理论,每将采样速率提高 4 倍 并进行求和平均,可以将信噪比(SNR)提高约 6 dB,而 6 dB 恰好对应于 1 位(1-bit)的额外分辨率。

计算公式为:

-

如果要从 24 位提升到 30 位,我们需要增加 6 位。

-

根据公式:

。

-

这意味着,如果你对 4096 个 24 位样本进行平均,你就能在理论上获得 30 位的解析度。

-

AD4030-24 最高支持

(即 65536)次平均,这远超 30 位所需的样本量,因此它可以稳稳地输出 30 位数据。

5.1.3. 为什么硬件是 24 位,输出能给 30 位?

这涉及到物理分辨率 与数字分辨率的区别:

-

物理分辨率(24位):这是 SAR ADC 内部电容网络(CDAC)的硬件限制,决定了单次转换能分出的最细刻度。

-

数字分辨率(30位) :在数字域(Digital Domain),芯片内部有一个累加器(Accumulator)。当你把多个 24 位的数据相加时,结果的位数自然会超过 24 位。

-

例如:两个 24 位数相加,结果可能需要 25 位。

-

AD4030 内部将这些高精度累加结果经过处理后,映射到一个 30 位的输出寄存器中。

-

5.1.4. 实现 30 位精度的前提条件

并不是任何时候平均都能增加位数,它需要满足两个关键条件:

-

信号必须包含微量噪声(Dither,抖动):如果信号完全没有噪声且正好落在两个量化阶梯之间,无论平均多少次,结果都一样。幸运的是,在 24 位这种极端精度下,系统中总会有足够的热噪声来充当"抖动",使信号在相邻的量化量级间跳变。

-

噪声必须是白噪声:即噪声在频谱上是均匀分布的随机噪声。

5.1.5. 30 位精度的实际意义

虽然物理上很难保证系统层面的绝对精度达到 30 位(受限于温漂、基准源稳定性等),但 30 位输出提供了极高的相对分辨率:

-

降低底噪:大幅提升动态范围(AD4030 可达 155.5 dB),让你能看到淹没在宽带噪声下的极其微弱的周期性信号。

-

平滑波形:在深空探测或精密物理实验中,30 位数据能提供极细微的信号变化趋势,这对于后续的数字滤波和算法处理非常有利。

5.1.6实例

问:虽然说信噪比变高了,但是为什么就说分辨率提高了呢?

**答:**这是一个非常深刻的问题。直觉上,分辨率(Resolution)是由硬件底层的电容阵列(CDAC)或者刻度"尺子"的大小决定的,而信噪比(SNR)更像是信号的"干净程度"。

为什么信号变干净了,我们就能厚着脸皮说"分辨率提高了"呢?这背后的逻辑在于:过采样和求和平均实际上创造了物理硬件原本不存在的"虚拟刻度"。

(1). 核心矛盾:LSB 的限制

在不使用过采样时,ADC 的分辨率受限于 LSB(最低有效位)。

假设一个 ADC 的 LSB 是

。

如果你输入一个

的信号,ADC 永远输出

。

如果你输入一个

的信号,ADC 还是输出

。

在这种情况下,你无法分辨

和

。这时的分辨率就是

。

(2). 秘密武器:噪声(Dither)

在 24 位 ADC 中,系统由于热噪声的存在,实际上是在"抖动"的。

当你的输入信号是

时,由于噪声的随机叠加,ADC 的单次转换结果可能会跳变:有时候是

,有时候是

。

统计学规律出现了:因为

更靠近

,所以产生

的概率更高(约 80%),产生

的概率较低(约 20%)。

如果我们把这 4096 次跳变的结果加起来求平均,得到的结果会非常接近

。

结论: 噪声原本是敌人,但在过采样中,它变成了"搬运工",把那些淹没在 LSB 以下的微小信号特征,"搬"到了统计分布的概率里。

(3). 从"台阶"到"斜坡"

我们可以用尺子量身高来做类比:

普通 24 位采集 :像是一把刻度为

的硬尺子。你只能说自己是

还是

。

30 位过采样 :你还是用这把尺子,但在测量时你的头在微微晃动(噪声)。你量了 4096 次,发现有 3000 次是

,1096 次是

。

数学处理 :算出的平均值是

。

这时候,虽然尺子的物理刻度没变,但你通过多次测量(牺牲时间) ,获得了一个比

更精细的解析能力。这个

就是那多出来的"位数"。

(4). 深度理解:SNR 与分辨率的关系

在信息论中,分辨率本质上是衡量你能从信号中提取多少有效信息。

维度 单次采样 (24-bit) 块平均后 (30-bit) 噪声底 (Noise Floor) 较高,淹没了微小变化 极低,微小变化浮现出来 最小可辨别信号 1 \\text{ LSB} 远小于 1 \\text{ LSB} (即子 LSB 级) 信噪比 (SNR) 108.4 \\text{ dB} 155.5 \\text{ dB} 实际意义 只能看到信号的大轮廓 能看到信号波形上极细微的毛刺或趋势 一句话总结:

信噪比的提高意味着你排除了干扰。当干扰(噪声)被压得比原始硬件的最小刻度(LSB)还要小时,你就可以通过数学计算,把原本被噪声掩盖的、位于两个物理刻度之间的"中间值"给找回来。

这就是为什么像 AD4030-24 这种芯片,通过内部数字滤波器(Decimation Filter)把数据位宽从 24 位扩展到 30 位------因为它认为这些多出来的位里装的是真实的信息,而不再仅仅是随机的噪声。

总结: 30 位精度是通过"用速度换精度"的策略实现的。ADC 跑得比你需要的快(2 MSPS),然后把多出来的这些样本在内部"揉"在一起,剔除随机噪声,最终提炼出更高精度的数据。

5.2 典型应用电路

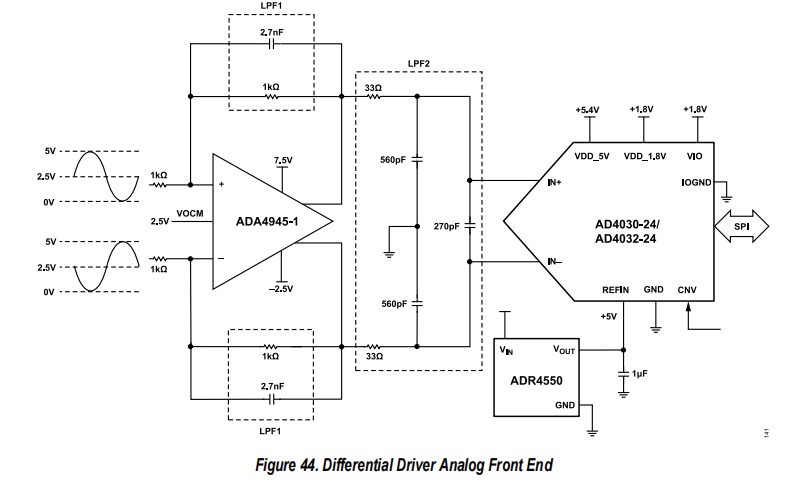

差动驱动模拟前端电路

差动驱动模拟前端电路

图中展示了一个典型的高性能、低功耗差分驱动模拟前端(AFE)电路 ,专门设计用于驱动高分辨率(24位)的逐次逼近型(SAR)模数转换器(ADC)。整个电路的设计核心是实现信号的精密调理、噪声滤除以及与ADC采样特性的阻抗匹配。

(1). 核心驱动放大器:ADA4945-1

ADA4945-1 是一款高速、全差分放大器(FDA)。

功能:它负责接收差分输入信号,并将其调整到适合 ADC 采样的电平范围。它具有极低的失真和噪声,能够维持 24 位 ADC 所需的信号完整性。

电压增益 :由反馈电阻(

)与输入电阻(

)的比值决定。该电路配置为单位增益 (

)。

共模电压(VOCM) :其

VOCM引脚接入了电压。这意味着放大器会自动将输出信号的中心电平偏移至

,这正好是

基准电压的一半,确保了信号在 ADC 的满量程范围内。

供电系统 :采用

和

的非对称供电。这种设计通常是为了在提供

到

输出摆幅时,确保放大器输出级有足够的余量(Headroom),从而提高线性度。

(2). 双级滤波网络

电路设计了两个低通滤波器(LPF)来优化信噪比:

第一级(LPF1,反馈回路中):

由

电阻和

电容并联组成。

截止频率 :

。

作用:作为抗混叠滤波器,在信号进入 ADC 前限制带宽,降低高频噪声。

第二级(LPF2,ADC 输入前):

由

电阻和一组电容(

和

)组成。

作用 :这是 SAR ADC 驱动电路中至关重要的 RC 电荷踢回(Kickback)滤波器。SAR ADC 在采样瞬间内部电容会切换,产生瞬态电流冲击。这个滤波器能吸收该冲击,使放大器在采样结束前能快速稳定。

(3). 高精度模数转换器:AD4030-24 / AD4032-24

分辨率:24位,属于超高精度级别,适合科学测量和精密传感。

输入架构:全差分输入(IN+ / IN-),能有效抑制共模干扰(如 EMI)。

数字接口 :通过 SPI 进行数据传输,

CNV引脚用于控制采样转换的起始。(4). 电压基准源:ADR4550

输出电压 :稳定的

。

作用 :为 ADC 提供"量心"。ADC 的所有量化结果都是基于这个

参考的,因此 ADR4550 的温漂和噪声性能直接决定了整个系统的绝对精度。

其输出端接有

去耦电容,以保证参考电压在采样过程中的动态稳定性。

以上就是本次笔记的内容。