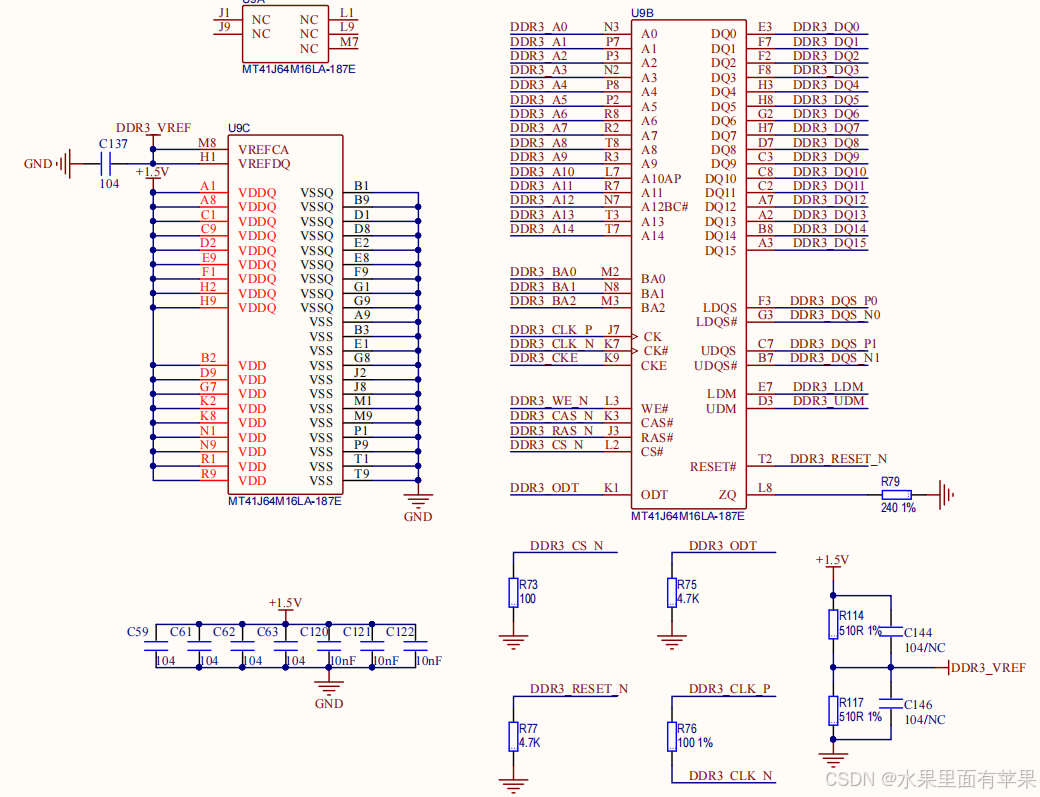

MT41J64M16LA-187E

MT41J64M16LA-187E采用96-ball FBGA封装,尺寸为9mm x 15.5mm,球间距0.8mm。其引脚按功能分为电源、时钟、地址/命令、数据等相关组别。

说明

| 功能组别 | 引脚名称 | 数量 | 作用与说明 |

|---|---|---|---|

| 时钟 | CK, CK# |

2 | 差分时钟输入 。所有地址、命令输入信号均在CK的上升沿和CK#的下降沿交汇处被采样。 |

| 地址/命令 | CKE, CS#, RAS#, CAS#, WE# |

5 | 命令控制 。组合决定具体的操作指令(如读、写、刷新等)。CKE用于时钟使能和进入低功耗模式。 |

| 地址 | A[13:0] |

14 | 地址总线 。用于提供行、列地址。在DDR3中,A[13:0]也用于在初始化时配置模式寄存器。 |

| 体选择 | BA[2:0] |

3 | Bank地址输入。用于选择DDR3内部8个Bank中的一个进行操作。 |

| 数据 | DQ[15:0] |

16 | 数据总线。双向传输。总容量1Gb,数据位宽16位,因此内部组织为64M x 16。 |

| 数据选通 | DQS, DQS# DQS[1:0], DQS#[1:0] |

4 | 差分数据选通信号。在读取时由DDR3芯片输出,在写入时由控制器输入,用于精确捕获数据。x16配置有两对,分别对应高8位和低8位数据。 |

| 数据掩码 | DM[1:0] |

2 | 写入数据掩码。用于在写入操作中屏蔽不需要写入的字节。 |

| 片上终端 | ODT |

1 | 动态片上终端使能。用于控制内部终端电阻的开启和关闭,以改善高速信号完整性。 |

| 校准 | ZQ |

1 | 输出驱动校准。需外接一个240Ω (±1%)的精密下拉电阻到地,用于校准输出驱动器的阻抗。 |

| 电源/地 | VDD, VDDQ, VSS, VSSQ VREFCA, VREFDQ |

多 | 核心供电、I/O供电和地 。VDD和VDDQ均为1.5V。VREFCA和VREFDQ为参考电压。 |

| 其他 | RESET# |

1 | 复位引脚。低电平有效,用于将DDR3内部状态机复位到已知状态。 |

需要注意的是,上述引脚功能在**模式寄存器(MRS)**中可以进行配置。例如,驱动强度(如34Ω)可以通过

MR1寄存器进行设置。TDQS(终端数据选通)功能在x16的配置中是不支持的,必须保持禁用状态。

-

电源供电(VDD / VDDQ) :内核电压和I/O电压均为 1.5V ,允许误差范围为±0.075V(即1.425V至1.575V)。这比之前提到的W9825G6KH-6的3.3V要低得多,因此不能混用。

-

片上终端(ODT) :

ODT引脚用于动态控制内部终端电阻的开启与关闭。这在DDR3高速读写中至关重要,可以显著减少信号反射,保证数据传输的完整性。其具体的阻抗值(如RZQ/7 = 34Ω)可通过模式寄存器进行配置。 -

参考电压(VREF) :

VREFCA为命令和地址总线提供参考电压,VREFDQ为数据总线提供参考电压。这两个电压通常应为VDD的一半,即 0.75V,用于判断高速信号的逻辑"0"和"1"。 -

数据掩码(DM) :在写入操作时,

DM信号用于屏蔽特定的数据字节。当DM为高电平时,对应数据位上的写入操作被忽略,这在处理非对齐数据或进行部分字节写入时非常有用。 -

校准(ZQ) :

ZQ引脚通过外接240Ω精密电阻到地,配合芯片内部的校准逻辑,可以实时补偿由于电压和温度变化引起的输出驱动阻抗和ODT阻抗的偏差,确保信号质量始终处于最佳状态。 -