同步计数器和异步计数器

CP脉冲

在数字电路中, CP (Clock Pulse) 指的是时钟脉冲信号, 它是整个时序逻辑电路的心脏或节拍器.

触发器(构成计数器的基本单元)只有在接收到时钟脉冲的有效边沿(比如上升沿或下降沿)时, 才会改变状态.

异步计数器 (Asynchronous Counter / Ripple Counter)

连接方式: 在异步计数器中, 只有第一级触发器连接到了外部的全局时钟脉冲 (CP), 后续的每一级触发器, 其时钟输入端连接的是前一级触发器的输出端.

工作状态(水波纹效应): 就像多米诺骨牌一样, 状态的变化是一级一级传递的, 当时钟到来时, 最低位先翻转;

最低位的翻转再触发次低位的翻转, 以此类推, 这种现象被称为纹波(Ripple).

致命缺点:传播延迟.

因为每一级触发器都有物理响应时间, 当计数器位数很多时, 从最低位传递到最高位的累计延迟会非常大; 在极短的瞬间(过渡态), 计数器的输出会出现短暂的错误值(毛刺现象), 这在高速电路中是不能容忍的.

纹波延迟: 异步计数器中, 时钟需逐级传递, 高位比低位延迟, 如4位计数器从0111→1000时, 各位依次翻转, 产生短暂的错误状态(0111→0110→0100→0000→1000)

毛刺(Glitch): 异步计数器在译码输出时易产生尖峰脉冲, 同步计数器则无此问题.

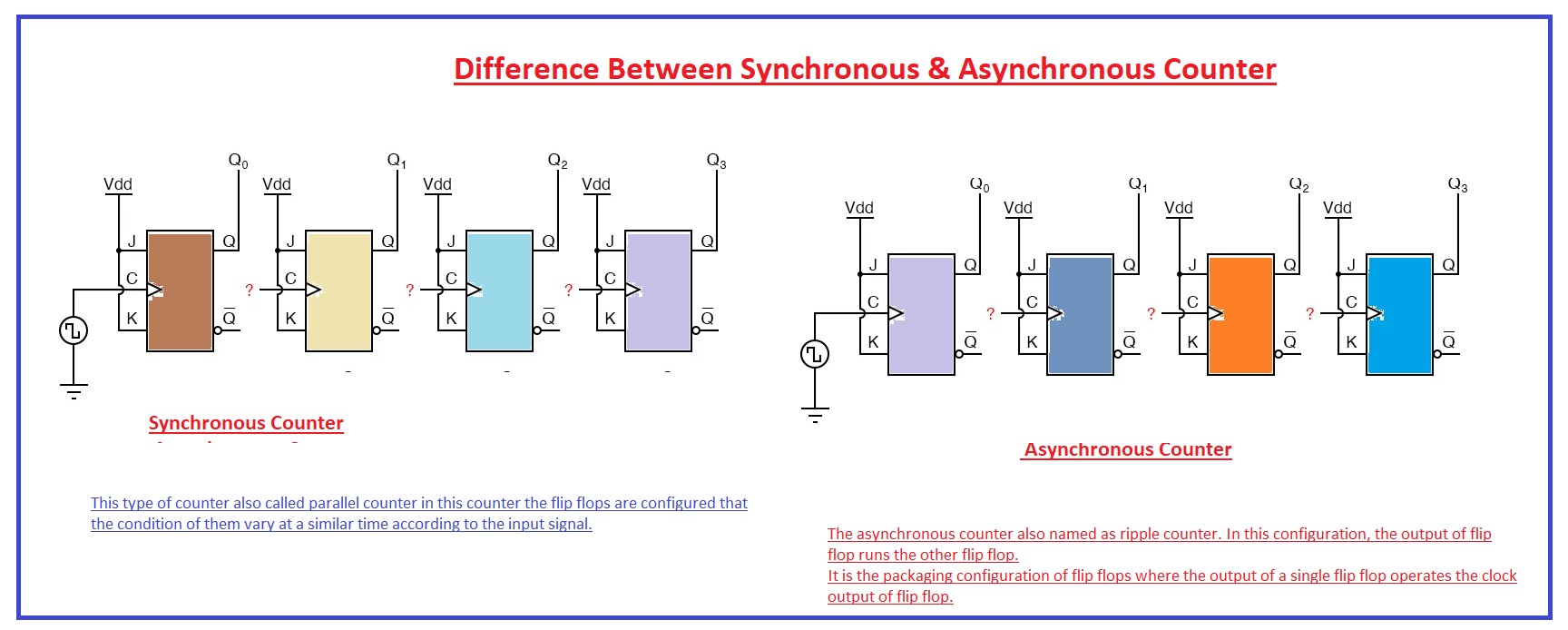

同步计数器 (Synchronous Counter)

连接方式: 在同步计数器中, 外部的全局时钟脉冲 (CP) 同时连接到所有级别触发器的时钟输入端;

工作状态: 当一个时钟脉冲到来时, 所有需要翻转的触发器会在同一瞬间共同改变状态.

既然时钟是同步的, 为了保证它们按正确的逻辑规律计数(比如 001 -> 010), 需要增加额外的逻辑门电路(与门、或门)来提前计算并控制每个触发器的输入端信号.

优点: 速度极快,没有累积的传播延迟, 状态切换干净利落.

例题

同步计数器和异步计数器的区别主要在于 (A)

A. 同步计数器CP脉冲输入端同步

B. 同步计数器清零端同步

C. 同步计数器使用脉冲上升沿或下降沿触发

D. 同步计数器预置信号同步

正确答案:A

详细解释:

这是数字电路中两种计数器的核心区别.

同步计数器 (Synchronous Counter): 所有触发器的时钟脉冲输入端(CP端)都连接在一起, 由同一个时钟信号驱动;

因此, 当有时钟脉冲到来时, 所有需要翻转的触发器会同时动作.

异步计数器 (Asynchronous Counter / Ripple Counter): 只有第一个触发器由外部时钟信号驱动, 后续触发器的时钟输入端由前一个触发器的输出来驱动, 这导致触发器的翻转是逐级传递的, 存在时间上的延迟, 不是同时发生的.

因此,最主要的区别在于时钟脉冲(CP)的输入方式是否同步.

同步 VS 异步

关键区别

同步计数器: 所有触发器的时钟端(CLK)并联连接, 同时接收时钟信号;

异步计数器(纹波计数器/Ripple Counter): 前级触发器的输出(Q)作为后级的时钟, 级联传递.

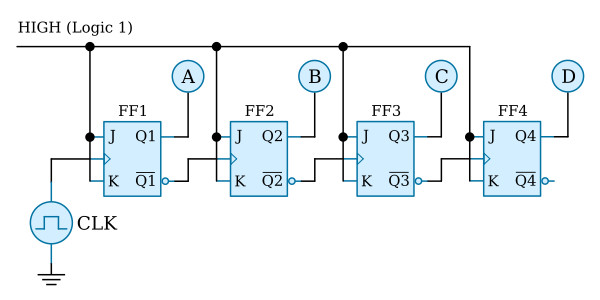

4位异步计数器电路

- 使用4个JK触发器(FF1-FF4)级联;

- 每个触发器的Q‾\overline{\text{Q}}Q输出连接至下一级的时钟端;

- 时钟从LSB(最低位)向MSB(最高位)逐级传递.

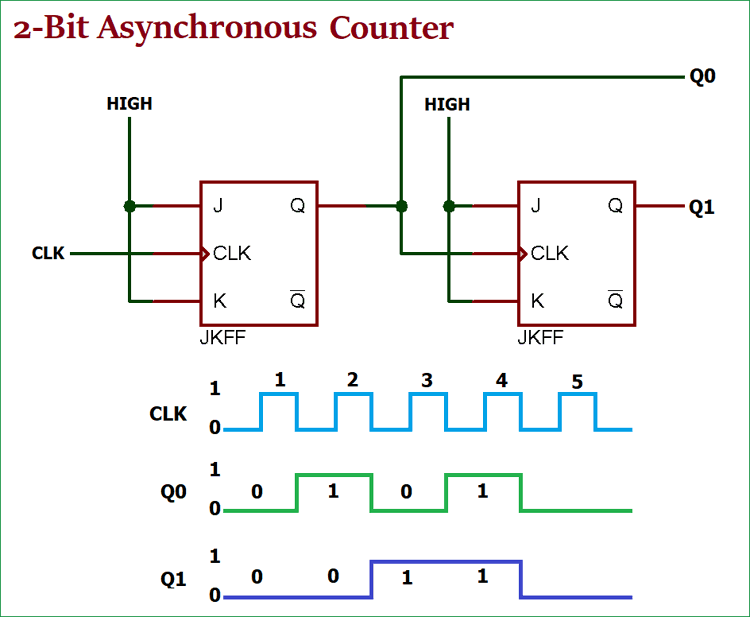

2位异步计数器及波形

电路: CLK → FF0 → FF1(逐级传递)

时序: Q0 在 CLK 下降沿翻转; Q1 在 Q0 下降沿翻转, 产生延迟累积.

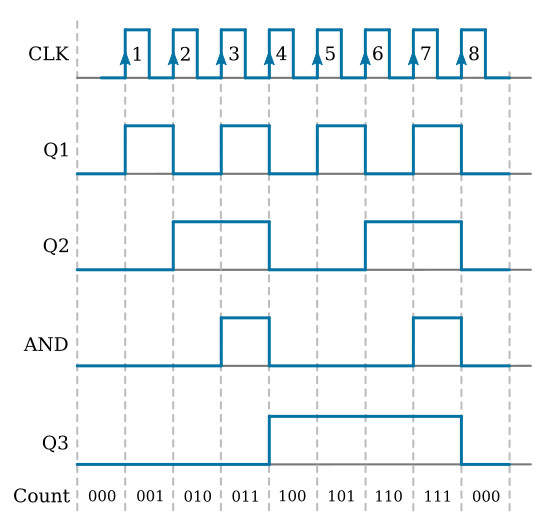

同步计数器时序图

- 所有输出(Q1、Q2、Q3)在时钟上升沿同时翻转;

- 通过与门(AND)控制进位逻辑;

- 计数状态:000→001→010→011→100...