文章目录

- 一、运算器

-

- [1. 原理与功能](#1. 原理与功能)

- [2. 核心组成部件](#2. 核心组成部件)

- 二、控制器

-

- [1. 原理与功能](#1. 原理与功能)

- [2. 核心组成部件](#2. 核心组成部件)

- 三、寄存器组

-

- [1. 分类与特点](#1. 分类与特点)

- 四、指令执行的基本过程

-

- [1. 工作流程](#1. 工作流程)

- 五、CISC与RISC(指令集架构扩展)

- 六、三者关系总结表

- 七、练习

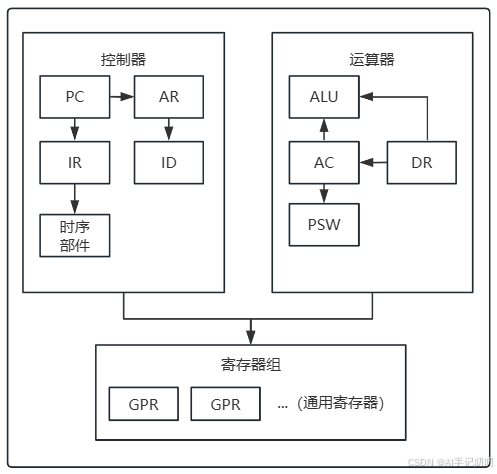

运算器、控制器、寄存器组 是CPU的三大核心组成部分,负责解释指令和处理数据。

一、运算器

1. 原理与功能

运算器 负责执行所有的算术运算 (加、减、乘、除)和逻辑运算(与、或、非、异或、比较)。它接收控制器的命令,对来自寄存器或内存的数据进行加工处理,并将结果暂存或写回。

2. 核心组成部件

运算器主要由以下4个部件组成,考试中常考查其名称与功能的对应关系:

算术逻辑单元(ALU) :运算器的核心,专门负责执行算术运算和逻辑运算。所有数据加工都在ALU中完成。

累加寄存器(AC) :为ALU提供一个工作区,用于暂存参加运算的数据或中间结果。通常至少有一个,是通用寄存器的一种。

数据缓冲寄存器(DR) :作为CPU与内存、外部设备之间数据传送的中转站,用于隔离和缓冲读写速度差异,避免直接访问慢速内存导致的等待。

状态条件寄存器(PSW):保存指令运行结果的状态标志(如进位标志C、溢出标志V、结果为零标志Z、负标志N)以及中断标志、工作状态位等,供控制器判断程序流向。

记忆:ALU负责算,AC存中间,DR做缓冲,PSW记状态。

二、控制器

1. 原理与功能

控制器 是CPU的指挥中心,负责从内存中取出指令,对指令进行译码,并产生各种操作控制信号,按正确的时间顺序发送给运算器、存储器等部件,以保证程序的自动连续执行。

2. 核心组成部件

控制器主要由程序计数器、指令寄存器、指令译码器、时序部件等组成:

程序计数器(PC) :存放下一条要执行的指令在内存中的地址。CPU执行一条指令后,PC会自动增加(+1,即一个指令字长),或根据转移指令、子程序调用指令等改变地址值。

指令寄存器(IR) :存放当前正在执行的指令(包含操作码和地址码/操作数)。从内存取出的指令先送入IR,再供译码。

指令译码器(ID) :分析指令寄存器中的操作码,识别出该指令具体要执行什么操作,并产生相应的控制信号发送给其他部件。

地址寄存器(AR) :保存当前CPU访问内存单元的地址(大多数教材、软考及体系结构教学中,AR 被视为控制器的组成部分)。

时序部件:产生各种时序信号(时钟周期、节拍脉冲),控制各部件在正确的时间点协调工作,保证指令执行的同步性。

易混淆点:PC存地址(指向下一条指令在哪),IR存指令内容(当前指令是什么),ID解析指令(决定要干什么)。

三、寄存器组

1. 分类与特点

寄存器组是CPU内部的高速存储单元,访问速度远高于内存。按功能可分为两类:

专用寄存器 :用途固定,属于运算器和控制器的组成部分(如上述的PC、IR、AC、PSW、DR等)。

通用寄存器:由程序员或编译器规定具体用途,数量因处理器架构而异(如x86有8个,ARM有16个以上),用于存放操作数和中间结果,以减少访问内存的次数,显著提高程序运行速度。

四、指令执行的基本过程

1. 工作流程

冯·诺依曼机采用存储程序方式工作,CPU执行一条指令的过程通常分为以下阶段:

- 取指阶段:控制器根据程序计数器(PC)中的地址,从内存中取出指令,送入指令寄存器(IR);同时PC自动加1,指向下一条指令。

- 译码阶段:指令译码器(ID) 分析IR中的操作码,识别指令类型和所需操作。

- 执行阶段:控制器产生相应的控制信号,运算器(ALU) 执行指令规定的操作(算术运算、逻辑运算、数据传送等)。

- 写回阶段:运算结果写入累加寄存器(AC)或内存,同时状态条件寄存器(PSW) 更新标志位。

五、CISC与RISC(指令集架构扩展)

CPU组成常与指令集架构结合,以下是对比表:

| 类型 | 指令数量 | 指令格式 | 寻址方式 | 控制方式 | 典型架构 |

|---|---|---|---|---|---|

| CISC(复杂指令集) | 多(几百条) | 变长 | 多 | 微程序控制 | x86(Intel/AMD) |

| RISC(精简指令集) | 少(几十条) | 定长(32位常见) | 少 | 硬布线控制 | ARM、MIPS、RISC-V |

结论 :

CISC强调指令功能强大,一条指令可完成复杂操作(如字符串查找),但芯片设计复杂、功耗高。

RISC强调指令简单、执行速度快,每个指令通常在一个时钟周期内完成,适合流水线设计。

"指令种类少"、"定长指令"、"硬布线" → 选 RISC ;"指令丰富"、"变长指令"、"微程序" → 选 CISC。

六、三者关系总结表

| 组成部分 | 核心部件 | 主要功能 | 考点 |

|---|---|---|---|

| 运算器 | ALU、AC、DR、PSW | 算术运算、逻辑运算 | PSW中的状态标志位含义 |

| 控制器 | PC、IR、ID、时序部件 | 取指令、译码、产生控制信号 | PC与IR的功能区分 |

| 寄存器组 | 专用寄存器、通用寄存器 | 高速存储数据/地址 | 哪些属于专用寄存器 |

七、练习

题目1:CPU中,保存当前正在执行的指令的寄存器是( )。

A. 程序计数器(PC) B. 指令寄存器(IR) C. 指令译码器(ID) D. 累加寄存器(AC)

答案:B

解析:指令寄存器(IR)存放当前正在执行的指令。程序计数器(PC)存放下一条指令的地址,指令译码器(ID)负责解析操作码,累加寄存器(AC)暂存运算数据。此题为软件设计师考试高频原题。

题目2:CPU中,跟踪下一条要执行的指令的地址的寄存器是( )。

A. 地址寄存器 B. 指令寄存器 C. 程序计数器 D. 通用寄存器

答案:C

解析:程序计数器(PC)始终存放下一条指令的内存地址。每执行完一条指令,PC自动加1或根据转移指令改变值。这是软件设计师考试几乎每年必考的知识点。

题目3:在CPU的寄存器中,( )用于保存运算结果的状态标志,如进位标志和溢出标志。

A. 累加寄存器 B. 程序计数器 C. 状态条件寄存器 D. 指令寄存器

答案:C

解析:状态条件寄存器(PSW)保存进位标志(C)、溢出标志(V)、结果为零标志(Z)、负标志(N)等状态信息,供控制器判断程序执行流向。

题目4:CPU主要由运算器、控制器和( )组成。

A. 内存储器 B. 寄存器组 C. 系统总线 D. 输入输出接口

答案:B

解析:CPU的三大组成部分是运算器、控制器和寄存器组。内存储器(内存)和输入输出接口不属于CPU,系统总线是连接CPU、内存、I/O设备的公共通道,也不属于CPU内部。

题目5:在指令执行过程中,若需要从内存中读取数据,该数据会先被临时存放在( )中。

A. 累加寄存器 B. 数据缓冲寄存器 C. 指令寄存器 D. 地址寄存器

答案:B

解析:数据缓冲寄存器(DR)作为CPU与内存之间的数据中转站,从内存读取的数据先送入DR,再送往ALU或寄存器;反之,写入内存的数据也先暂存于DR。

题目6:以下关于RISC(精简指令集计算机)的叙述中,正确的是( )。

A. RISC指令系统中的指令种类和寻址方式更多

B. RISC采用变长指令格式,有利于减少程序长度

C. RISC更适合采用硬布线逻辑控制方式

D. RISC的复杂指令通过微程序实现

答案:C

解析:RISC(精简指令集)特点是指令种类少、寻址方式少、指令格式定长、采用硬布线控制(速度快)。CISC(复杂指令集)才采用微程序控制,指令丰富、变长。

题目7:在CPU中,ALU(算术逻辑单元)的功能是( )。

A. 执行算术运算和逻辑运算

B. 存放下一条指令的地址

C. 对指令进行译码

D. 产生时序控制信号

答案:A

解析:ALU是运算器的核心部件,专门负责算术运算(加、减、乘、除)和逻辑运算(与、或、非、异或等)。B是PC的功能,C是ID的功能,D是时序部件的功能。

题目8:CPU执行一条指令的过程通常依次包括( )阶段。

A. 译码、取指、执行、写回

B. 取指、译码、执行、写回

C. 取指、执行、译码、写回

D. 写回、取指、译码、执行

答案:B

解析:标准指令执行流程:先根据PC从内存取指令(取指),再分析操作码(译码),然后执行操作(执行),最后将结果写回寄存器或内存(写回)。

题目9:在下列寄存器中,属于专用寄存器的是( )。

A. 通用寄存器 R0

B. 累加寄存器(AC)

C. 基址寄存器

D. 变址寄存器

答案:B

解析:专用寄存器有固定的功能,如PC(程序计数器)、IR(指令寄存器)、AC(累加寄存器)、PSW(状态条件寄存器)、DR(数据缓冲寄存器)等。通用寄存器(R0等)、基址寄存器、变址寄存器属于通用寄存器,用途可由程序员规定。

题目10:计算机中,CPU的控制器主要依据( )来产生控制信号。

A. 程序计数器的值

B. 指令寄存器的内容

C. 累加寄存器的值

D. 状态条件寄存器的标志

答案:B

解析:控制器中的指令译码器(ID)根据当前指令寄存器(IR)中的操作码,产生相应的控制信号。PC提供取指地址,AC和PSW是执行阶段涉及的寄存器,但不是产生控制信号的直接依据。