转载:(13 封私信 / 81 条消息) PCIe协议学习-TLP Processing Hints(TPH) - 知乎

前序:

TPH是一个optional的用于优化memory请求处理的feature。

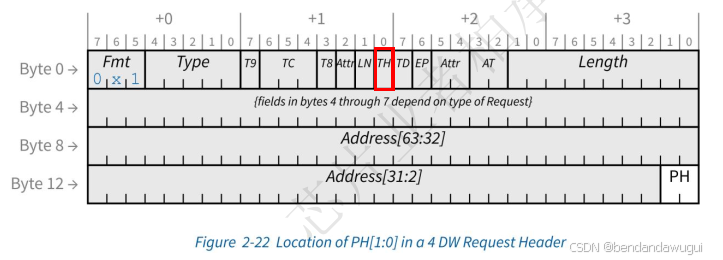

TLP header中,以NFM TLP 为例,与TPH相关的有四个域段:TH(TLP Hints),PH(processing Hints),ST(steering tag),和TPH prefix,其中TH和PH位置如下:

TH为1bit,PH为2bit,当TH=1b时,PH才有效。

| PH[1:0] (b) | 提示类型 | 核心语义 |

|---|---|---|

| 00 | Requester & Target | 设备与主机均会频繁访问该数据(如共享内存区域)。 |

| 01 | Requester | 设备将高频使用该数据(D*D*类:DWDW/DWDR/DRDR)。 |

| 10 | Target | 主机将高频使用该数据(HWDR/DWHR类)。 |

| 11 | Target with Priority | 高优先级目标提示(主机需优先处理,如关键任务数据)。 |

Figure 2-22 中的Byte4-Byte7 映射如下:

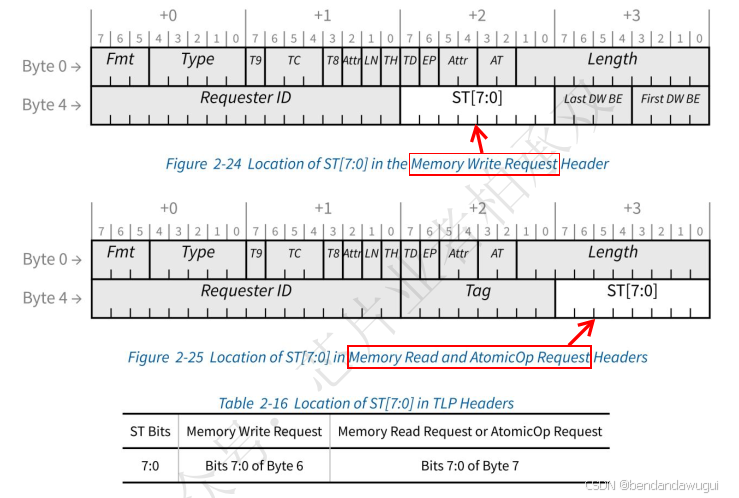

ST [7:0] 在header中的位置有两种,如下图所示,ST[7:0] 为0时,表示tag无效。

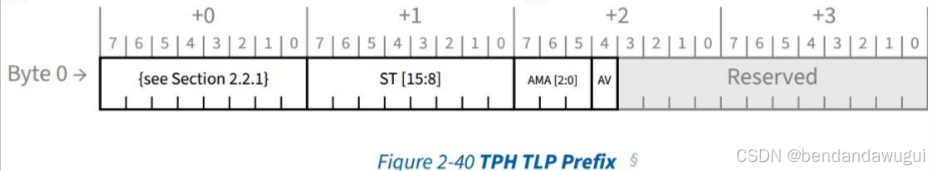

TLP prefix如下图所示,byte0用于指示prefix类型,Byte1为ST[15:8] ,header中TH=0时,TLP prefix也可以存在,用于携带AMA信息(AV bit指示AMA是否有效),但是只有TH=1时,TLP prefix中的ST[15:8] 才是有效的。【TLP prefix 扩展了ST 字段】

AMA表示ATS memory attributes,PCIe协议对AMA描述不多,主要集中在ATS相关章节,AMA的值可以与memory的属性绑定,但是具体如何使用,或者说不同AMA的值代表什么含义,是implementation specific的,在ARM架构中,对AMA似乎没有什么应用。

processing Hints

requester通过processing Hints给RC或者其他EP提供数据的预期使用方式,具体的encoding及含义如下:

| PH[1:0] (b) | 提示类型 | 核心语义 |

|---|---|---|

| 00 | Requester & Target | 设备与主机均会频繁访问该数据(如共享内存区域)。 |

| 01 | Requester | 设备将高频使用该数据(D*D*类:DWDW/DWDR/DRDR)。 |

| 10 | Target | 主机将高频使用该数据(HWDR/DWHR类)。 |

| 11 | Target with Priority | 高优先级目标提示(主机需优先处理,如关键任务数据)。 |

Bi-Directional data structure表示此数据是在host和device之间share的,并且device和host都可能进行读写访问。

D*D*:表示这是device写/读数据,而且device很快会进行数据的读/写回。

DWHR表示此device的写数据很快会被host读取使用(可以将数据放入cache中,减少数据搬移)

HWDR表示此device的数据是host刚写入不久的(数据很可能在cache中)

因此,以ARM架构下的写请求为例,在实际应用时,Bi-Directional data structure/HWDR(PH=00b/10b/11b)都表示数据会被host使用,并且可能很快就被host使用,所以RP在将对应的requester请求转换为总线操作时,可以转换成AXI的writeuniquePtlstash操作(表示将数据写入到shareable localtion并指示数据应该保存在cache中)这样PE/HOST访问时才能更高效,减少数据搬移,而对于D*D*(PH=01b),数据只是device使用,或者TH=0(不清楚数据的使用场景),转换成AXI 的writeuniqueptl即可,表示普通地将数据写入到shareable localtion。

Steering Tags:

在协议上,steering tags用于提供指示host要将数据放到哪个cache中,者其实取决于数据要被哪个processing elements(PEs)使用,对应到ARM架构的AXI总线,就是指示stash操作的target node ID 和 logical processer ID,具体如何映射需要PCIe控制器或者说I/O子系统与总线按照系统的编码规则做好配合。

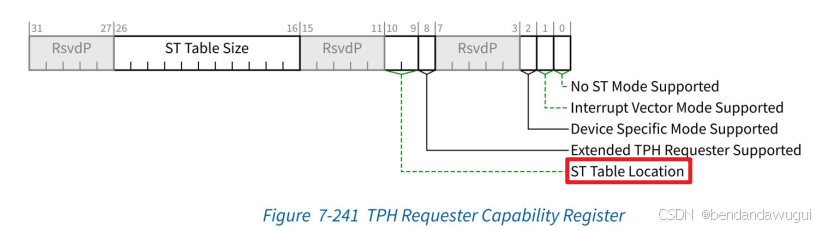

每个fucntion都可以有一个ST table ,ST table可以保存在TPH extended capability 或者MSI-X table中,但是协议规定不能同时在两个位置都保存ST table,当ST table保存在MSI-X Table中时,MSI-X table的vector control register的最高2-byte用于保存具体的steering tag的值,系统软件负责对ST table进行编码,给每一个function分配对应的steearing tags。

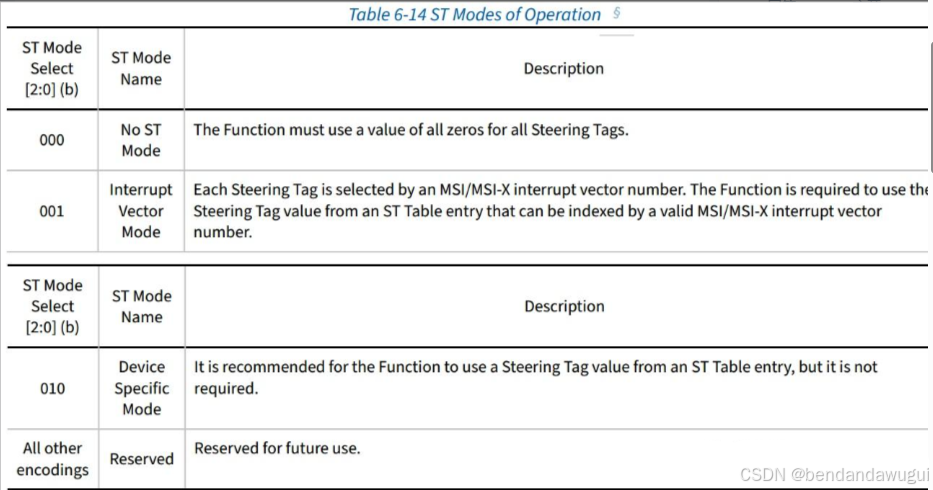

ST Mode of operation:

对于Interrupt Vector Mode,如果function使用MSI-X,则function在发送请求时,可以从MSI-X Table size的范围内选择一个Steering Tag。如果ST Table size比使用的中断vectors的数量要小,则function可以选择在某些transactions中不使用Steering Tag(ST=0),或者从ST Table中选一个有效的Steering Tag。

PCIe协议建议对ST Table进行静态或者准静态编程,以避免出现半新半旧的Steering Tag。

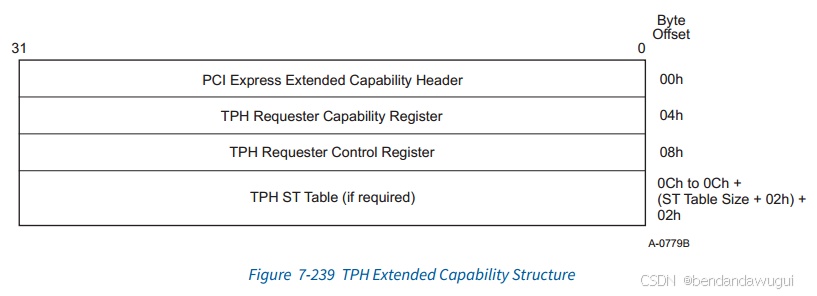

TPH Capability:

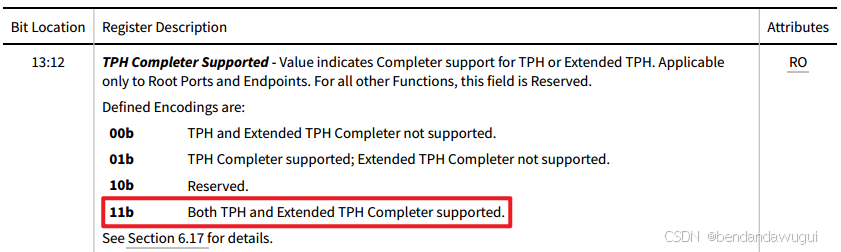

支持产生TPH的function必须有TPH requester extended capability structure,支持处理携带TPH的TLPs的function,必须在device capability 2 register中指示其TPH completer capability。

软件必须配置TPH requester extended capability structure中的TPH requester enable域段,来让fucntion产生带TPH的TLPs。

device capability 2 register 的bit3-12指示其作为TPH completer的支持情况,如下图所示:

extended TPH completer表示function支持TPH TLP prefix,即接收并处理ST的高8-bit以及AMA。

TPH requester extended capability:

由4部分组成:header capability register,control register 和 ST Table:

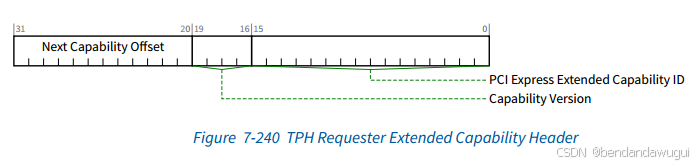

TPH requester extended capability header:

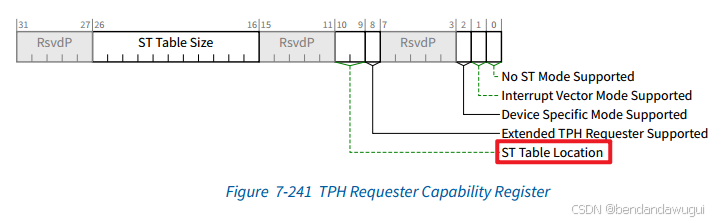

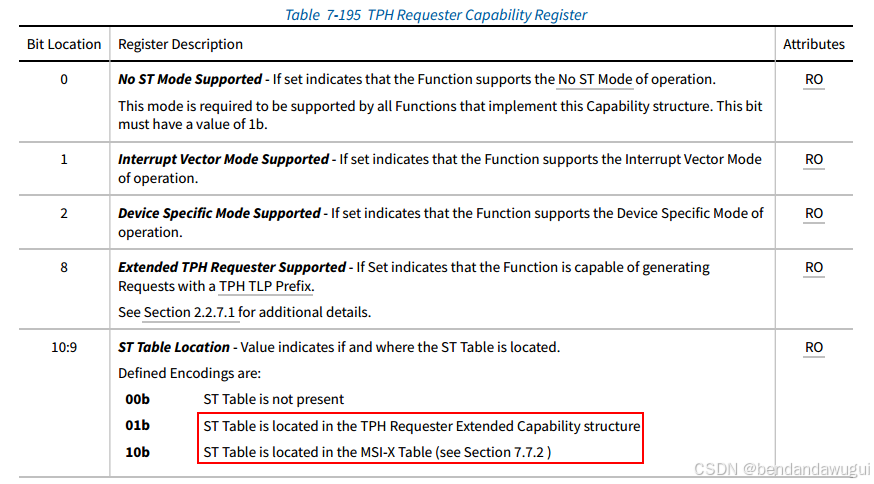

TPH requester capability register (offset 04h):

这里再强调一下,虽然协议允许Function的capability虽然可以同时置位Interrupt Vector Mode Supported和Device Specific Mode Supported,但ST Table的位置只能在一个地方,取决于device的实现。

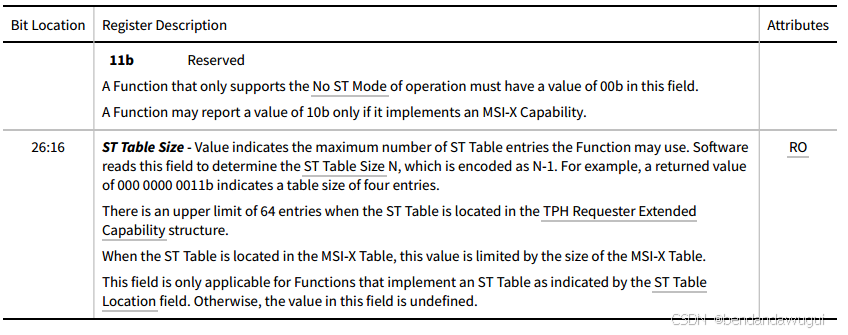

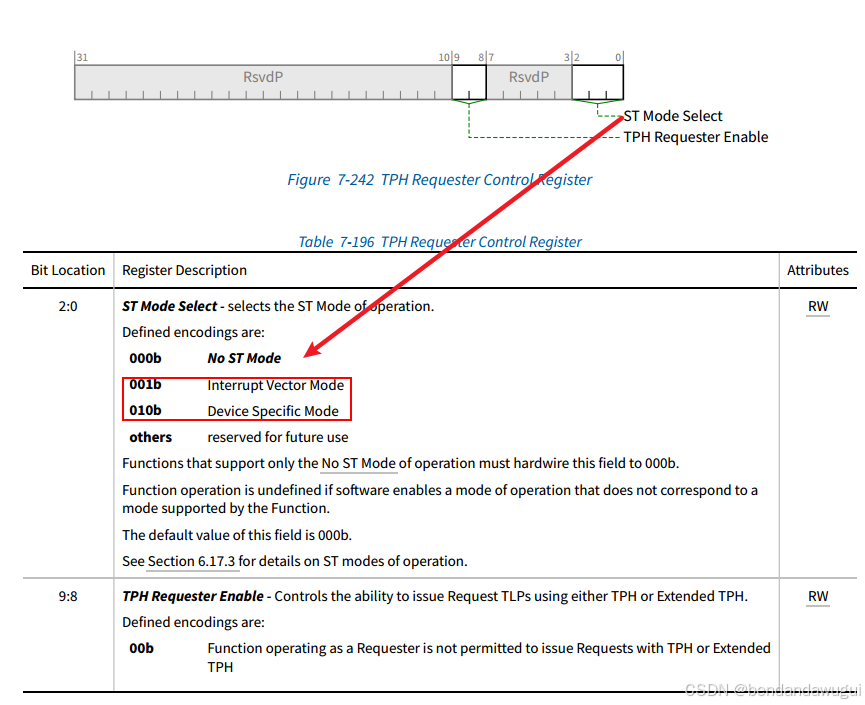

TPH requester control register(offset 08h):

这里的ST Mode Select要和前面的ST Table location匹配

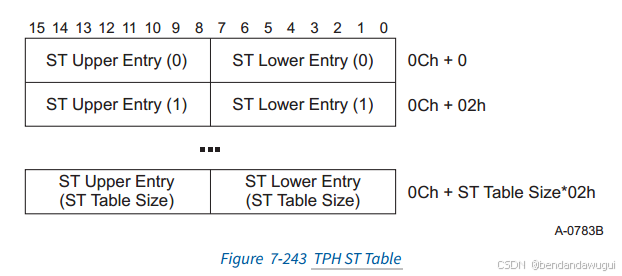

TPH ST table(starting from offset OCh)

ST Table从寄存器偏移0Ch开始,每个Steering Tag占2-Byte大小,具体结束位置取决于function的ST Table Size,但最大不超过64个(前面的寄存器描述里也有提及)。