本分析基于经验数据,核心重点是复介电常数及其温度依赖性,同时也展示了铜粗糙度效应和传导损耗带来的损耗。

所分析和使用的电介质/铜材料如下:

-

一种采用VLP铜箔的"低损耗"材料,测量温度范围为0°C至85°C

-

一种采用RTF铜箔的"中损耗"材料,在室温下测量

-

一种采用RTF铜箔的"高损耗"材料,测量温度范围为0°C至90°C

为确保因果关系,需将提取的原始复介电常数拟合到合适的弛豫模型中。因此,接下来将涵盖以下内容:

-

寻找能最佳拟合弛豫模型的未知变量的过程

-

简要描述本文中使用的弛豫模型:

-

-

德拜模型(Debye)

-

多极德拜模型(Multi Pole Debye)

-

无极模型(Infinite Pole Model)

-

科尔-科尔模型(Cole-Cole)

-

科尔-戴维森模型(Cole-Davidson)

-

哈夫利利亚克-内加米模型(Havriliak-Negami)

-

-

直流电导率(DC conductivity)

-

基于测量数据从上述模型中选择最合适的弛豫模型

-

复介电常数的表格形式在三维求解器中的应用

-

两种材料复介电常数的温度依赖性

-

关于模型、温度及其关系的讨论与比较

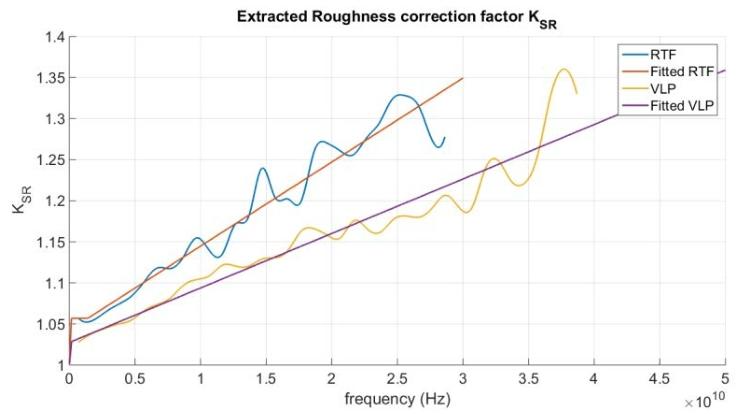

本文中,铜粗糙度效应拟合为多项式函数,因为提取的粗糙度修正因子无法通过现有模型实现宽带拟合。

经验数据的提取

经验数据的提取是通过在印刷电路板(PCB)上的矢量网络分析仪(VNA)测量结构,采用爱立信宽带提取(EBBE)算法完成的。采用分解方法分离复介电常数、铜粗糙度效应和传导损耗。

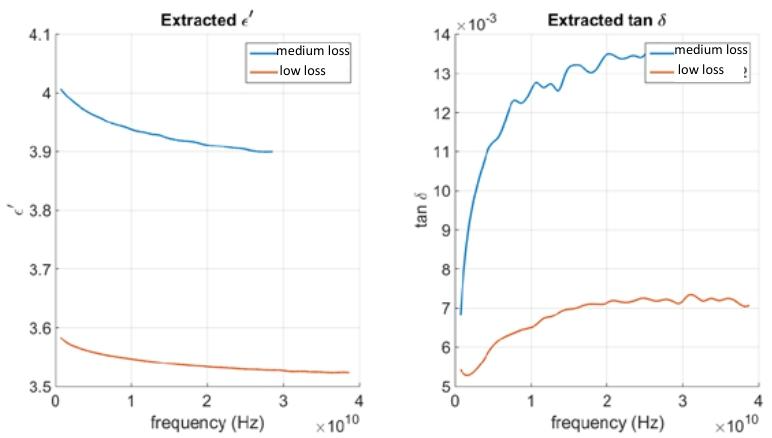

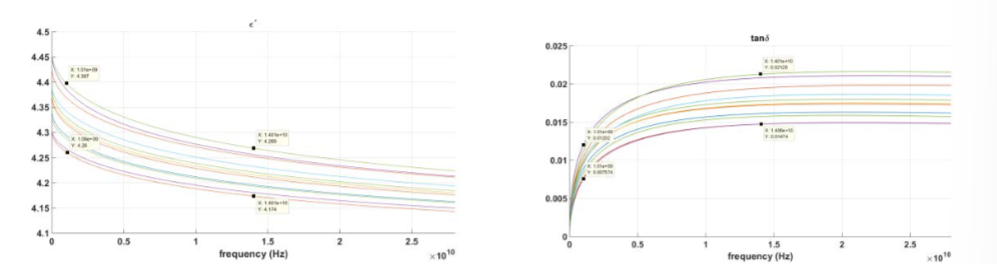

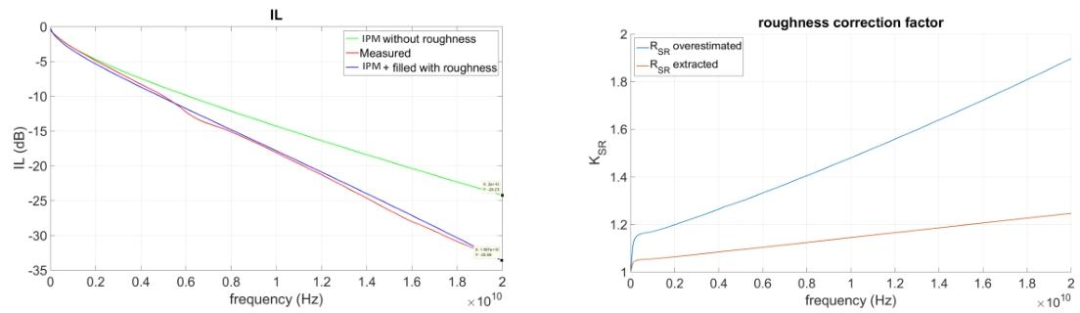

两种上述材料在室温下的ε'、tanδ和KSR的原始提取经验数据如图1至图2所示。

图1:提取的复介电常数

图2:提取的粗糙度修正因子

与去嵌入带状线的提取结果比较

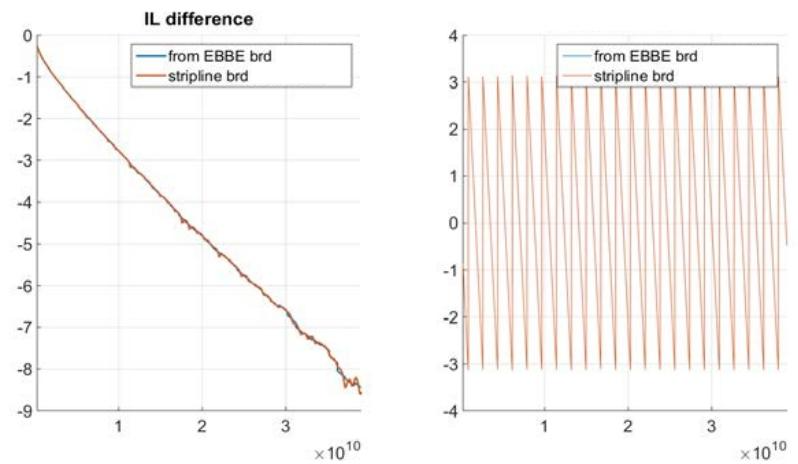

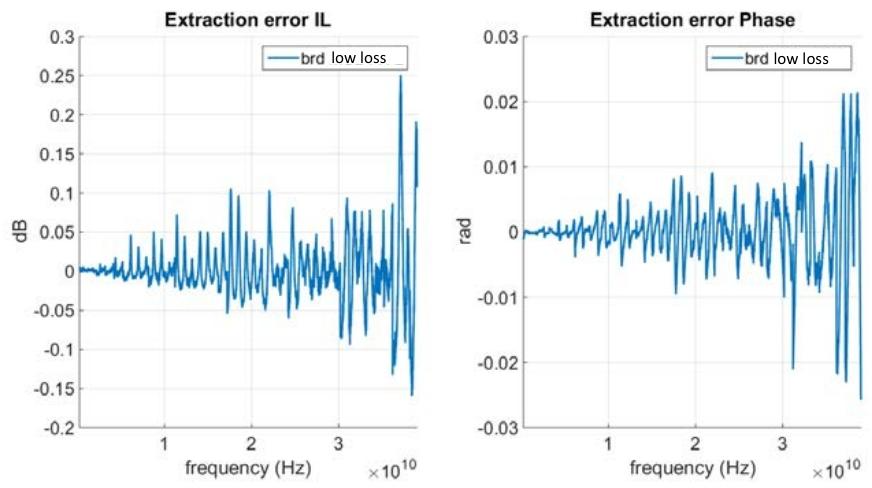

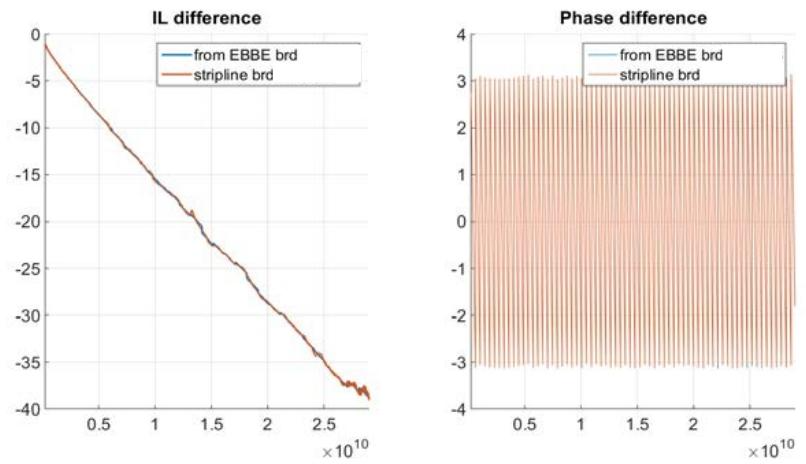

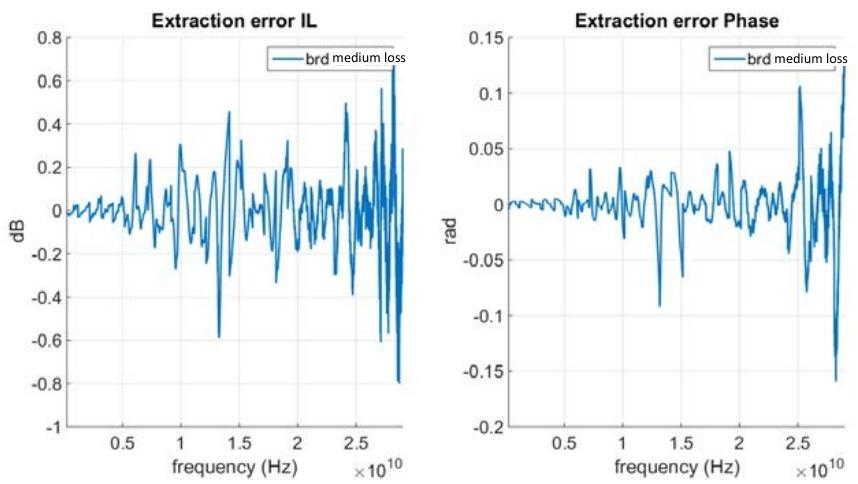

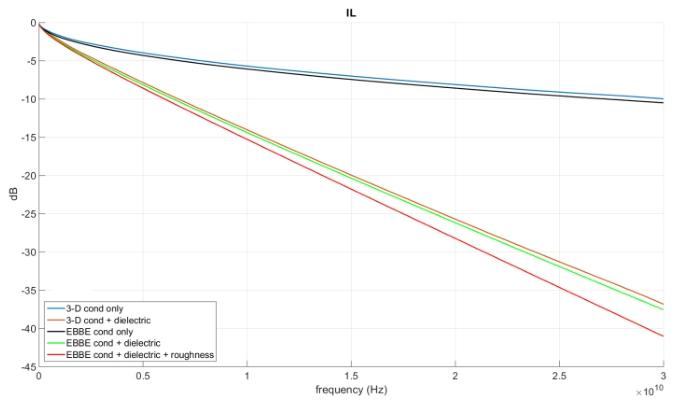

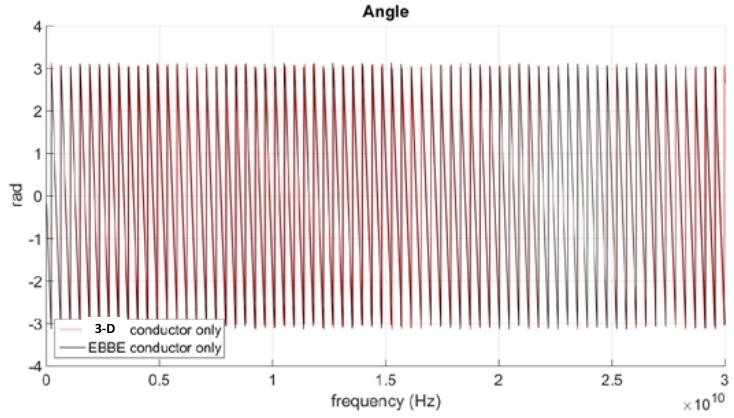

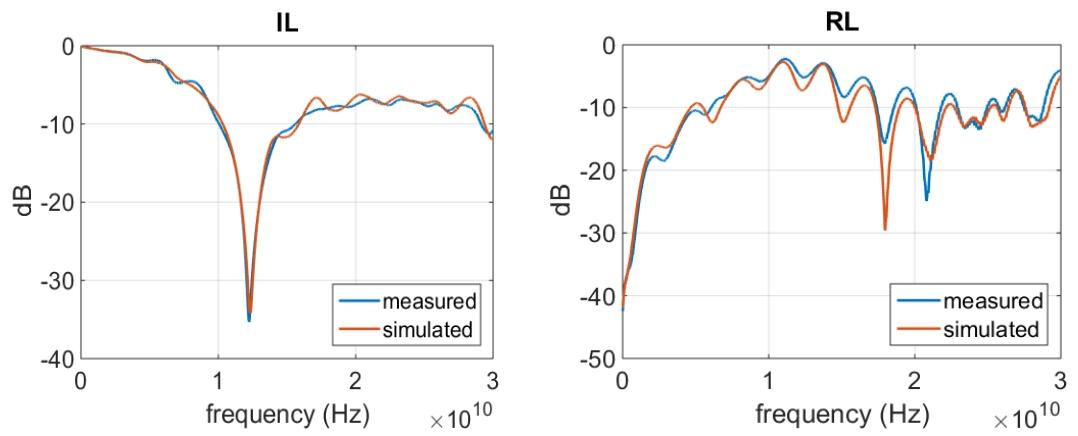

由于本文未介绍和展示EBBE提取算法,因此在图3至图6中呈现了与去嵌入带状线结构的比较。这些带状线位于PCB上EBBE提取结构的附近。进行这种相关性分析是为了让读者对提取值更有信心。图16中还展示了与三维求解器的相关性。

图3:低损耗材料在不同频率(Hz)下的插入损耗(IL,单位dB)和角度(单位rad)差异

图4:低损耗材料的提取误差

图5:中损耗材料在不同频率(Hz)下的插入损耗(IL,单位dB)和角度(单位rad)差异

图6:中损耗材料的提取误差

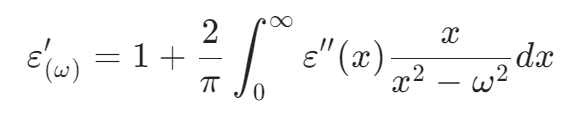

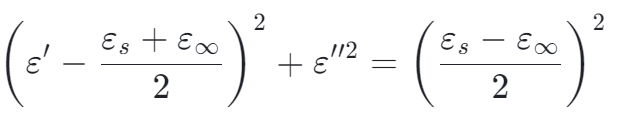

其中,ε'是复介电常数ε*的实部,ε''是其虚部。

复介电常数

普通材料对外场的响应通常取决于场的频率。这种频率依赖性反映了材料的极化不会对外加场做出瞬时响应这一事实。响应必须始终是因果性的(在外加场之后产生),这可以通过相位差来表示。因此,介电常数通常被视为外加场角频率ω的复函数。

因果复介电常数必须遵守克拉默斯-克勒尼希关系(Kramers-Kronig relations):

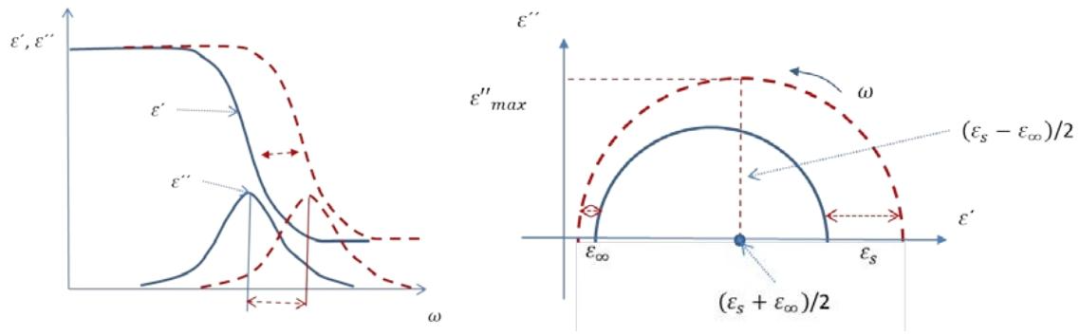

下面分析经验数据的一种方法是研究阿冈图(Argand plot,也称为科尔-科尔图)以及tanδ、ε'和ε''的对数图。

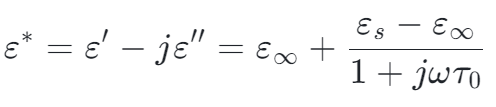

德拜模型(Debye)

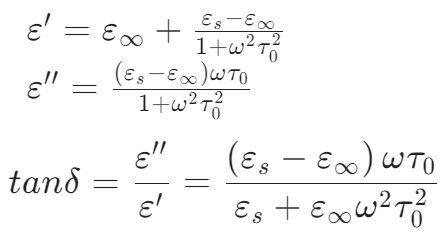

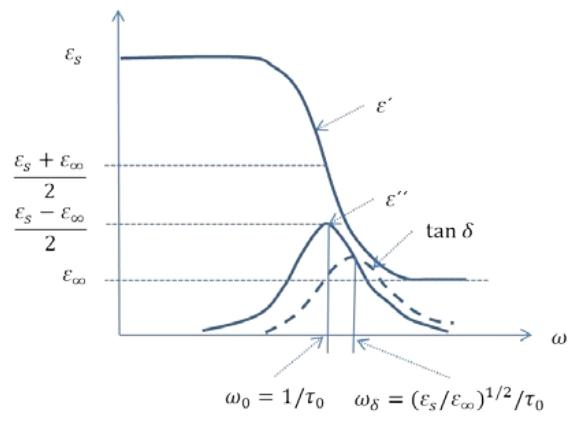

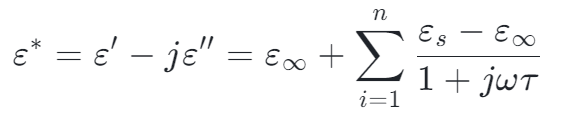

以下方程通常被称为动态极化的德拜方程,仅包含一个弛豫时间。在无限频率极限下,复介电常数的实部通常称为ε∞,在直流(DC)下称为εs。τ为弛豫时间。

并且:

这些方程基于衰减函数为指数函数的假设。

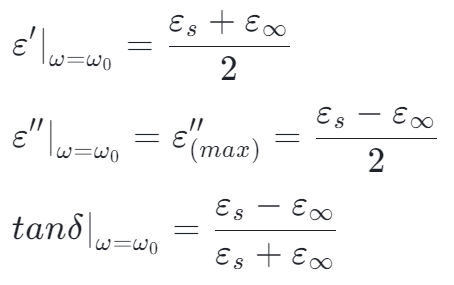

通过令dε''/dω=0和d(tanδ)/dω=0,可以找到ε'、ε''和tanδ达到最大值时的频率。

ε''的最大值出现在ω₀τ₀=1时。

在该频率下,ε'、ε''和tanδ分别为:

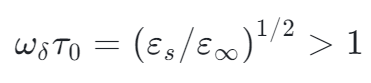

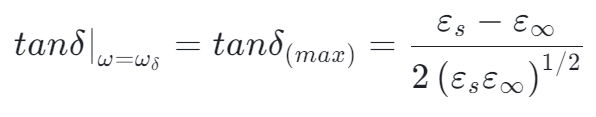

然而,ω₀处的tanδ值并非最大值。tanδ的最大值出现在ωδ处,此时:

在该频率下,tanδ为:

ε'、ε''和tanδ作为ω的函数如图7所示。

图7:德拜模型的对数图

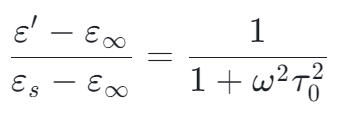

这两个方程给出了ε'-ε''平面上的圆方程,消去其中的ωτ₀可得:

只有ε''为正的半圆具有物理意义,如图8所示。

图8:德拜模型的阿冈图

为了考虑多个弛豫时间,可以将方程扩展为包含多个极点,即多极德拜模型:

无极模型(Infinite Pole Model)

由于宽带复介电常数测量难以实现,因此开发了一种方法,从供应商提供的数据表中的单个数据点计算复介电常数的频率依赖性。数据表通常列出1GHz和10GHz下的介电常数(ε')和损耗角正切(tanδ)。

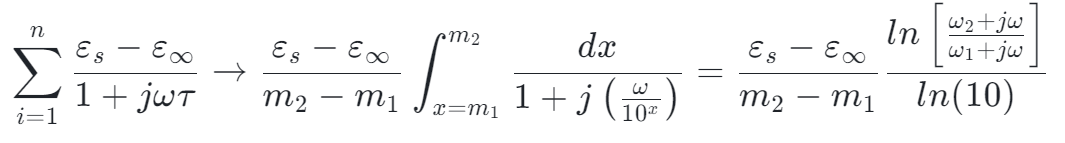

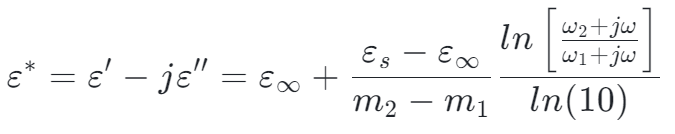

Djordjevic等人通过增加项数并假设1/τ₀在对数尺度上线性减小,简化了公式(Eq 16)。假设εs-ε∞的变化是感兴趣的较低频率ω₁=10^m¹和较高频率ω₂=10^m²之间ε'的总变化。

当项数趋于无穷时,公式(Eq 16)中的求和变为:

因此:

科尔-科尔模型(Cole-Cole)

基于单一弛豫时间的德拜方程不足以描述大多数电介质材料(如聚合物)的弛豫现象。在这种情况下,需要弛豫时间分布来解释实验数据,多极德拜模型就是如此。

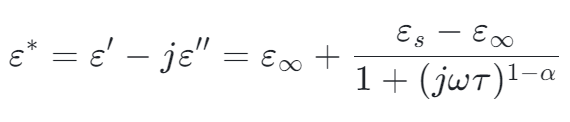

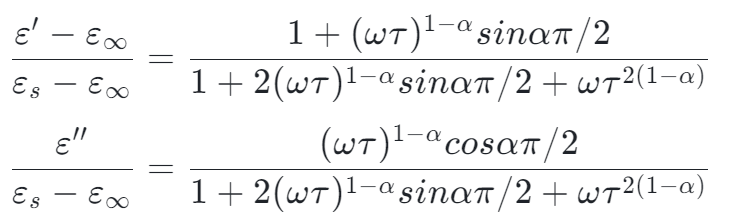

考虑弛豫时间分布影响的另一种方法是使用Cole和Cole提出的经验关系式:

其中,0<α<1,当α=0时为德拜弛豫。

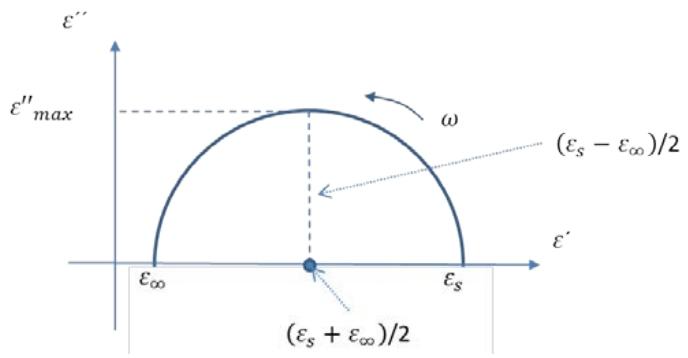

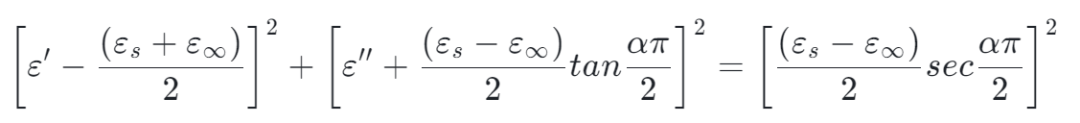

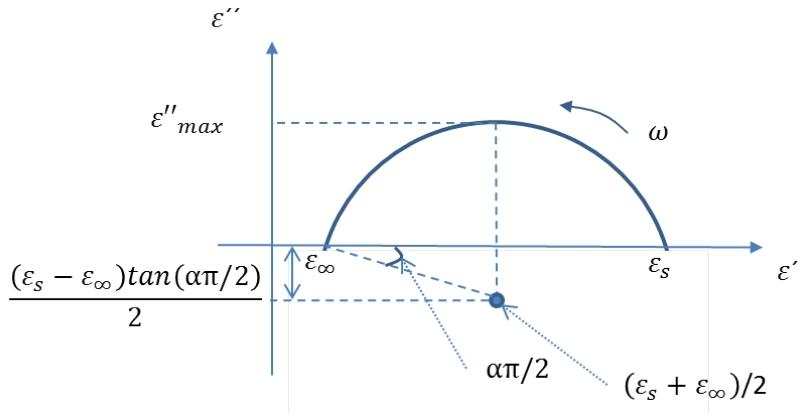

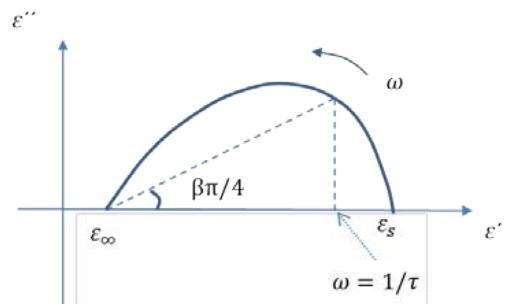

为了确定阿冈图(科尔-科尔图)的几何解释,公式可写为:

当α>0时,色散曲线比单一弛豫时间的曲线更宽,但仍关于ωτ=1对称。

通过令dε''/dω=0,可以证明最大损耗也出现在ωτ=1处。消去公式(Eq 20)和(Eq 21)中的ωτ,得到:

该方程表示一个圆,其圆心为[(εs+ε∞)/2, -(εs-ε∞)/2 tan(απ/2)],半径为[(εs-ε∞)/2 cos(απ/2)],如图9所示。

图9:科尔-科尔模型的阿冈图

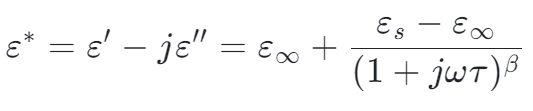

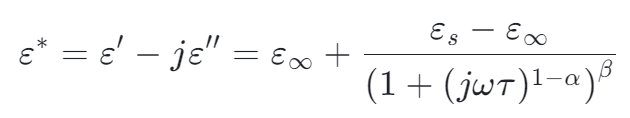

该方程用于电介质损耗峰呈现非对称展宽的情况,如图10所示:

其中,0<β<1。

图10:科尔-戴维森模型的阿冈图

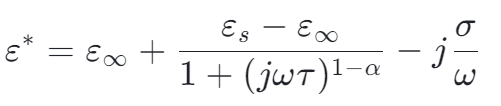

哈夫利利亚克-内加米模型是德拜弛豫模型的经验修正,考虑了电介质色散曲线的非对称性和宽度:

其中,0<α<1且0<β<1。

图11:哈夫利利亚克-内加米模型的阿冈图

-

当β=1时,哈夫利利亚克-内加米方程简化为科尔-科尔方程

-

当α=0时,哈夫利利亚克-内加米方程简化为科尔-戴维森方程

-

当β=1且α=0时,哈夫利利亚克-内加米方程简化为德拜方程

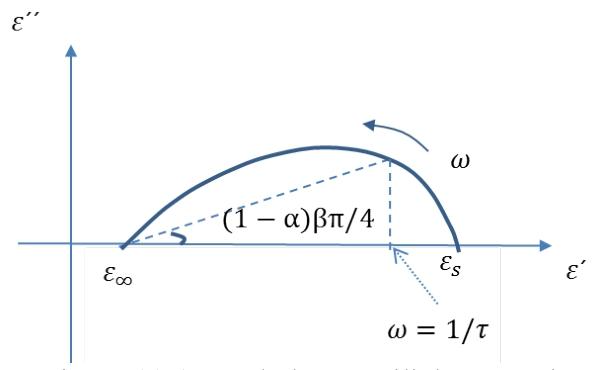

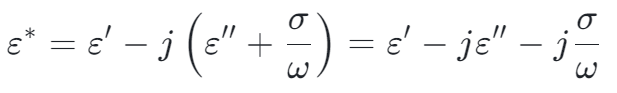

直流电导率(DC conductivity)

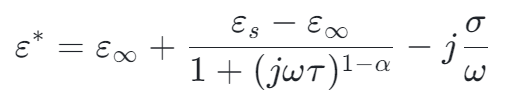

如果直流电导率不可忽略,则σ将对复介电常数的虚部产生影响。此时,总复介电常数变为:

包含直流电导率的科尔-科尔模型则变为:

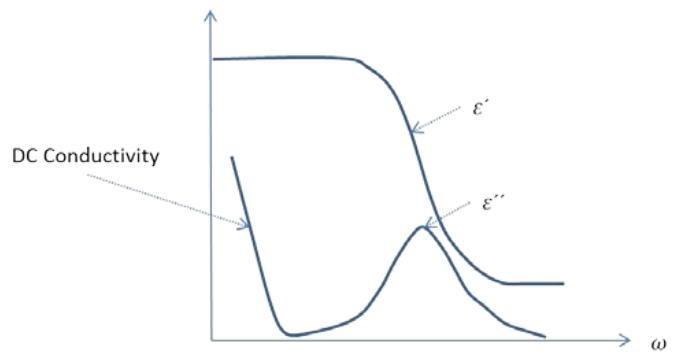

图12:包含直流电导率的阿冈图

图13:直流电导率的对数图

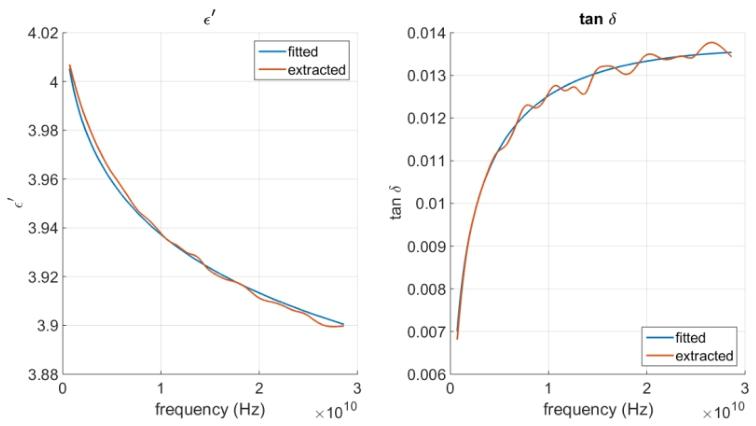

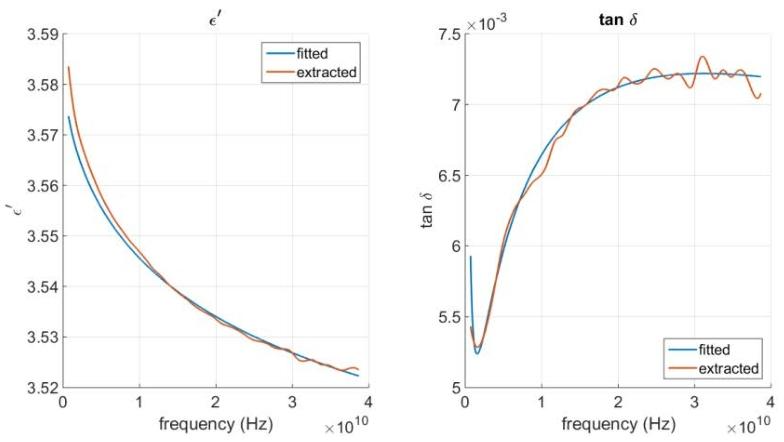

将提取的复介电常数拟合到多种不同的弛豫模型中,并记录拟合误差(拟合优度),从而选择拟合误差较低的模型,如表1所示。

图14:中损耗材料包含电导率项的科尔-科尔拟合

图15:低损耗材料包含电导率项的科尔-科尔拟合

图14和图15中,将包含直流电导率项的拟合科尔-科尔模型与EBBE提取的中损耗和低损耗材料的原始数据进行了比较。

注:在当前搜索算法下,β的不同初始值(0或1)会产生不同的拟合优度(GOF)值。

从表1可以得出结论,包含直流电导率项的科尔-科尔弛豫模型似乎是最合适的弛豫模型。哈夫利利亚克-内加米模型给出了总体最低的拟合误差,因为它更灵活,并且可以退化为科尔-科尔模型,但可能需要另一种搜索算法以实现更好的收敛性。哈夫利利亚克-内加米模型的额外灵活性也增加了过拟合的可能性。

仿真软件

将提取的复介电常数拟合到科尔-科尔模型后,就可以生成表格形式的数据,用于的一些信号完整性(SI)工具。

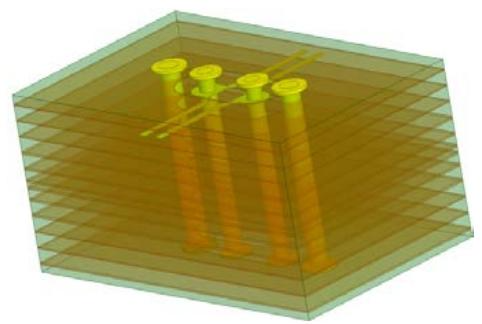

通过微观切片建模得到的几何结构,以及从中损耗材料的科尔-科尔拟合中得到的复介电常数表格值,被输入到三维求解器中。

然后,将三维求解器生成的S参数与EBBE生成的S参数进行比较------EBBE生成的S参数采用了中损耗材料的科尔-科尔拟合,以及从同一条35厘米长的带状线走线中提取的导体损耗。

粗糙度效应来自提取和拟合的RTF箔。的一些仿真软件还能够使用表格形式的粗糙度修正因子。

在传导损耗方面观察到非常小的偏差(将tanδ设置为非常低的值),这表明EBBE提取的传导损耗是正确的。在介电损耗和传导损耗的组合方面也观察到非常小的偏差。

图16:三维求解器的插入损耗比较

图17:三维求解器的角度比较

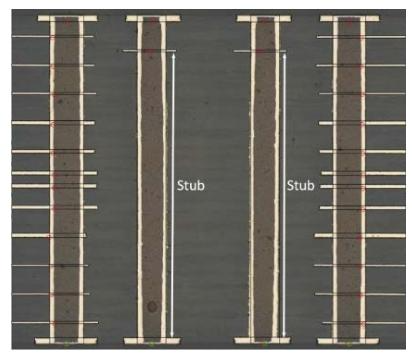

介电常数

图18:横截面图

采用Moore-Neighbor跟踪算法并在Matlab中实现,从过孔横截面图片中识别和测量过孔焊盘和焊筒的边界,如图18所示。

图19:根据提取的几何结构自动生成的三维模型

图20:过孔比较,测量值与仿真值

-

仿真的陷波频率始终高于测量的陷波频率,平均陷波频率偏差约为240MHz。

-

偏差随着反焊盘空隙尺寸的减小而增大。

为了更深入地了解偏差的来源,调整了多个参数,试图使仿真和测量的差分插入损耗陷波频率达到更好的一致性。选择反焊盘空隙正常、陷波频率偏差为360MHz的长 stub 过孔测试案例进行分析。

调整的参数及其对应的陷波频率偏移总结在表2中。目前,尚无法确定偏差来自以下哪种效应、多种效应的组合,或其他未考虑到的效应。

|------------------------|-------------------------------------|

| 调整参数(Tuned parameter) | 陷波频率偏移(Notch frequency shift (MHz)) |

| 介电常数增加5% | -250 |

| 阻焊层介电常数增加28% | -100 |

| 电源层与接地层之间电介质的介电常数降低10% | 180 |

| 铜平面周围的环氧树脂 | -40 |

| 反焊盘空隙偏移45um | -70 |

| 5%的尺寸误差 | -60 |

| 过孔焊筒添加粗糙度 | 90 |

温度影响

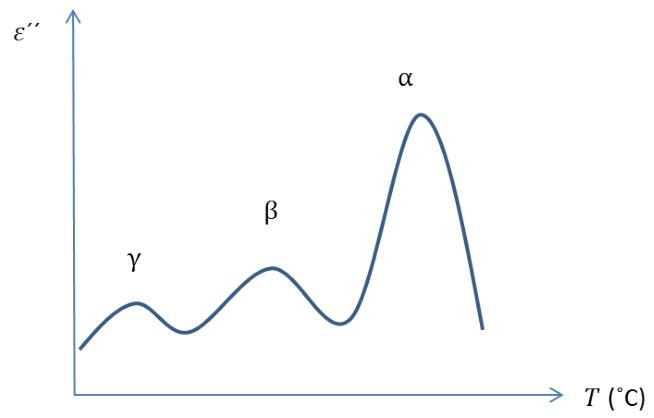

复介电常数是频率和环境效应(如温度)的复函数。在文献中,ε'和ε''的温度依赖性主要通过弛豫时间τ的温度依赖性体现(见图21a)。对于偶极分子,(εs-ε∞)也具有温度依赖性(见图21b)。

图21:a)温度影响的对数图;b)温度影响的阿冈图

图22:α、β、γ弛豫

-

偶极段弛豫(dipolar segmental relaxation)

-

偶极基团弛豫(dipolar group relaxation)

这两种类型的电介质弛豫在ε''的温度或频率依赖性曲线上表现出损耗峰。ε''或tanδ的最强峰出现在从玻璃态到橡胶态(高弹性态)的转变区域,即接近玻璃化转变温度Tg。

随着温度升高,各种类型分子的迁移率逐渐增强,使得偶极取向更容易发生。通常,电介质弛豫过程从高温端开始依次标记为α、β、γ等,如图22所示。

偶极段弛豫对应于α弛豫,偶极基团弛豫过程对应于β、γ弛豫。

温度对高损耗材料的影响

前面章节中选择的科尔-科尔模型用于寻找未知变量,以创建跨温度的拟合。图中省略了拟合的直流电导率损耗。

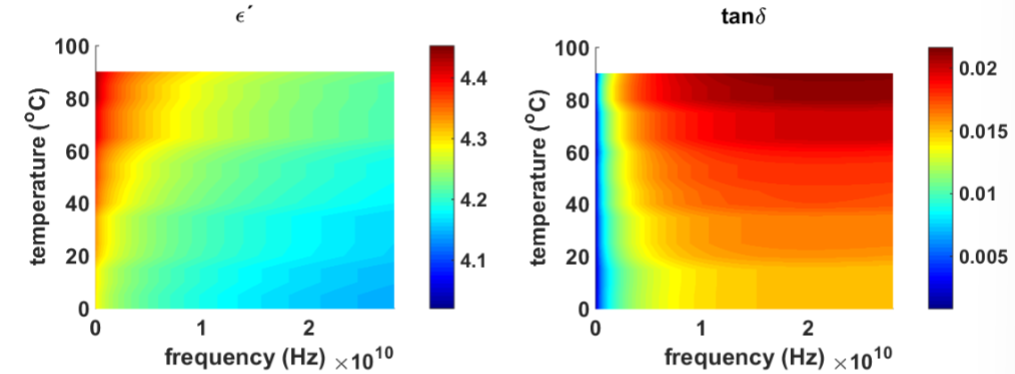

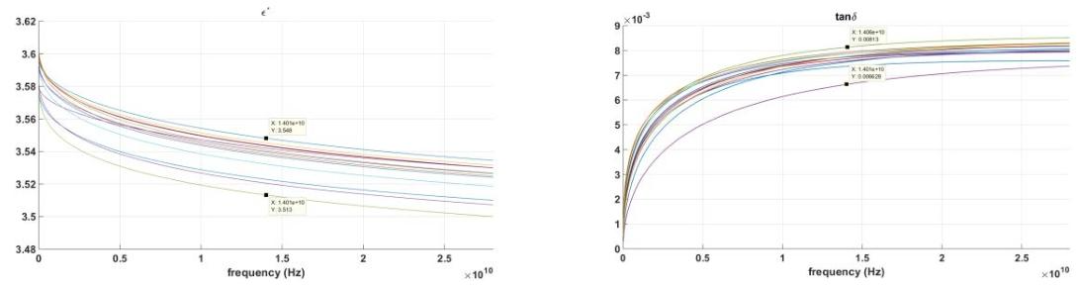

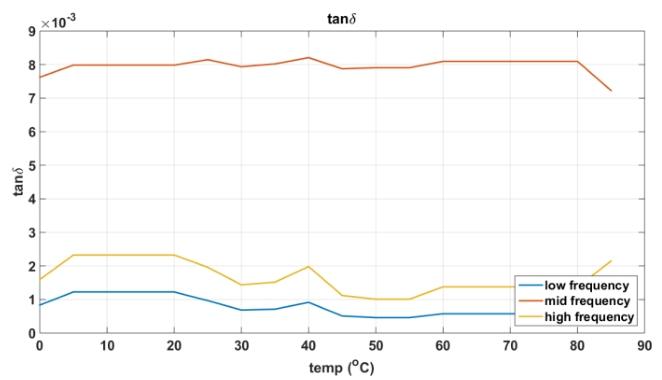

对于在0°C至90°C之间测量的高损耗材料,其tanδ和ε'随温度的变化如图23和图24所示。

图23:高损耗材料的ε'和tanδ随温度的变化

图24:高损耗材料的ε'和tanδ随温度的变化

从图23可以看出,ε'从0°C到90°C仅有适度增加:在1GHz时增加3%,在14GHz时增加2%。然而,tanδ在相同温度范围内有非常大的增加:在1GHz时增加58%,在14GHz时增加44%。

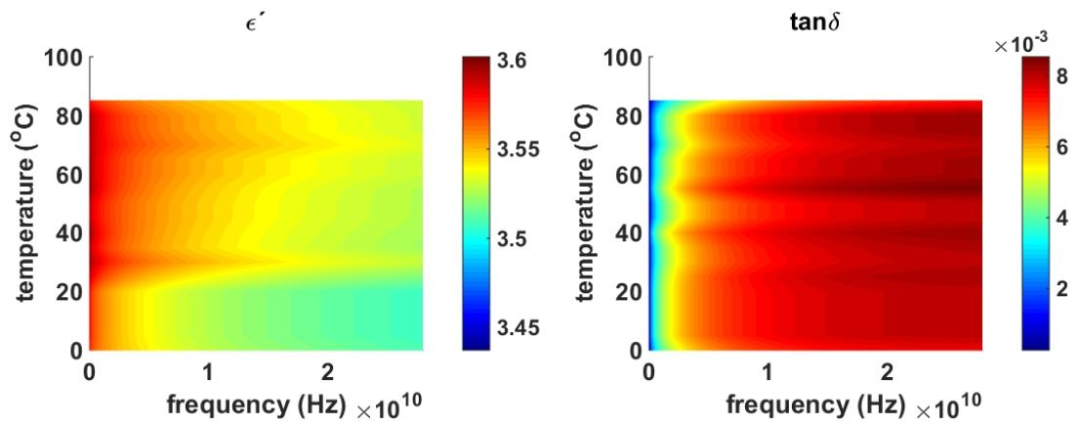

图25:高损耗材料提取的科尔-科尔参数

\varepsilon \Delta=\varepsilon_{s}-\varepsilon_{\infty}

从图25中观察到:

-

ε∞表现出几乎平坦的特性;

-

εΔ(即εs-ε∞)有所增加,因此εs是主要贡献者;

-

α和τ也呈现出一定的趋势。

正如在图21中指出的,除了τ和εΔ的变化外,根据这些发现,ε∞也具有温度依赖性。

从导出的变量中,还可以外推到非常高的频率,以进一步研究和理解材料在不同温度下的行为。

(注:高损耗材料在加热室中进行VNA测量的连接存在较多噪声,当外推到非常高的频率时,可能会影响变量和分析结果。)

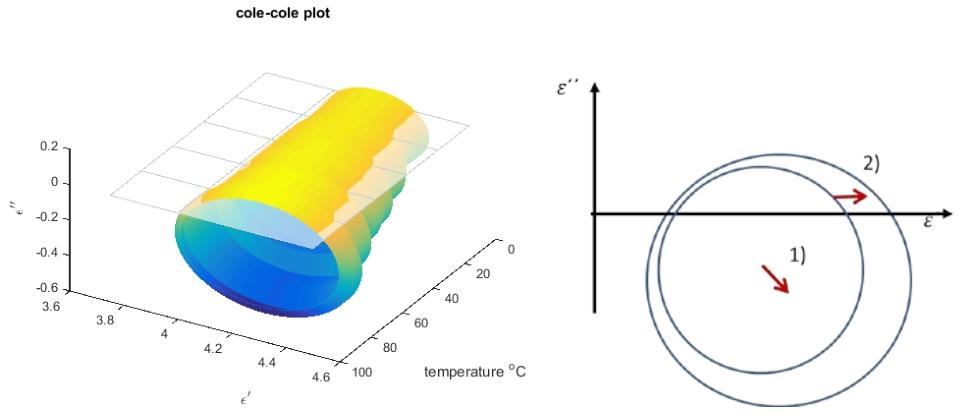

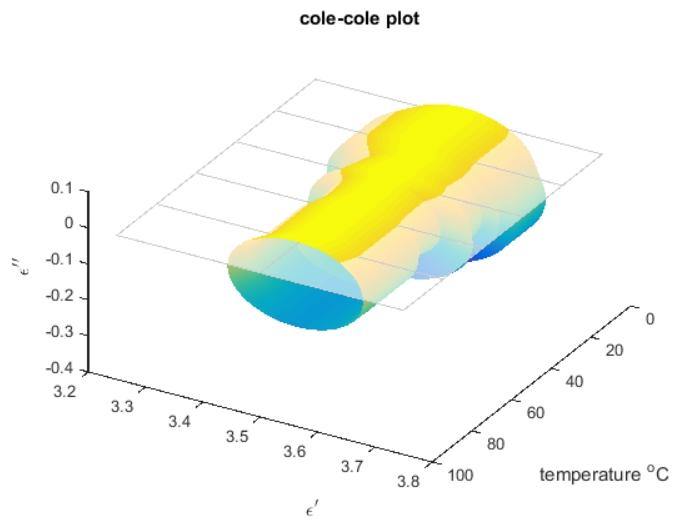

从不同温度下的阿冈图可以看出:

-

圆心沿右下方向移动;

-

εs增加(ε∞仅有微小偏移)。

图26:高损耗材料不同温度下的阿冈图

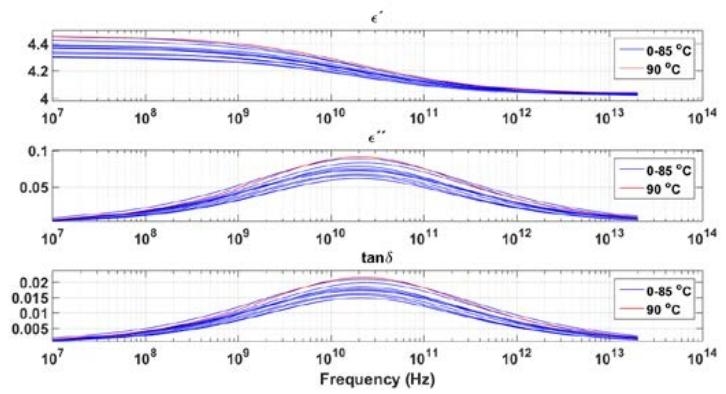

图27:高损耗材料不同温度下的对数图

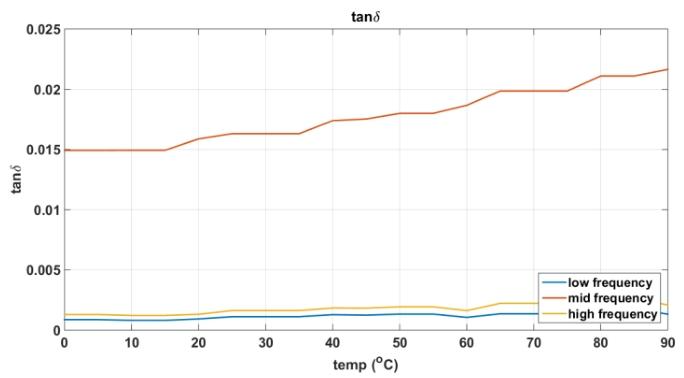

图28:高损耗材料在低、中、高频率下的tanδ随温度的变化

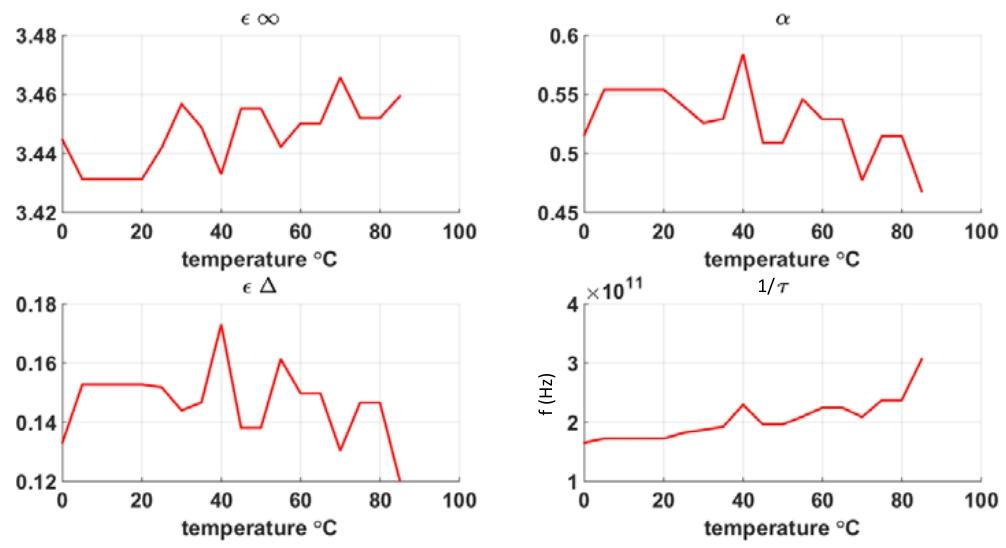

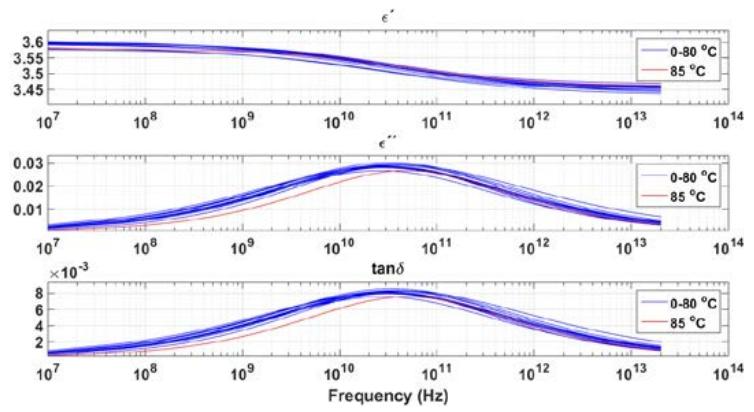

温度对低损耗材料的影响

图29:低损耗材料的ε'和tanδ

图30:低损耗材料的ε'和tanδ

图31:低损耗材料的科尔-科尔变量

图32:低损耗材料不同温度下的对数图

在85°C时,1/τ向高频偏移,这使得在感兴趣的频率范围内tanδ降低。图32中最低的轨迹(红色)对应最高温度。因此,图21a中描述的特性在此处可见,并解释了为什么该材料在较高温度下的介电损耗会降低。

图33:低损耗材料不同温度下的阿冈图

图34:低损耗材料在低、中、高频率下的tanδ随温度的变化

模型、温度及其关系

图35:插入损耗的温度依赖性

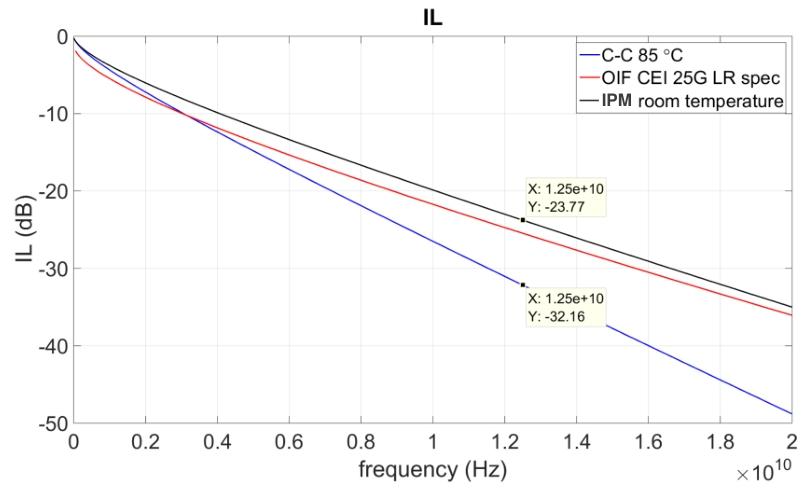

图35显示了高损耗材料的40厘米走线在两种情况下的插入损耗差异:一种是在室温下使用无极模型(IPM),另一种是在85°C下使用科尔-科尔模型(C-C)。

图36:插入损耗对比

因此,当使用介电损耗百分比较大的材料时,考虑介电常数的温度依赖性非常重要。

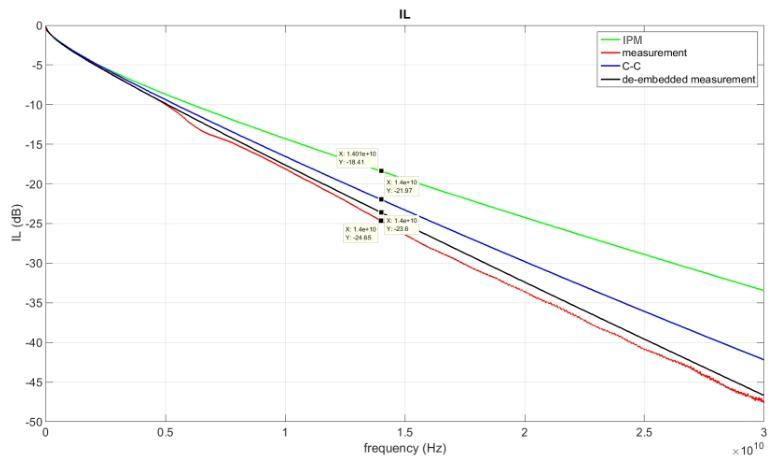

如果走线模型使用无极模型描述复介电常数,并且与未去嵌入的测量结果进行比较,通常会将差值归因于粗糙度效应。

在这种情况下,图36中的绿色轨迹(14GHz时为-18.41dB)不考虑粗糙度效应并使用无极模型,与未正确去嵌入的测量轨迹(红色,14GHz时为-24.65dB)进行比较。因此,差值为6.24dB,对应于这条40厘米走线的15.6dB/m。这可能归因于粗糙度。

图37:表面粗糙度的高估

使用无极模型和科尔-科尔模型之间的插入损耗差异为3.6dB,即9dB/m。

图37中对高估情况进行了评估。图37中的绿色轨迹不考虑粗糙度效应并使用无极模型。将图2中的粗糙度修正因子重新缩放,直到与测量轨迹(红色)"达到合理拟合"。从图37可以看出,为了弥补插入损耗偏差,KSR必须大幅增加,从20GHz时的1.25增加到1.9。

结论

环境效应(如温度和湿度)是进行可靠的时域和频域仿真时需要考虑的重要因素。

关于复介电常数,选择科尔-科尔模型是因为它对分析的材料具有良好的拟合效果。包含直流电导率的弛豫模型如下:

研究变量和图表中由温度等因素引起的增量变化,也能更深入地理解电介质材料的特性。

Ref:【Decompositional analysis of copper roughness effect and complex permittivity】

往期推荐

FCBGA芯片封装中的高密度高速SerDes信号完整性设计研究

56+Gbps SerDes高速接口应用的信号完整性设计解析

DDR接口Write/Read burst转换期间的信号完整性分析

以太网信号的电路建模及其在电磁兼容性与信号完整性分析中的应用

UCIE/HBM高速信号2-μm-Pitch RDL Interposer信号完整性分析

128 Gbps PCIe 7.0通道中布线区域和过孔残桩的信号完整性考量