关于信号翻转模块(sig_flag_mod)的实现

语言 :Verilg HDL 、VHDL

EDA工具:ISE、Vivado、Quartus II

-

关键词: Verilog HDL,ifdef 和 endif ,generate语句

一、引言

本文使用FPGA实现环形振荡器,达成信号翻转的作用。

二、实现信号翻转模块的方法

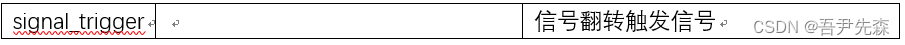

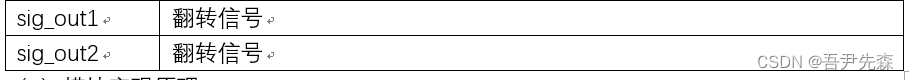

(1)输入接口

(2)输出接口

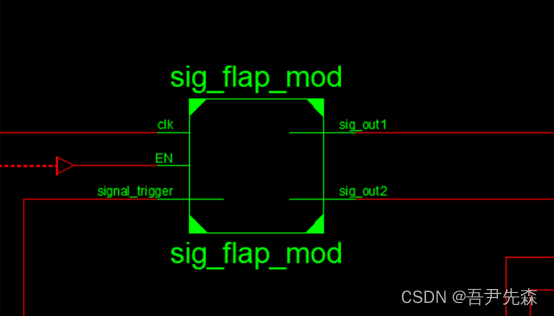

(3)模块实现原理

环形振荡器,是由奇数个非门输出端和输入端首尾相接,构成环状的电路。在环形振荡器原理图中,假设第一级反相器的输入端为低电平,经过5级反相之后,第5级反相器输出端必为高电平。在t=0时刻,此时电源(VDD)通过第5级反相器输出端对第1级反相器的输入电容充电,第一级反相器经过一级平均延迟时间Tdelay1之后,其输出状态发生转换。经过(Tdelay1+ Tdelay2+ Tdelay3+ Tdelay4+ Tdelay5)之后,第5级反相器输出端由高电平转换为低电平。接着第一级的输入电容将通过第5级的输出端放电,经过(Tdelay1+ Tdelay2+ Tdelay3+ Tdelay4+ Tdelay5)之后状态再次发生转换,完成一个振荡周期输出。本模块中实现了121级反相器的翻转。

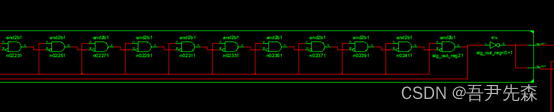

(4) 模块实现原理图

如下图所示是模块实现原理图和原理图细节图

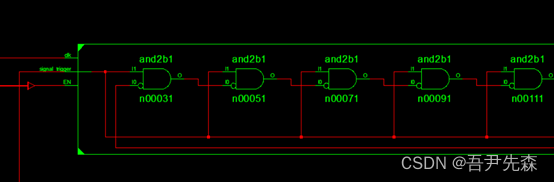

(5) 代码

bash

module sig_flap_mod(

input clk ,

input EN,

input signal_trigger,

output sig_out1 ,

output sig_out2

);

localparam NUM =120 ;

(* DONT_TOUCH = "yes" *) wire[NUM:0] sig_out_reg ;

(* DONT_TOUCH = "yes" *) wire sig_out_reg2 ;

assign sig_out1 = sig_out_reg[0];

assign sig_out2 = sig_out_reg[0];

and u1( sig_out_reg2 , sig_out_reg [NUM], signal_trigger );

not u2 (sig_out_reg [0] , sig_out_reg2 ) ;

generate

genvar i;

for ( i=0;i<NUM;i=i+1 )

begin:inst

not u3 (sig_out_reg[i+1] , sig_out_reg[i] ) ;

end

endgenerate endmodule