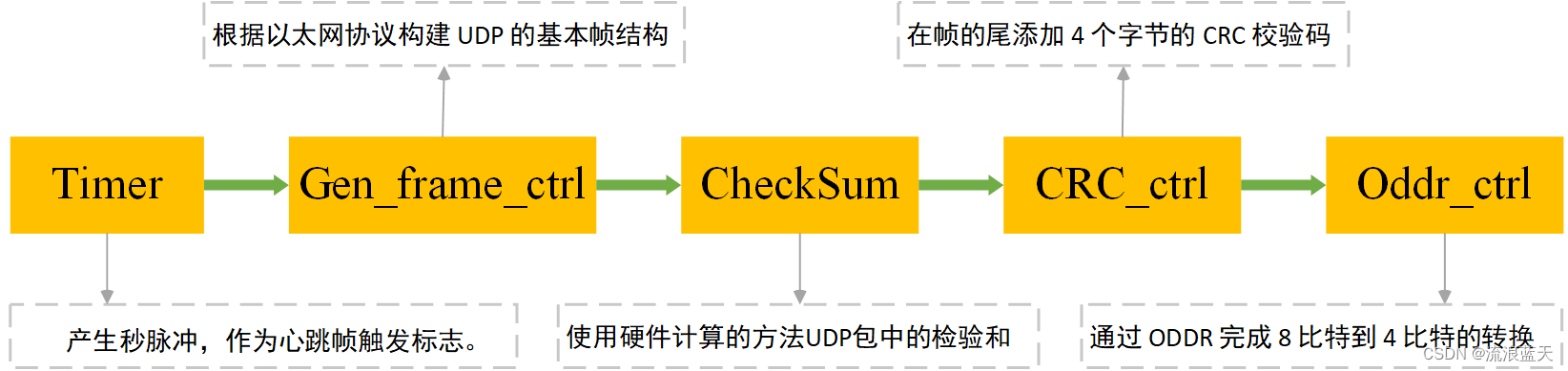

我们设计的以太网整个发送链路如下图所示,在千兆以太网数据发送(一):心跳帧的组建中已经实现了timer模块和gen_frame_ctrl模块,得到UDP的基本帧结构,但是检验和、CRC等字段都给的0。本文将在此基础上计算出IP检验和以及UDP校验和,进一步完善以太网数据包。

以太网发送链路

以太网发送链路

一、IP校验和计算方式

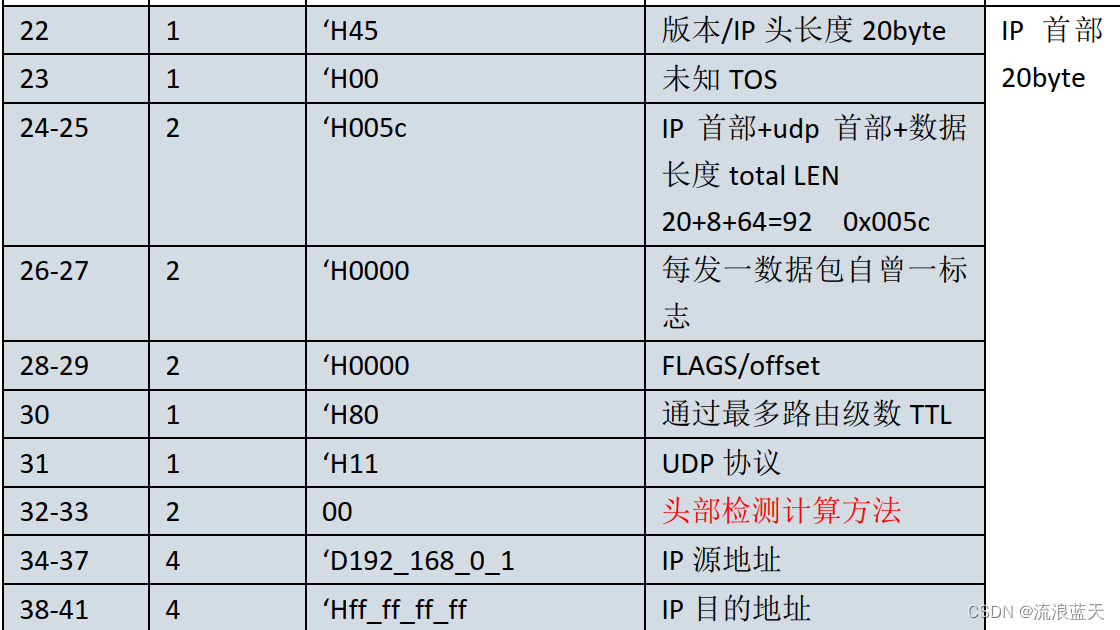

以太网帧结构中需要进行IP校验的字段范围如下图。IP校验和的计算是将IP首部的20字节按照2字节进行分割,然后逐个相加。如果相加结果超过16'hffff,就把超出部分与低16位再次相加,直到最终结果小于16位的最大值为止。最后,将最终小于16位的结果取反作为IP校验和。校验和的高字节在前,低字节在后,将之前填充在以太网协议中的0进行替换即可。

IP检验和范围

IP检验和范围

由上文可知,20字节按照2字节进行分割后得到10个16bit字段,现在我们考虑一种极限情况,假设10个字段都为最大值16'ffff,那么想加后的值等于9FFF6,地16bit和9相加等于FFFF,没有超过FFFF。因此,我们最多只需要判断一次相加结果是否大于16'hffff,再将超出部分与低16位相加即可。

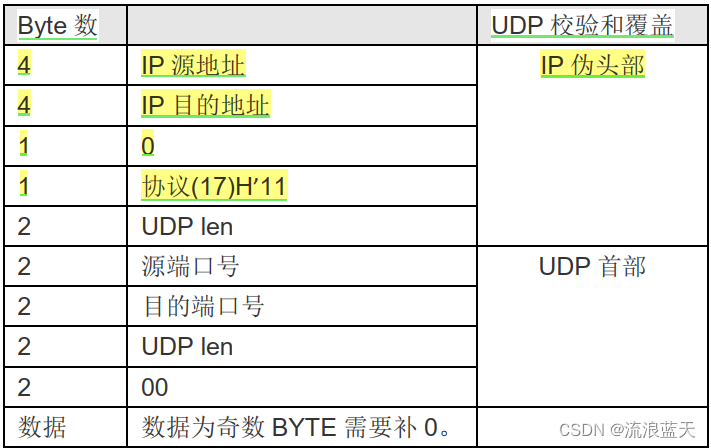

二、UDP校验和计算方式

以太网帧结构中需要进行UDP校验的字段范围如下图。UDP校验和的计算方式与IP校验和计算方式类似,特殊的是还需要加上IP伪首部,将IP伪首部、UDP 首部的 8 个 bytes 和数据按照2字节进行分割,然后逐个相加。

UDP检验和范围

UDP检验和范围

由于本次构建的是心跳帧,数据部分都为16'h0000,因此即使在每个字段都取最大值16'hffff时,同样只需要判断一次相加结果是否大于16'hffff,再将超出部分与低16位相加。

三、模块实现

思路:模块输入的信号分为两路,一路存入ram中,一路进行IP check和UDP Check。当校验和计算完成后,开始从ram中读出数据,当读取到检验和位置时,用计算得到的校验值替换读出的值。

具体实现中,当校验和计算完成后拉高ram读使能信号,读出113个数据后拉低。ram读出的数据会延后使能信号一拍,再加上寄存器寄存一拍(实现对应校验和位置替换),所以本模块输出的数据有效信号check_en将延后ram读使能信号两拍。部分代码如下:

cpp

//rd_ram_en

always @(posedge sclk) begin

if (rst == 1'b1) begin

rd_ram_en <= 1'b0;

end

else if (rd_ram_addr == 'd113 && rd_ram_en == 1'b1) begin

rd_ram_en <= 1'b0;

end

else if (tx_end_flag == 1'b1) begin

rd_ram_en <= 1'b1;

end

end

//check_data

always @(posedge sclk) begin

if (rst == 1'b1) begin

check_data <= 'd0;

end

else if (rd_ram_addr == 'd33 && rd_ram_en == 1'b1) begin

check_data <= ip_check_sum[15:8];

end

else if (rd_ram_addr == 'd34 && rd_ram_en == 1'b1) begin

check_data <= ip_check_sum[7:0];

end

else if (rd_ram_addr == 'd49 && rd_ram_en == 1'b1) begin

check_data <= udp_check_sum[15:8];

end

else if (rd_ram_addr == 'd50 && rd_ram_en == 1'b1) begin

check_data <= udp_check_sum[7:0];

end

else begin

check_data <= rd_ram_data;

end

end四、仿真测试

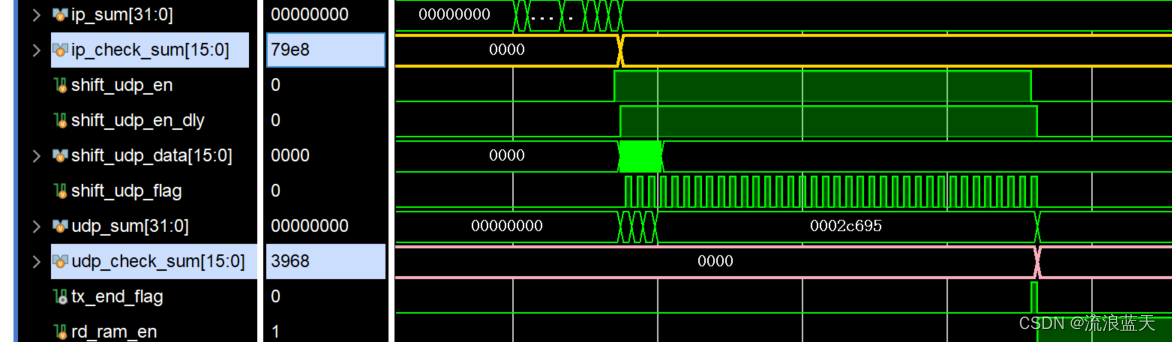

在仿真波形中可以看到IP校验和为16'h79e8,UDP校验和为16'h3968,与手算结果一致。

仿真波形1

仿真波形1

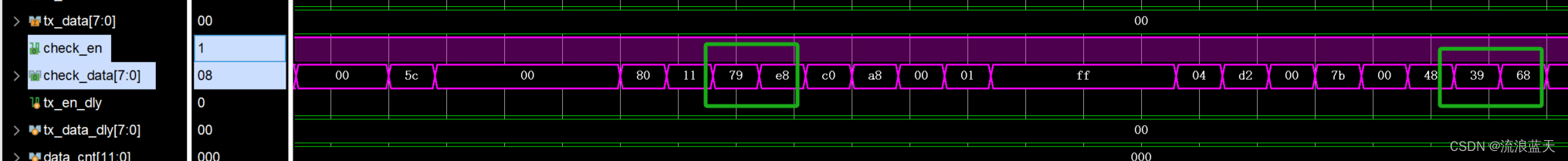

再观察最终模块输出的check_en和check_data[7:0]信号,可以看到对应校验和的位置已经被填充上计算出的值。

仿真波形1

仿真波形1