1 of N模式 SPI

概述

GIC-600AE支持1 of N模式SPI。在此模式下可以将SPI target到多个core,并且GIC-600AE可以选择哪些内核接收SPI。

GIC-600AE只向处于powered up 并且使能中断组的core发送SPI。

GIC-600AE会优先考虑那些被认为是active的核,但如果没有active的核,它就会选择inactive的核。

GIC600AE选择哪个core进行响应,受以下控制或影响:

1.cpu_active signal

cpu_active连接到gic redistributor用于指示每个core的状态。若cpu_active为低,表明该core处于low-power state,例如retention。当系统中没有合适的路由目标时,必须选择它作为SPI的目标

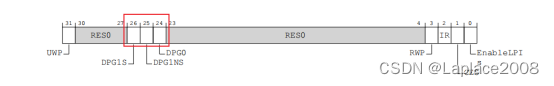

2.GICR_CTLR.DPGxx(Disable Processor Group)

设置DPGxx =1会阻止特定中断分组的1 of N模式的SPI路由到该core

3.Processor and GICD group enables and GICR_WAKER.ProcessorSleep

若以下任一条件为真,1 of N模式SPI中断不会路由到该core:

①通过GICR_WAKER.ProcessorSleep表明core处于休眠状态;

②中断分组被禁用

4.Interrupt class

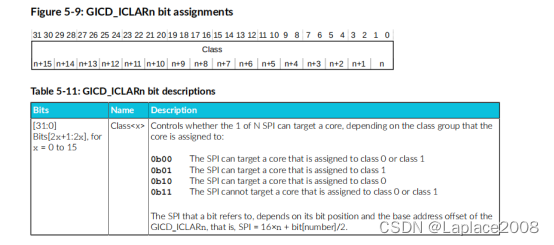

通过配置GICR_CLASSR可以将core分成class0或class1。1 of N模式的SPI中断通过配置GICD_ICLAR寄存器,可以将路由目标选择为class0,class1或both class。

在Arm big.LITTLE系统中,可以将所有big cores设置为class1,little cores设置为class0,1 of N模式的SPI中断可以根据处理量进行区分。

5.GICD_CTLR.E1NWF

该bit用于控制,当1 of N模式的SPI中断没有恰当的路由目标时,是否通过GIC唤醒该core

配置流程

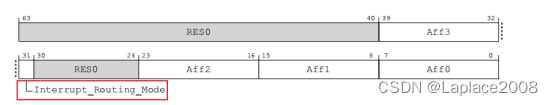

1.在配置产生SPI中断时,首先通过配置GICD_IROUTER.Interrupt_Routering_Mode将中断路由模式设置为1 of N模式

2.配置GICD_ICLARn寄存器将要产生的spi中断划分为class0,class1或both

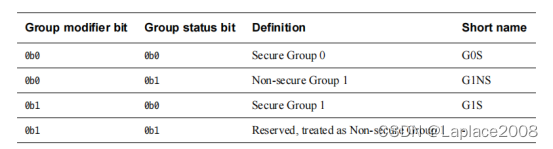

3.配置spi中断的分组(GICD_IGRPMODR和GICD_IGROUPR)

4.GICR_CLASSR

这个寄存器用于指定CPU接受哪一类的1 of N SPI中断

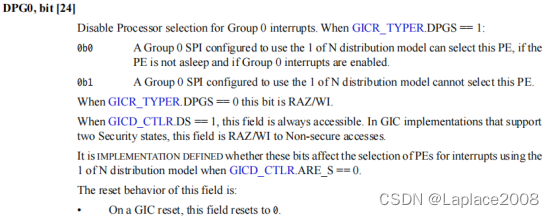

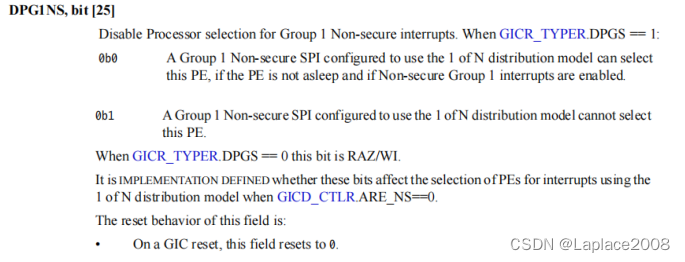

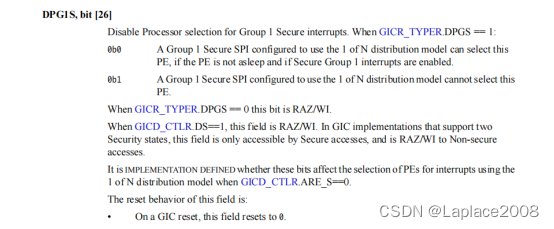

5.GICR_CTLR.DPGxx

如果配置DPG0=1,那么Group 0 的 1 of N 模式的SPI中断将无法作用到对应的cpu上

如果配置DPG1NS=1,那么Group 1 Non-Secure 的 1 of N 模式的SPI中断将无法作用到对应的cpu上

如果配置DPG1S =1,那么Group 1 Secure的 1 of N 模式的SPI中断将无法作用到对应的cpu上.

上述3bit最好都配置为0,这样PE就可以接收Group 0,Group 1 Non-Secure,Group 1 Secure的1 of N模式的spi中断