先说结论:

内容非常全面,讲解到位,会有专门的工程师一对一答疑,整个项目跑下来提升非常大,绝对物超所值!

一些细节:

本人微电子专业研一在读,有过两次简单的数字芯片流片经历,出于学习和科研需要,报了景芯的12nm A72 UPF DVFS后端实战。

整个项目基于innovus实现,主要包括芯片partition、maia_cpu的PR和MAIA顶层的PR三个阶段。在每个阶段PR结束之后,对maia_cpu ip核/MAIA顶层进行Calibre DRC, LVS检查,StarRC抽参,pt抽参,lc生成lib文件,使用xtop/pt进行timing eco修复setup/hold违例,LEC逻辑等价性检查,VCLP低功耗设计静态检查,voltus功耗和压降评估,redhawk功耗和IR Drop分析等等。个人觉得项目的设置真的非常全面,涵盖了芯片后端物理实现直到tapout的全流程,本人在跑这套后端flow的过程中也了解到很多非常实用的后端EDA工具和功耗/时序的分析/修复方法。

项目整体流程和部分文档

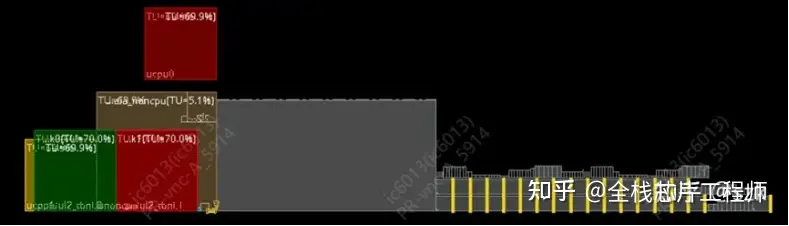

在partition阶段,进行初步的floorplan,划分电压域,并实现顶层的电源网络。如下图所示,整颗芯片包含两颗A72 cpu核,若干L2 $,一些常开模块和PMU模块等等。整颗芯片共划分了6个电压域。(顺便提一句,我觉得整个项目唯一美中不足的地方是顶层芯片没加PAD,景芯的另一个soc项目有加PAD的流程)

MAIA before partition

MAIA partition

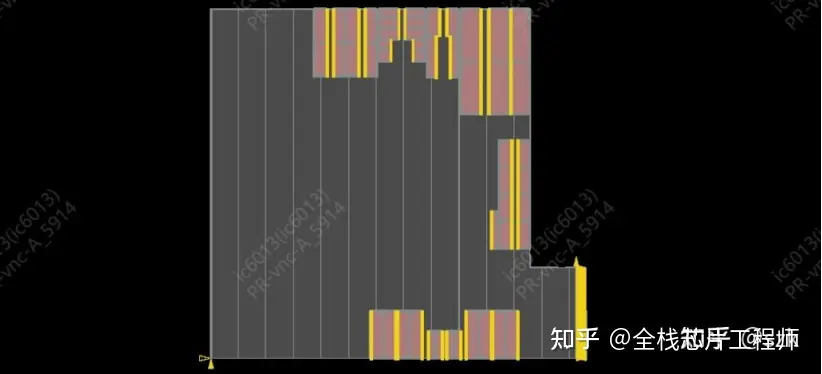

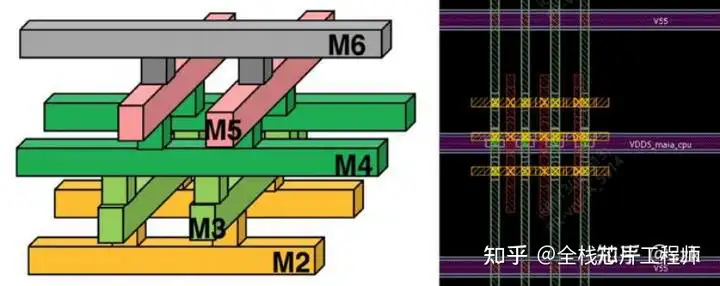

maia_cpu阶段实现单颗A72的PR,这部分流程就比较常规了,首先导入之前partition好的maia_cpu部分的def,随后进行单颗maia_cpu的floorplan、摆放powerswitch和各种tapcell, endcap、电源网络设计、摆放标准单元、时钟树综合、二级电源连线、信号布线、各种check和verify、release等。但是!让我眼前一亮的有两点,一个是12nm的电源网络的via pillar处理方式,另一个是ICG单元的特殊处理和整个时钟网络的balance,还是学到不少新东西的。

A72 maia_cpu floorplan

via pillar

overview of ICGs

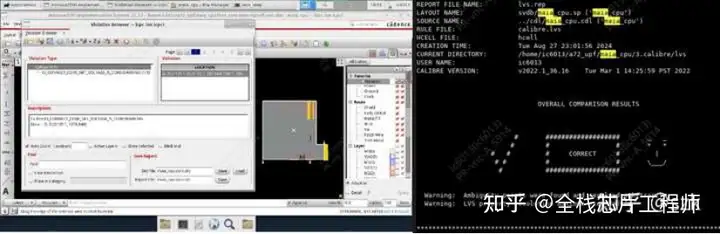

完成maia_cpu后,我先进行starRC、pt抽参,随后使用xtop优化setup和hold,并再次打开innovus使用xtop生成的脚本自动进行eco修复timing。确认时序没有违例后,使用Calibre进行DRC、LVS检查,不出所料有很多DRC违例,LVS不通过。但是!!!景芯的一对一辅导真的很靠谱,有几个较难的DRC和LVS问题,工程师会一步步帮忙找bug并进行eco,整个过程非常专业并且工程师真的非常非常有耐心。最后如愿DRC和LVS clean。

DRC/LVS results

对maia_cpu进行一系列LEC检查和功耗、压降检查后,就可以进行最后一步MAIA顶层的布局布线了。依次读入各种lib和lef文件、maia_cpu的def和partition阶段产生的MAIA顶层的def,随后与maia_cpu相同,进行floorplan、电源网络、时钟树综合等等,不再赘述。

MAIA after CTS

整体来说我觉得这个项目是非常完善的,DRC、LVS、时序、功耗、压降等各种检查都有涉及;同时项目也非常有难度,不仅芯片规模大,制程先进(12nm),还涉及很多UPF的相关内容。景芯视频和实践相结合的授课方式也非常有效,视频会大量讲解一些原理性的内容,比如MCMM、UPF的一些基本概念和环境配置、时钟树的基本理论和该项目的时钟树结构的设计方法、顶层模块的时序约束、POCV/SOCV时序报告解读等等,而上机实践的部分则需要自己动手跑脚本,发现bug并尝试解决,锻炼工程能力。此外,我觉得课程很贴心的一点是,上机实践的部分在关键步骤都准备了golden结果,如果当下bug不能立即解决可以先跳过,使用提供的golden先体验一下整个后端流程,回过头再来解决一些细节问题。跑完整个项目真的感觉收获满满,在理论和实践上都有很大提升,但是感觉依然有很多内容没有完全掌握,整个flow中的很多细节都没注意到,很多工具也只是马马虎虎跑了个脚本。

最后!我觉得最值的一点就是有专门的工程师全程答疑,工程师回消息特别快,解决方案也很细致,除了解决一些具体的bug之外,有时候还会讲解一些原理性的内容,分享一些工程经验等等,真的能学到很多除脚本之外的东西!非常推荐!

(另外: 我觉得A72 整体难度有点大,如果是新手的话建议先跑景芯的soc后端实践课,再来尝试A72的进阶课程)