在180度 B to B Connector 信号完整性仿真时,不会碰到端口设置不方便问题,但在做90度B to B Connector信号完整性仿真时就会碰到端口设置问题。如下面的90度B to B Connector。

公座

母座

公母对插后如下:

客户要求改Connector需符合PCI-E3.0的信号完整性要求,主要传输网络信号,差分阻抗中值是按100欧母设计的。这类连接器仿真基本上都是采用波端口激励。波端口都是设置在边界上,对上排端子设置端口,没有问题,如下:

对下排端子设置波端口就麻烦了,如果像下面设置,仿真结果就不正确,因为波端口设置在了内部。对这种连接器,设置端口可以使用线缆引出法去设置端口,即用线缆将Trace连接到边界,然后在线缆的端部设置波端口。下面讲下具体做法。

1 模型预处理

上面的图片中可以看出公母端子存在较大干涉,需要做处理,这里就简单处理一下,处理结果如下:

2 设计PCB(夹具)设计PCB时需做阻抗匹配,将Trace的差分阻抗设计在100+/-5欧姆以内。

3 设计连接线缆,线缆可以设计成矩形也可以设计成圆形,这里设计成矩形。设计的线缆同样也需要做阻抗匹配。

4 这里让线缆垂直穿过PCB与Trace相连,去除相交部分。

仿真夹具设计完成后如下:

5 将3D模型导入CST,设置端口,如下:

6 仿真及结果查看。

在介绍仿真结果之前,先介绍一下PCIE3.0信号完整性标准要求。下面是部分PCIE3.0信号完整性要求的截图:

下面看下仿真结果:

差分插入损耗(DDIL)

差分回波损耗(DDRL)

差分近端串扰(DDNEXT)

差分远端串扰(DDFEXT) 该项PCIE3.0没有要求

从上面·结果可以看出该产品设计时符合PCIE3.0信号完整性要求的。

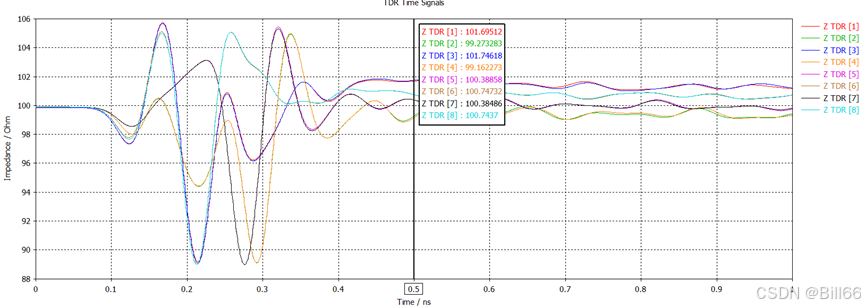

时域阻抗(TDR)

可以看出差分阻抗在100 +6/-12 欧以内。

本博文示例的原始3D 模型(stp格式),仿真模型(stp格式),仿真设置及结果(cst格式)以打包上传到CSDN,如需对照练习可去下载,下载链接为:https://download.csdn.net/download/billliu66/90162193