文章目录

- [第三节 半导体存储器与CPU的连接](#第三节 半导体存储器与CPU的连接)

-

- 一、存储芯片与CPU连接中应关注的问题

- 二、存储器扩展

-

- [1. 位扩展:](#1. 位扩展:)

- [2. 字扩展](#2. 字扩展)

- [3. 字位扩展](#3. 字位扩展)

- 三、实现片选控制的方法

-

- [1. 全译码法](#1. 全译码法)

- [2. 部分译码法](#2. 部分译码法)

- [3. 线选法](#3. 线选法)

第三节 半导体存储器与CPU的连接

一、存储芯片与CPU连接中应关注的问题

- CPU 的负载能力

外接芯片的数量、驱动器、缓冲器。 - 芯片的选择

考虑芯片的容量、总存储容量、时序匹配等。 - 时序配合

存储芯片的速度和CPU额读/写时序相匹配。 - 存储器的地址分配

RAM的用户取存放程序和数据,单芯片容量有限,多芯片组形成存储器需要考虑片选,地址分配。

二、存储器扩展

1. 位扩展:

多个芯片并联得到指定位宽的存储器。

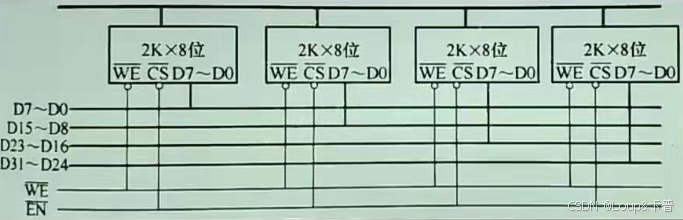

例:用 2Kx8 位的存储芯片组成 2Kx32 位存储体

32 / 8 = 4 片

地址线、控制线并联;

数据线从8位扩展到32位。

2. 字扩展

数据位数不变,子的数量扩展

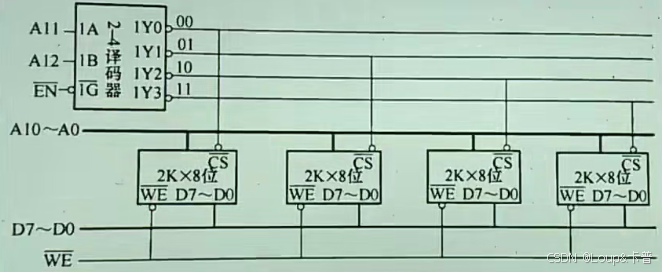

例 用2Kx8位的存储芯片组成8Kx8位存储体。

8k/2k = 4

8K = 13 根地址线

数据线、控制线和部分地址线并联、另一部分地址线通过译码器后形成片选信号来决定每个芯片的地址。

左边数第一个芯片的地址:0000H~7FFH

第一个的起始和结束地址

00 0000000000

00 11111111111

最后一个时

3. 字位扩展

数据位数和子的数量都需要扩展

如。用2Kx8位的存储芯片组成8kx16位存储体。

先将2个2Kx8位芯片用位扩展为2Kx16位的存储器,在将4个2Kx16位的存储器用字扩展为8Kx16位的存储器。

【例题】存储器扩展有哪几种方式?

3 种,字扩展、位扩展、字位扩展。

【解析】:字扩展:增加字的数量,地址范围; 位扩展:增加位数;字位扩展:位数和地址范围均增加。

三、实现片选控制的方法

存储体由多个芯片构成,由片选信号(由地址线实现)巨顶对哪个芯片进行读写操作。

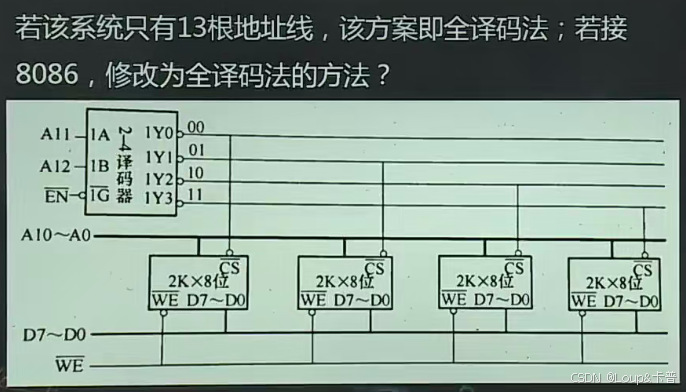

1. 全译码法

即系统的全部地址线参与到地址译码,高位全部接译码器的输入形成片选信号来选择存储芯片;低位直接接到存储芯片的地址引脚,选择芯片内部的存储单元。该方法存储芯片的每个存储单元有唯一的地址。

8086 有20位, A13-19没有参与。

2. 部分译码法

即地址高位的一部分接到译码器的输入,形成片选信号选中存储芯片;地址低位接到存储芯片的地址端,选择芯片内部的存储单元。该法存储单元的地址不唯一。

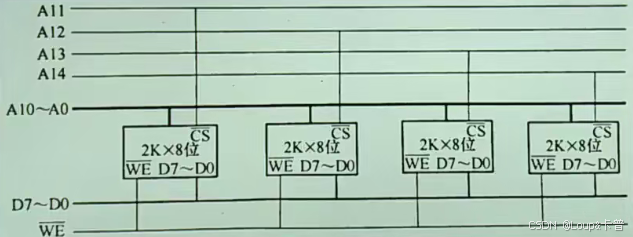

3. 线选法

不适用译码器,直接将地址线的高位作为片选线。各存储芯片地址范围?

A19-A15

00000

A14-A11

1110

A10-A0 全0 全1