文章目录

- [第二节 串行通信协议](#第二节 串行通信协议)

- [第三节 串行接口标准RS-232C](#第三节 串行接口标准RS-232C)

- [第四节 可编程串行接口芯片8251A](#第四节 可编程串行接口芯片8251A)

-

- 一、基本性能

- 二、内部结构

- 三、外部引脚功能

-

- [1. 同CPU的连接信号](#1. 同CPU的连接信号)

- [2. MODEM控制信号(4个)](#2. MODEM控制信号(4个))

- [3. 发送器有关信号(4个)](#3. 发送器有关信号(4个))

- 4.接收器有关信号(4个)

- 四、8251A的编程

-

- [1. 方式指令](#1. 方式指令)

- [2. 命令指令](#2. 命令指令)

- [3. 状态字](#3. 状态字)

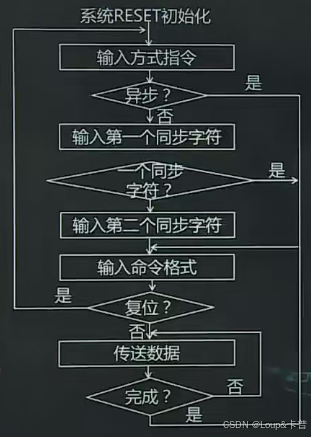

- [4. 初始化与操作流程](#4. 初始化与操作流程)

第二节 串行通信协议

通信协议:通信双发对数据传送控制的一种约定,又称通信规程或链路控制规范

约定包括:

- 数据格式

- 同步方式

- 传送速率

- 传送步骤

- 检测纠错方式

- 控制字符

一、异步串行通信协议

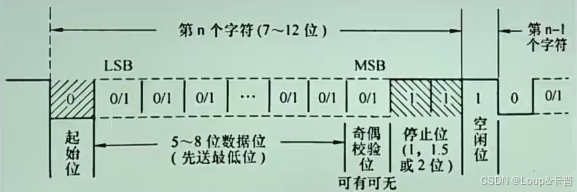

异步串行通信协议:靠起始位和停止位来进行字符同步,也称起止式协议。

异步串行通信数据格式

起始位用逻辑电平零

停止位用逻辑电平高表示

接收过程:接受设备不断检测传输线,当检测到一系列的"1"后检测到1个"0"即确认一个字符开始,于是以位时间位间隔移位接受规定的数据位和奇偶检验位,这之后应接收规定位长的停止位"1",若没有收到即为 "帧出错"。

一个字符接收完毕,接收设备继续检测传输线,监视起始位"0"的到来,即下一个字符的开始。

二、同步串行通信协议

同步串行通信协议:以数据块为单位(帧)传送,每个数据块由一个字符序列组成,每个字符取相同位数,字符间连续,没有起始位和停止位,不能有空隙。

帧头部 :数据块的前面设置1-2个同步字符,作为帧的边界和通知对方接收的标志。

帧尾部:校验字符

发送方和接收方要完全同步,用同一时钟进行移位操作。

同步通信规程:面向字符型、面向比特型、面向字节计数。

第三节 串行接口标准RS-232C

一、RS-232C信号线定义

一个完整的RS-232C接口:22根线,采用标准25芯插座。

信道 :主信道、辅信道

远距离串行通信接口标准:基本信号9根。

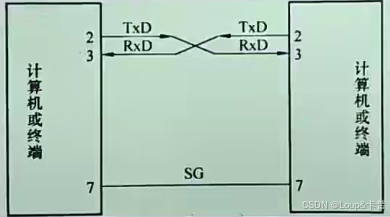

不同应用场合连线不同,最简单场合只需3根信号线。

RS-232C最简连接

二、电气特性

- 应保持电平在 ± (3-15)V

在数据线T5V,xD和RxD上:逻辑1=-3-15V,即电平低于-3V;逻辑0=+3V-+15V,即电平高于+3V。 - 必须进行电平转换

RS-232C采用佛罗基,其逻辑电平与TTL电平不同。为实现与TTL电路连接,进行电平转换。采用电平转换芯片MAX232和MAX232A(高速) - 必须抗共模噪声干扰

【例题】在以RS-232C标准传送信息时,表示逻辑"1"的电平信号是()

A. +5V

B. -5V

C. 0V

D. +12V

B. 逻辑1电平 -3 --- -15V,采用负逻辑规定逻辑电平。

第四节 可编程串行接口芯片8251A

一、基本性能

8251A USART 通用同步/异步接收发生器,基本性能:可用于同步和异步传送

同步传送 :5 - 8 bit/字符,内部或外部同步,可自动插入同步字符。

异步传送 :5 - 8 bit/字符,时钟速率为通信波特率的1、16、64倍

可产生中止字符 :可产生1、1.5、2个位的停止位,可检查假启动位,自动检测和处理中止字符。

波特率 :DC - 19.2kbit/s(异步),DC - 64kbit/s(同步)

完全双工,双缓冲器和接收器。

误差检测具有奇偶、溢出和帧错误等检测电路。

与Intel8080、8085、8086及8088CPU兼容。

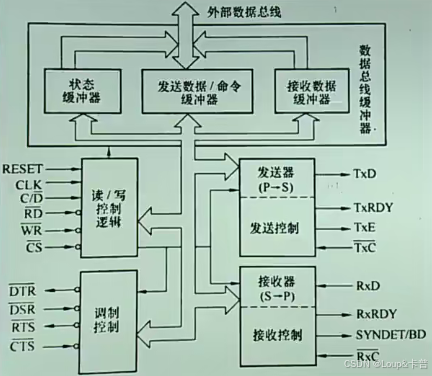

二、内部结构

8251A内部结构框图

- 数据总线缓冲器

三态双向8位缓冲器,使8251A与系统总线连接起来。包含数据缓冲器和命令缓冲器。 - 接收器

在接收时钟RxC作用下,接收RxD引脚上的帧格式化串行数据,并转换为并行数据。

同时进行校验,若无错,将并行数据存放在数据总线缓冲器中,并发出接收器准备好信号(RxRDY=1),通知CPU读数。

若校验有误,则在状态寄存器中保存,以便CPU处理。

错误类型有3种:奇偶错误、帧错误、溢出(丢失)错误 - 发送器

把待发送的并行数据转换成所要求的帧格式,在发送时钟TxC作用下,由TxD引脚逐位的发送。发送完一帧数据后发送器准备好信号置位(TxRDY=1),通知CPU发送下一帧数据。 - 读/写控制和调制控制

实现对8251A的读写和对MODEM的控制。

三、外部引脚功能

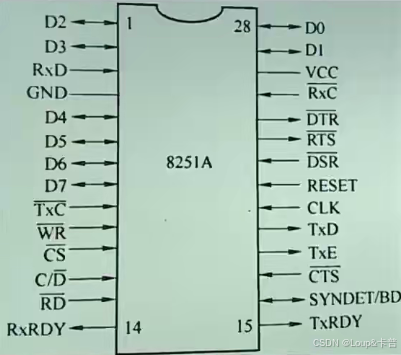

8251A外部引脚图

1. 同CPU的连接信号

RESET:6倍时钟宽的高电平信号使得芯片复位,处于空闲状态。

CLK:时钟输入端,同步方式下该时钟频率比数据速率大30倍以上,异步方式下大4.5倍。

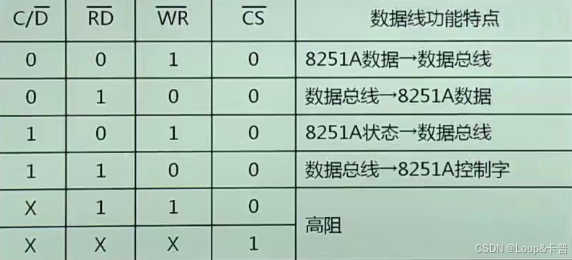

/WR、/RD:读/写信号输入端。

C/#D:输入高电平,CPU对芯片写控制字或读控制字;反之,读/写内容为数据。与地址线的最低位相连。

8251A占两个端口地址,偶地址为数据,奇地址为控制。

/CS:片选输入端,与地址译码器输出连接。

D0-D7:双向8为数据线,CPU通过D0-D7写控制字或数据,读状态字或数据。。

2. MODEM控制信号(4个)

/DTR:数据终端准备好,输出,低有效,CPU准备就绪。

/RSR:数据装置准备好,输入,低有效,表示调制解调器或外设的数据准备好。

/RTS:请求发送,输出,低有效,通知调制器,CPU已准备好发送。

/CTS:清除发送信号,输入,低有效,由调制解调器或其他外设送到8251A,表示允许USART发送数据。

3. 发送器有关信号(4个)

TxD:发送数据

TxRDY:发送器准备好。有雄安表示发送缓冲器已空,CPU可以相芯片送入新数据。

TxE:发送缓冲器空标志。只要发送缓冲器种没有再要发送的字符该引脚就变高。克表示一段数据传输的结束。

/TxC:输入控制发送器数据速率的时钟。每个数据的移位输出都是在/TxC的下降沿实现的。

4.接收器有关信号(4个)

RxD:接收数据。

RxRDY:接收器准备好。为高有效表示接收缓冲器由组装好的一个数据字符,可通知CPU取走。

/RxC:接收时钟输入端。时钟的上升沿,把数据取样输入。常与/TxC共用同一个时钟源。

SYNDET/BD:同步方式下的同步检测端和异步方式下的终止检测输出。

四、8251A的编程

方式指令:定义8251A的一般工作特性,复位后由CPU写入。

命令指令:指定芯片的实际操作,在写入方式指令之后。

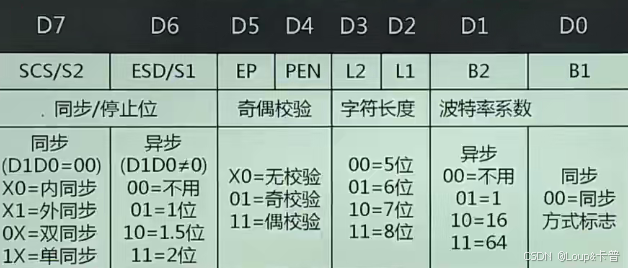

1. 方式指令

指定通信方式及方式下的数据格式。

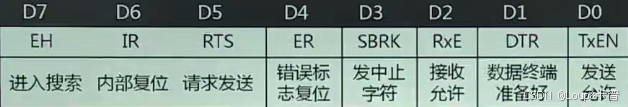

2. 命令指令

指定8251A进行某种操作或处于某种状态。

TxEN:允许发送。=1,允许发送;可作发送中断屏蔽位。

DTR:数据终端准备就绪。=1,表示终端设备已准备好。

RxE:允许接收。 = 1,允许接收;可作接收中断屏蔽位。

SBRK:发中止字符。=1,强迫TxD为低电平,输出连续的空号,即空闲时的输出数据为低电平;=0,正常操作,

线路输出仍为高电平。

ER:错误标志复位。=1,使状态字中的错误标志位(PE/OE/FE)复位。

RTS:请求发送。=1,强迫/RTS为低电平,使其有效。DTR和RTS是送往MODEM的控制信号。

IR:内部复位。=1,进行内部复位,发方式命令之前一定要进行内部复位。

EH:进入搜索方式。=1,启动搜索同步字符,此时将接收到的数据码逐位组合成字符,做同步比较,直到找到同步码后,引脚SYNDET输出1为止。然后再把这个控制位回到0,做正常接收。

地址区分:方式指令和命令指令写入时所用的口地址相同,采用写入次序进行区分。对异步通信,复位后写u人的为方式指令,此后写入的才是命令指令。

3. 状态字

CPU向8251A发送各种操作命令字,是依据8251A当前的运行状态决定的。

状态字中的错误标志是再接收过程中自动检测设置的。

【例题】

从8251A的状态字可知,有哪些出错检测?

【答案】帧出错、溢出错、奇偶错

【解析】8251A的状态字中D3-D5这3个位用来标志接收时检测3类错误,帧出错、溢出错、奇偶错。

4. 初始化与操作流程