`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date:

// Design Name:

// Module Name: DIV

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module division

(

input wire [31:0] dividend ,

input wire [31:0] divisor ,

input wire start ,

input wire sys_clk ,

input wire sys_rst_n ,

output wire [31:0] q ,

output wire [31:0] r ,

output wire busy ,

output wire valid

);

reg [4:0] count;

reg [31:0] reg_q;

reg [31:0] reg_r;

reg [31:0] reg_b;

reg busy2,r_sign;

reg out_busy ;

reg flag1,flag2;

wire ready;

wire [32:0] add_sub;

wire [31:0] r_temp;

wire [31:0] q_temp;

assign busy = out_busy ;

assign valid = ~out_busy ;

assign ready=~out_busy&busy2;

assign add_sub=r_sign?({reg_r,q_temp[31]}+{1'b0,reg_b}):({reg_r,q_temp[31]}-{1'b0,reg_b});

assign q_temp=reg_q;

assign q=flag1?(~q_temp+1):q_temp;

assign r_temp=r_sign?reg_r+reg_b:reg_r;

assign r=flag2?(~r_temp+1):r_temp;

always @ (posedge sys_clk or negedge sys_rst_n)

begin

if( sys_rst_n == 1'b0 )

begin

count <= 5'b0;

out_busy <= 1'b0;

busy2 <= 1'b0;

end

else

begin

busy2 <= out_busy;

if( start == 1'b1 )

begin

reg_r<=32'b0;

count<=5'b0;

r_sign<=1'b0;

out_busy<=1'b1;

flag1<=dividend[31]^divisor[31];

flag2<=dividend[31];

reg_q<=dividend[31]?~(dividend-1):dividend;

reg_b<=divisor[31]?~(divisor-1):divisor;

end

else if( out_busy == 1'b1 )

begin

reg_q <= { reg_q[30:0],~add_sub[32] } ;

reg_r <= add_sub[31:0];

r_sign <= add_sub[32];

count <= count+5'b1;

if( count == 5'b11111 )

begin

out_busy <= 0;

end

end

end

end

endmoduletb

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/04/10 11:24:59

// Design Name:

// Module Name: tb_division

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

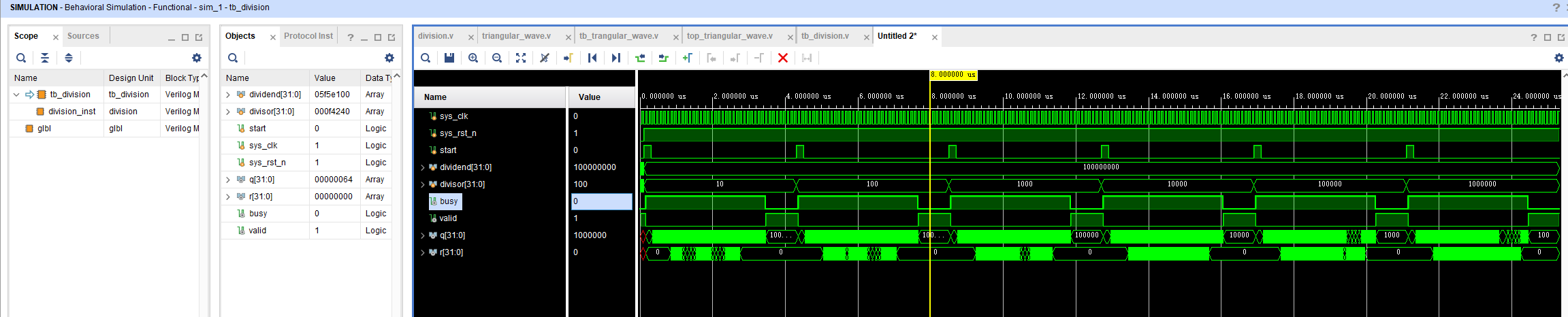

module tb_division();

// Inputs

reg [31:0] dividend;

reg [31:0] divisor;

reg start;

reg sys_clk;

reg sys_rst_n;

// Outputs

wire [31:0] q;

wire [31:0] r;

wire busy;

wire valid ;

// Instantiate the Unit Under Test (UUT)

division division_inst (

.dividend(dividend),

.divisor(divisor),

.start(start),

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.q(q),

.r(r),

.busy(busy),

.valid(valid)

);

initial

begin

dividend = 0;

divisor = 0;

start = 0;

sys_clk = 0;

sys_rst_n = 0;

#100;

sys_rst_n = 1'b1 ;

start = 1;

dividend = 32'd1_0000_0000;

divisor = 32'd10;

#200;

start = 0;

#4000;

start = 1;

dividend = 32'd1_0000_0000;

divisor = 32'd100;

#200;

start = 0;

#4000;

start = 1;

dividend = 32'd1_0000_0000;

divisor = 32'd1000;

#200;

start = 0;

#4000;

start = 1;

dividend = 32'd1_0000_0000;

divisor = 32'd1_0000;

#200;

start = 0;

#4000;

start = 1;

dividend = 32'd1_0000_0000;

divisor = 32'd10_0000;

#200;

start = 0;

#4000;

start = 1;

dividend = 32'd1_0000_0000;

divisor = 32'd100_0000;

#200;

start = 0;

#4000;

$finish;

end

always

begin

#50;

sys_clk = ~sys_clk;

end

endmodule