一、MAC简介

stm32自带有10/100Mbit/s的以太网MAC内核,他提供地址以及媒体访问的控制方式。

MAC内核特性:

传输速率:支持外部PHY接口实现10/100Mbit/s数据传输速率;

协议标准:符合IEEE802.3/3u的MII和RMII接口与快速以太网PHY通信;

工作模式:支持全双工和半双工操作;

站管理接口:支持通过MDIO接口配置和管理PHY设备;

MAC内核是单片机自带,比如STM32F4/STM32H7,这些单片机自带了MAC内核;

当然有些单片机是不带MAC内核,所以不带MAC内核的单片机要做怎么进行通讯,据我之前所了解需要购买带MAC内核的PHY芯片

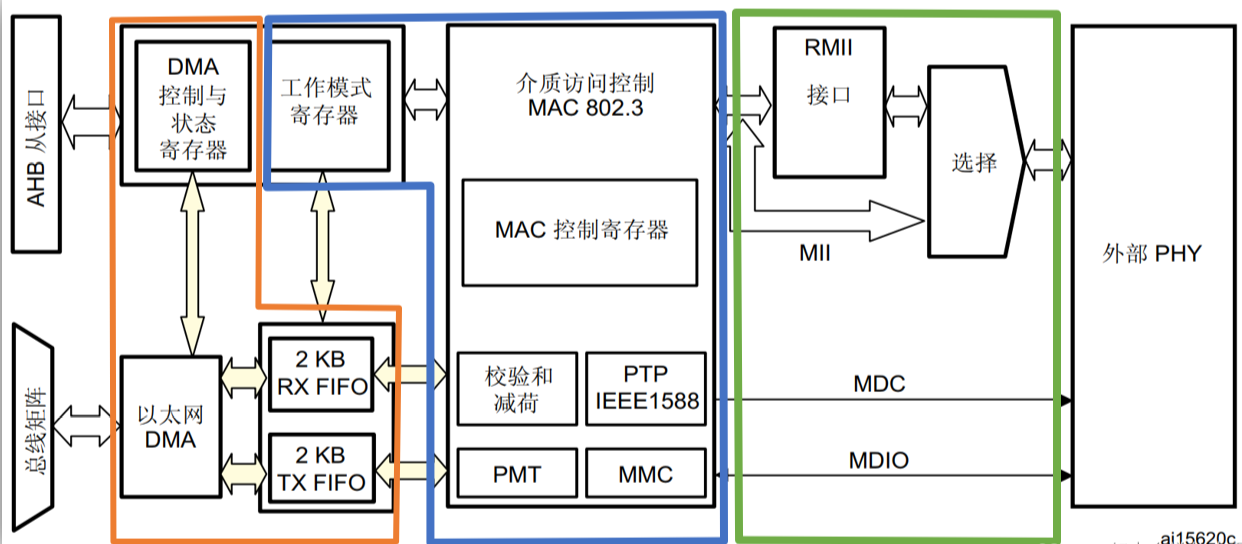

二、STM32的ETH框架

按照从左向右的顺序介绍:

- 以太网DMA数据包以DMA方式发送/接收

- MAC内核以太网帧发送时,给数据加上一些控制信息;以太网接收时,去掉控制信息;

- PHY交互接口:数据通道------介质接口RMII/MII;管理通道------SMI站管理接口。

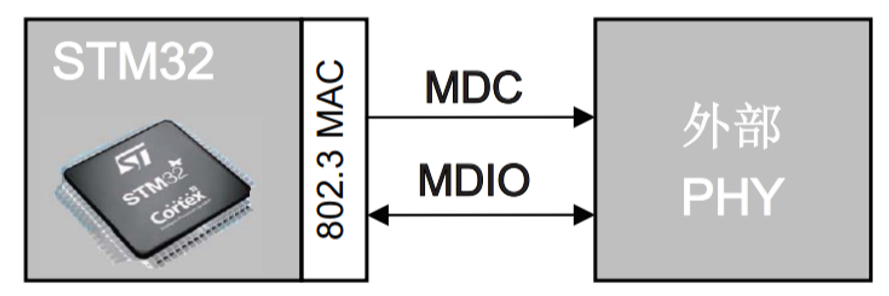

三、SMI站管理接口

允许应用程序通过时钟线和数据线访问任意PHY寄存器,最多支持32个PHY访问

- MDC:周期始终引脚(最大频率为2.5MHz);

- MDIO:数据输入/输出比特流。

也就是STM32这个MAC内核最多能够控制32个PHY芯片,这个总线其实跟IIC类似,那么肯定有地址控制。

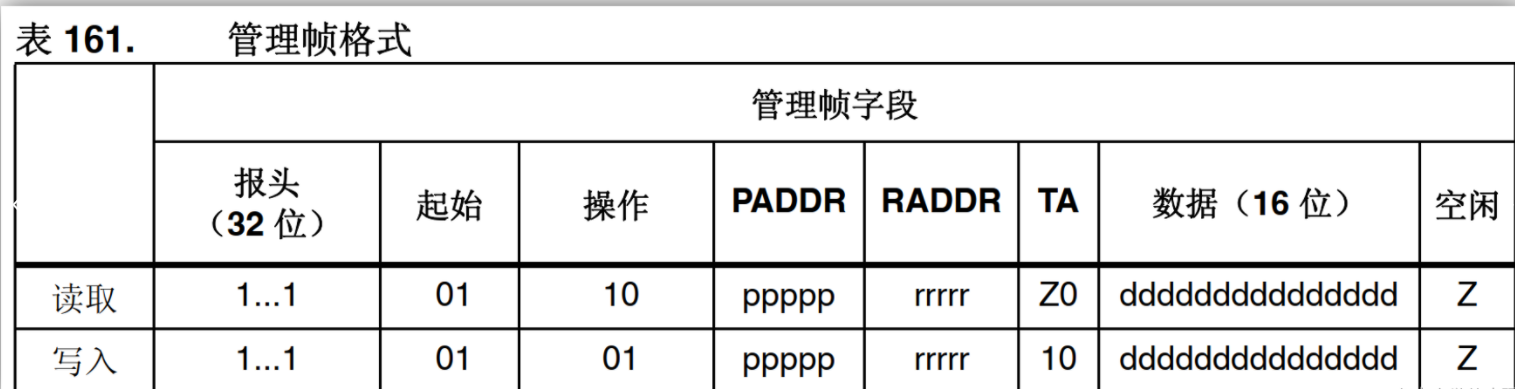

1、SMI帧格式

- PADDR:PHY地址(00_1F);

- RADDR:寄存器地址(00_1F);

- 数据位:16位数据位(PHY寄存器都是16位)。

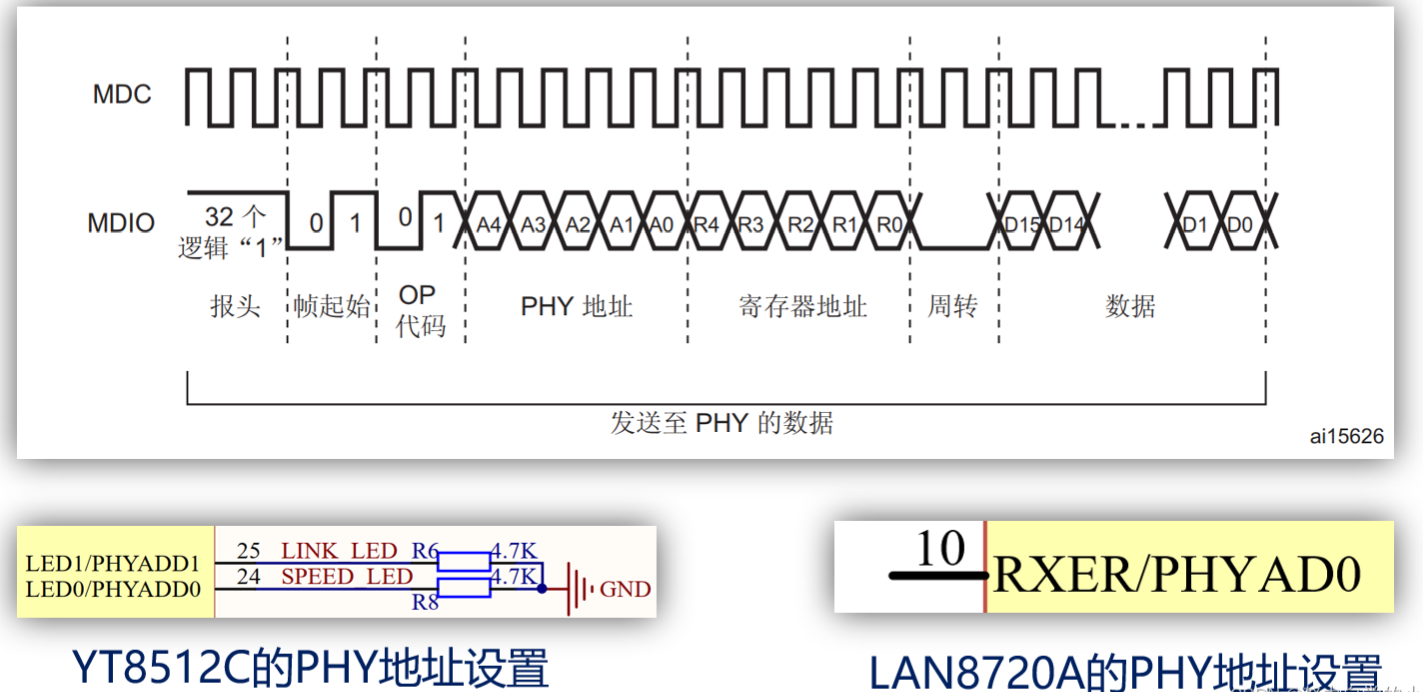

- 下图可看出PADDR是5位,最多控制32个,所以只要我们将PHY芯片地址设置好,就可控制多个PHY芯片。

MDIO时序和帧结构------写周期

2、MDC时钟来自哪里?

MDC的时钟来自于stm32内部,是通过AHB时钟树分频得到的。

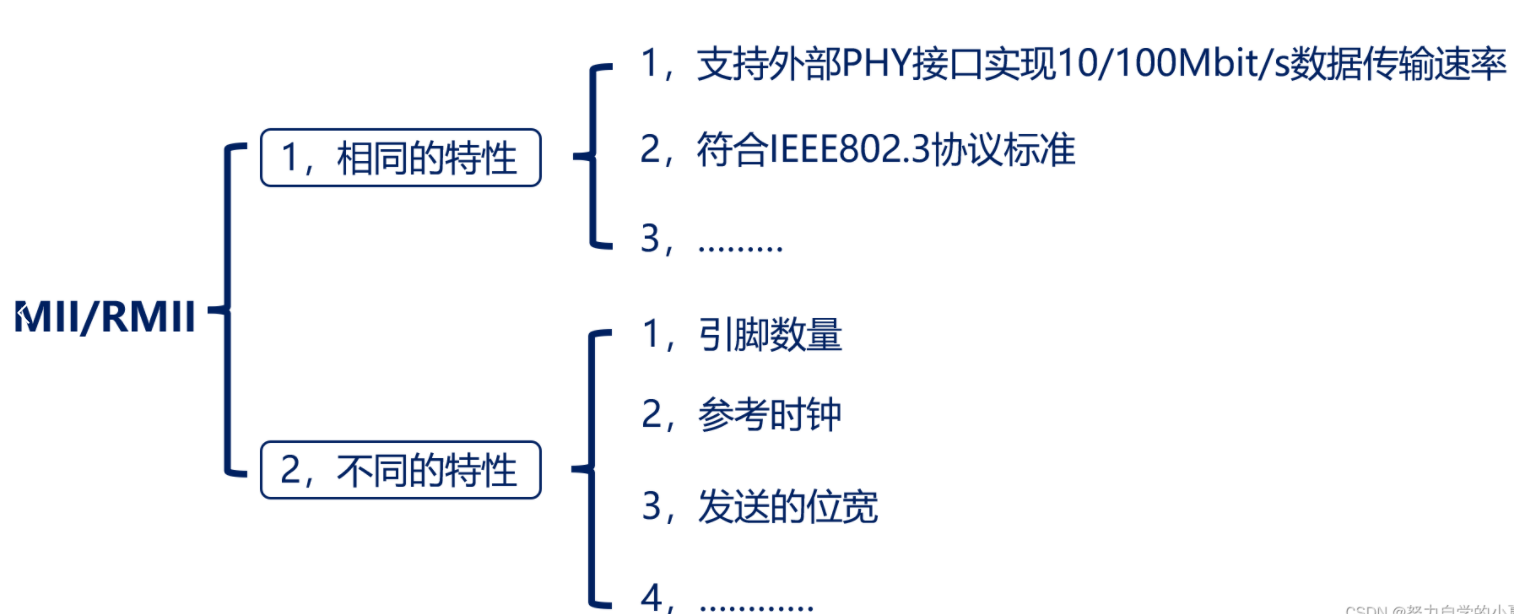

四、介质接口MII与RMII

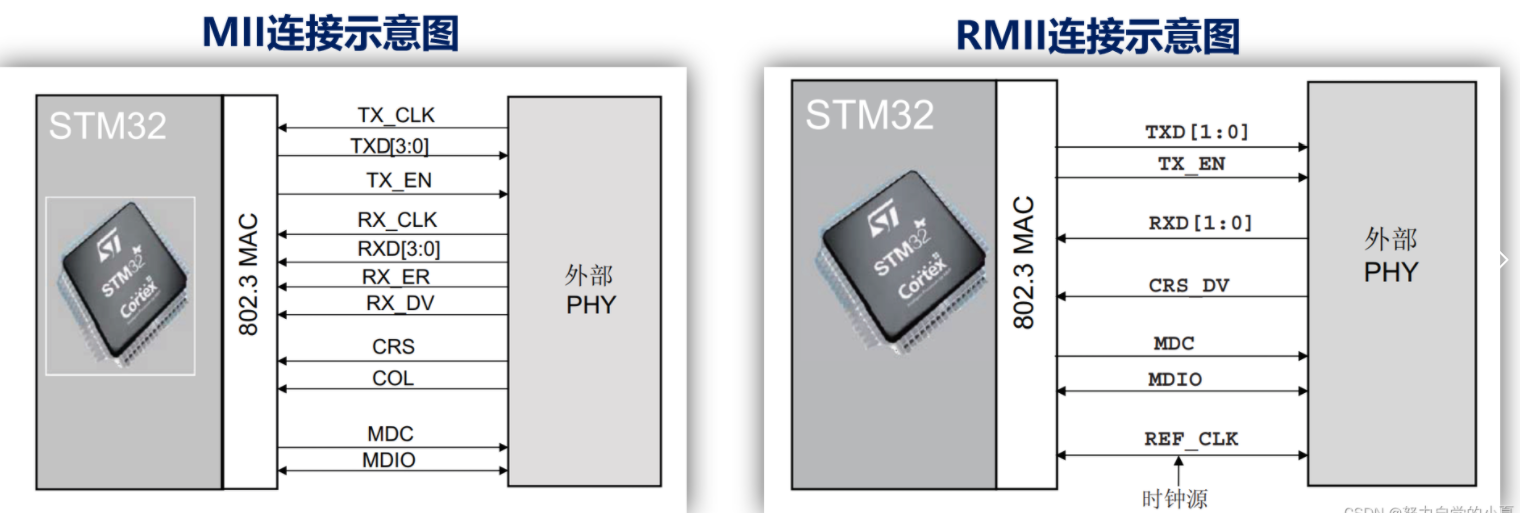

MII有16个引脚,RMII只有9个引脚

MII参考时钟是25MHz,而RMII是50MHz

MII是4位位宽,而RMII只能收发2位位宽

综上所诉,所以大家基本布板选用RMII连接走线比较多

介质接口MII、RMII引脚数量

MII所需引脚位16个,而RMII所需只有9个;

MII的TX_CLK和RX_CLK由PHY芯片提供,使得MAC内核以这个时钟采集收发数据;

RMII的REF_CLK,MAC内核以这个时钟采集收发数据。

注意:RX_ER和RX_DV用来检测以太网帧是否有效;而CRS和COL以及CRS_DV在全双工模式下无效。