芯片后门不是科幻片!从英伟达H20到英特尔ME,你的电脑可能正躺着个"硬件间谍",最近网信办约谈英伟达的新闻都看了吧?H20芯片被曝能远程自毁+定位追踪,这波直接让搞AI训练的实验室集体血压飙升。今天咱就扒一扒这些藏在纳米级电路里的"硬件内鬼"。

一、芯片后门介绍

1.1 后门定义与分类

芯片后门是指在集成电路设计或制造过程中恶意植入的硬件电路,能够在特定条件下触发,实现非授权控制、数据窃取或系统破坏等功能。根据植入阶段不同,可分为:

-

设计阶段后门:在芯片设计阶段植入,通常通过第三方IP核或设计工具引入

-

制造阶段后门:在芯片制造过程中通过修改掩模版等方式植入

-

固件级后门:隐藏在芯片配套固件中的恶意代码

1.2 后门的危害场景

芯片后门一旦触发,可能导致:

-

系统控制权劫持:攻击者获得芯片最高权限

-

敏感数据泄露:加密密钥、生物特征等核心数据被窃取

-

远程控制系统:实现远程关闭或追踪定位功能

-

系统功能破坏:导致芯片永久性失效

近期国家网信办就英伟达H20算力芯片漏洞后门安全风险进行约谈,曝光的正是"追踪定位 "和"远程关闭"两大高危风险。这类芯片广泛应用于金融风控、工业质检等关键领域,一旦被触发后果不堪设想。

二、后门实现技术

2.1 模拟硬件木马(A2攻击)

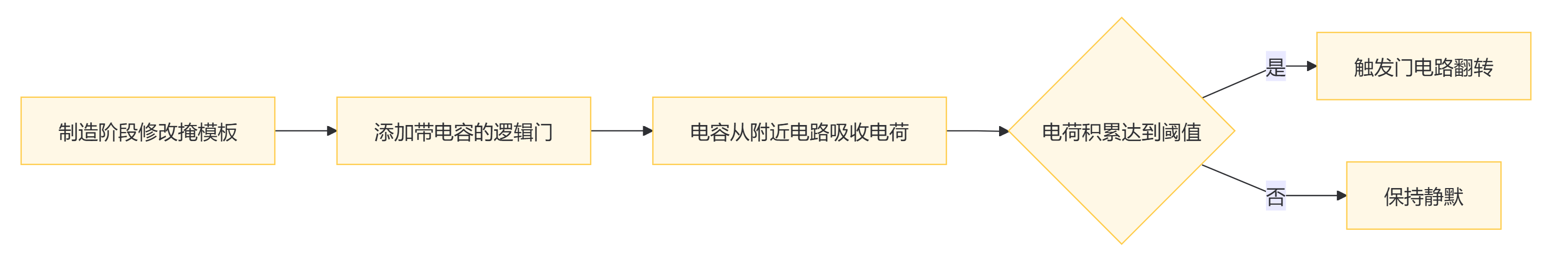

密歇根大学研究人员在DARPA资助下开发的A2(模拟攻击)技术代表了制造阶段植入后门的顶尖水平。其核心技术原理:

这种后门的核心优势在于:

-

物理级隐蔽:利用晶体管本身的物理特性(电荷泄露/聚集),不依赖数字逻辑

-

极小微面积:面积仅为传统数字后门的1/1000(约百万门中的单个门)

-

环境适应性:在-25℃~100℃范围内稳定工作

-

抗检测性:不改变芯片功耗、温度、时序特征,传统测试方法几乎无法发现

2.2 RTL级硬件木马

在寄存器传输级植入的后门更具灵活性。攻击者通常采用以下技术手段:

// 伪代码示例:基于AES的泄密型硬件木马

module trojan_aes(

input wire clk,

input wire rst_n,

input wire [127:0] plaintext,

input wire [127:0] key

);

// 合法AES加密模块

aes_encrypt u_legit(.clk(clk), .rst_n(rst_n), .plaintext(plaintext), .key(key)...);

// 木马触发逻辑

reg [31:0] trigger_counter;

always @(posedge clk) begin

if (plaintext == 128'hDEADBEEF... ) // 特定数据模式触发

trigger_counter <= trigger_counter + 1;

end

// 数据泄密通道

wire [127:0] ciphertext_leak;

assign ciphertext_leak = (trigger_counter > 32'hFFFF) ? ciphertext : 0;

// 通过隐通道发送数据

此类木马可通过代码混淆技术躲避审查:

-

使用非常规条件判断(如多级异或门组合)

-

触发条件与低概率事件绑定(如特定指令序列)

-

输出通过物理层隐通道传输(电磁、功耗、温度等)

2.3 基于缓存的IP后门

第三方缓存IP(如RAM、TCAM)是后门重灾区。攻击者通过在缓存中预设特定数据模式触发恶意行为:

传统触发方式:写入特定数据序列 → 触发后门 → 执行恶意操作

无害化改造原理:

原始数据 → [写入预处理] → 变换后数据存入缓存

读取数据 → [读出预处理] → 恢复原始数据其中预处理算法可包括:

-

异或掩码 :

data_trans = data_orig ^ mask -

循环移位 :

data_trans = {data_orig[15:0], data_orig[31:16]} -

动态参数化加密 :

data_trans = AES_Encrypt(key, data_orig),密钥可随机生成或定期更换

2.4 物理层后门技术

除了电路级后门,物理层面的攻击同样危险:

-

非侵入式攻击:通过分析功耗、电磁辐射等旁路信号提取密钥

-

半侵入式攻击:去封装后利用激光故障注入篡改执行流程

-

全侵入式攻击:使用微探针直接读取芯片内部存储单元

表:常见芯片后门技术对比

| 类型 | 植入阶段 | 触发机制 | 检测难度 | 典型案例 |

|---|---|---|---|---|

| 模拟硬件木马 | 制造 | 物理特性(电荷积累) | 极高 | 密歇根大学A2攻击 |

| RTL级木马 | 设计 | 特定数据/指令序列 | 高 | AES泄密木马 |

| 缓存IP后门 | IP集成 | 特定数据模式 | 中 | 第三方RAM IP后门 |

| 管理引擎后门 | 设计 | 远程命令 | 极高 | Intel ME后门 |

三、后门检测与鉴别技术

3.1 基于能量分析的检测

针对后门指令的检测可采用能量分析技术:

-

指令分段穷举

-

采集各指令能量迹

-

特征比对分析

-

简单能量分析(SPA):直接观察能量迹差异

-

差分能量分析(DPA):统计分析多组能量迹

-

相关能量分析(CPA):计算能量消耗与预测值的相关性

-

实验证明,后门指令通常表现出:

-

异常功耗峰值:触发时出现非常规功耗特征

-

电磁辐射异常:特定频段辐射强度显著提高

-

时序偏移:指令执行周期出现微小偏差

3.2 形式化验证方法

使用定理证明器Coq对RTL代码进行形式化验证8:

-

建立RTL到Coq的转换规则

-

对信号附加密级属性

-

公开信号

-

秘密信号(如加密密钥)

-

受控信号

-

-

定义安全定理:如"秘密信号不可通过公开端口输出"

-

数学证明验证:通过Coq引擎验证定理成立性

该方法已成功检测DES/AES实现中的硬件木马,特别适合安全关键型IP核验证。

3.3 网表级木马清除技术

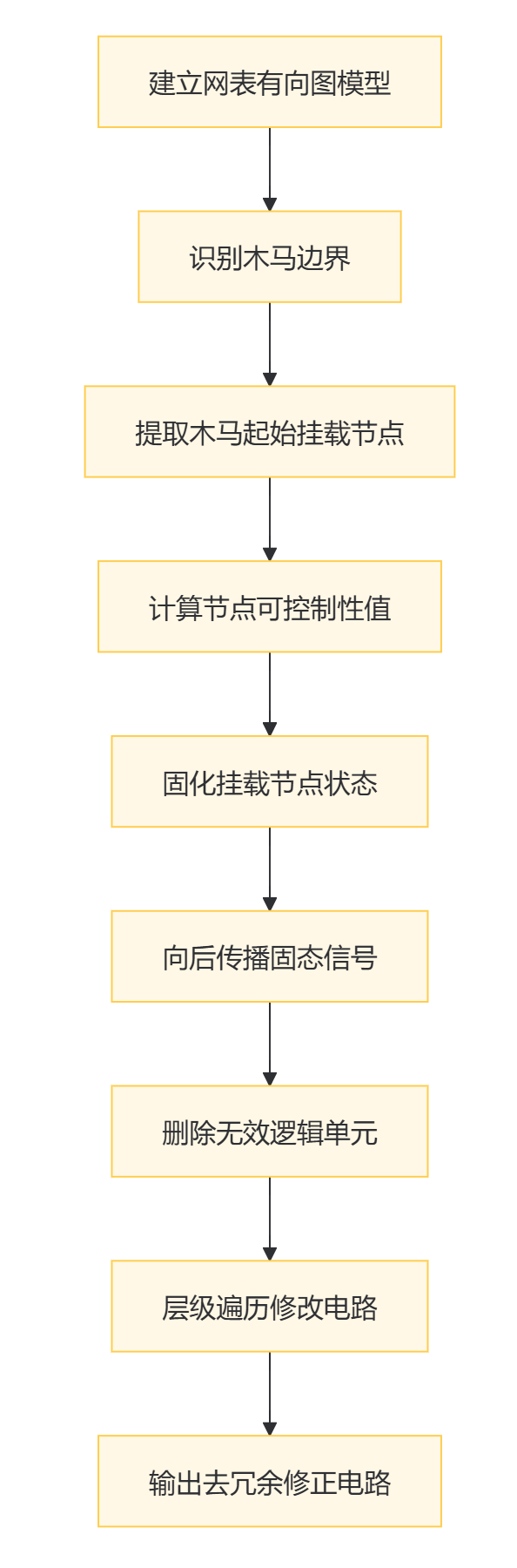

针对已识别后门的IP固核网表,可采用系统化移除方法:

关键技术点:

-

SCOAP算法:计算节点可控制性(CC0/CC1值)

-

真值表冗余消除:根据输入状态简化逻辑门

-

固态信号传播:将固定值传播至下游电路

3.4 物理检测方法

对于最终成品芯片,可采用物理检测手段:

-

X射线层析成像:对比每层电路与设计图纸的差异

-

红外热成像:检测异常热点区域

-

电子显微镜分析:纳米级电路结构检查

-

功耗图谱分析:高精度测量芯片功耗特征

然而这些方法通常成本高昂 且可能破坏样品,适合抽样检测或关键场合。

四、系统级防御体系构建

4.1 可信制造链建设

应对制造阶段植入的后门,需要:

-

晶圆级溯源:建立晶圆到芯片的全程追溯系统

-

多地域分制造:关键层在不同代工厂制造

-

光罩安全存储:使用加密存储+物理隔离保护掩模板

4.2 动态数据变换技术

针对缓存IP后门,采用预处理模块实现动态防护:

# 动态异或掩码示例

import os

class CacheSanitizer:

def __init__(self, mode='xor'):

self.mode = mode

self.key = os.urandom(16) # 生成随机密钥

def write_preprocess(self, data):

if self.mode == 'xor':

return bytes(a ^ b for a, b in zip(data, self.key))

elif self.mode == 'aes':

cipher = AES.new(self.key, AES.MODE_ECB)

return cipher.encrypt(data)

def read_postprocess(self, data):

if self.mode == 'xor':

return bytes(a ^ b for a, b in zip(data, self.key))

elif self.mode == 'aes':

cipher = AES.new(self.key, AES.MODE_ECB)

return cipher.decrypt(data)

def key_rotation(self, new_key=None):

self.key = new_key or os.urandom(16) # 定期更换密钥4.3 硬件可信根架构

构建基于硬件的信任链:

-

PUF物理不可克隆函数:利用芯片制造差异生成唯一密钥

-

安全启动链:ROM → Bootloader → OS逐级验证

-

运行时监控:

-

异常指令检测

-

内存完整性检查

-

功耗实时监控

-

4.4 国产化替代路径

在关键领域推进国产芯片替代:

-

架构自主:RISC-V等开放指令集

-

工具链可控:

-

国产EDA工具(如华大九天)

-

自主IP核库

-

-

制造本土化:中芯国际等代工厂产能支持

-

可信封测:建立安全封测产线

英伟达H20芯片事件后,我国采取"解禁与安全审查并行"策略,在允许特定芯片流通的同时,为国产算力芯片(昇腾、寒武纪等)争取替代时间。

五、前沿案例与趋势分析

5.1 近期安全事件

-

英特尔ME事件:管理引擎被曝存在独立操作系统,可完全控制系统且永不关闭

-

英伟达H20芯片风险:被指存在"追踪定位"和"远程关闭"功能,遭国家网信办约谈

-

学术界的A2攻击:密歇根大学展示制造阶段植入的物理级后门

5.2 新兴防御技术

-

激光传感器网络:在芯片内部部署传感器检测物理篡改

-

机器学习检测:利用CNN分析电路图像识别异常模式

-

量子指纹技术:基于量子效应生成不可克隆的芯片标识

-

3D集成监控:在逻辑层上方堆叠监控层实时检测

六、实战建议清单

-

供应链审计

-

优先选择开源架构(如RISC-V)

-

审查第三方IP来源证书

-

要求提供形式化验证报告

-

-

部署防护措施

# 缓存防护模块实例化 cache_sanitizer = CacheSanitizer(mode='aes') # 设置密钥轮换定时器(每小时) scheduler.every(1).hours.do(cache_sanitizer.key_rotation) -

定期安全检测

-

每季度执行功耗分析

-

关键系统年度X光检测

-

固件更新时验证数字签名

-

-

应急响应计划

-

建立芯片级安全事件响应流程

-

准备关键系统备用芯片

-

与专业安全机构合作分析

-

芯片后门防护是一场持续的攻防对抗战。随着芯片制造工艺不断进步和后门技术日益隐蔽,安全从业者必须深入理解硬件底层原理,构建多层防御体系,并积极推进核心技术自主可控。只有将硬件安全 、供应链安全 和操作安全有机结合,才能有效应对日益严峻的芯片后门威胁。

如安全专家在分析POWER9芯片时所言:"在像POWER9这样复杂的体系结构中嵌入后门有着无尽的可能性"。这提醒我们:没有绝对的安全,只有持续的风险管理和技术革新。

欢迎在评论区交流芯片安全防护经验,或分享您遇到的相关技术挑战。