奇偶校验原理与FPGA实现

- 写在前面

- 一、基础原理

-

- [2.1 奇校验](#2.1 奇校验)

- [2.2 偶校验](#2.2 偶校验)

- [2.3 缺点](#2.3 缺点)

- 二、举个例子

-

- [3.1 奇校验例子](#3.1 奇校验例子)

- [3.2 偶校验例子](#3.2 偶校验例子)

- [3.3 检测出错例子](#3.3 检测出错例子)

- 三、FPGA实现

- 写在后面

写在前面

奇偶校验码是一种简单的检错码,主要用于数据传输或存储过程中检测奇数个比特错误或者偶数个比特错误,其实现简单、开销低,但可靠性低、检错能力有限,在UART、RS23等低速串行接口或者早期的存储中会使用到。

一、基础原理

奇偶校验码核心原理 是通过增加一个校验位,使得整个数据(包括校验位)中"1"的个数满足奇偶性(奇数或偶数),从而检测传输或存储过程中可能发生的单比特错误。具体地,奇偶校验分为奇校验 和偶校验。

2.1 奇校验

发送端 ,在序列尾部增加1位校验位,确保发送的整个二进制序列中"1"的总个数位奇数。

接收端,判断接收到的二进制序列中的"1"的总个数是否为奇数,若为奇数,则校验通过,认为数据传输正确;若为偶数,则校验失败,认为数据传输错误。

2.2 偶校验

发送端 ,在序列尾部增加1位校验位,确保发送的整个二进制序列中"1"的总个数位偶数。

接收端,判断接收到的二进制序列中的"1"的总个数是否为奇数,若为偶数,则校验通过,认为数据传输正确;若为奇数,则校验失败,认为数据传输错误。

2.3 缺点

奇偶校验码在数据传输的过程中仅增加了1位的冗余,所增加的额外开销小,但检错能力有限,若出错的数据个数为偶数,则无法检测出来错误。

二、举个例子

假设在发送端需要传输一个二进制序列11100001。

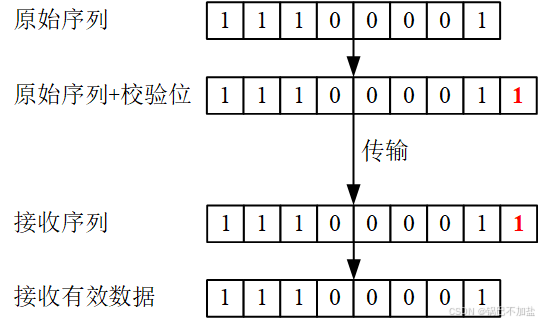

3.1 奇校验例子

若为奇校验,此时序列中"1"的个数为偶数,发送端增加的校验位应为1。在接收端,接收到的序列中"1"的总个数为奇数,取出有效数据。

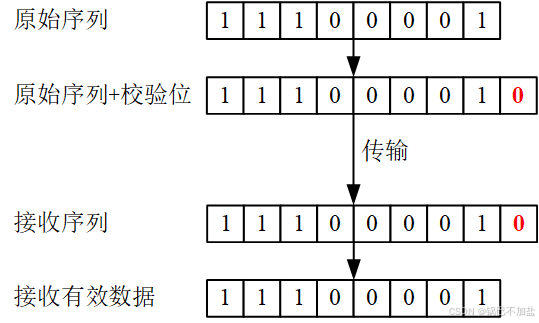

3.2 偶校验例子

若为偶校验,此时序列中"1"的个数为偶数,发送端增加的校验位应为0。在接收端,接收到的序列中"1"的总个数为偶数,取出有效数据。

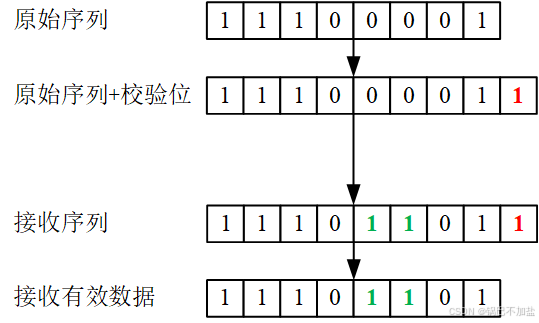

3.3 检测出错例子

采用奇校验,在传输过程中出现了2比特的错误,但是在接收端统计"1"的个数仍为奇数,认为接收到数据无误,实际上数据有误。

三、FPGA实现

以下为奇偶校验码的Verilog实现代码,由于较为简单,这里不提供仿真环境。

c

module parity_check

#(

parameter DW = 8

)

(

input clk ,

input rst_n ,

input [DW-1 :0] data_in ,

input mode , // 0:偶校验 1:奇校验

output reg [DW :0] data_out ,

output reg parity_bit

);

always @(posedge clk) begin

data_out <= mode ? {data_in,(^data_in)} : {data_in,(~(^data_in))};

parity_bit <= mode ? (^data_in) : (~(^data_in));

end

endmodule写在后面

本文中我们学习了奇偶校验的基础原理,同时给出了奇校验、偶校验的例子以及相应的RTL代码。

🧐:以上为个人学习笔记,如有疑问,欢迎评论区交流探讨 !!!