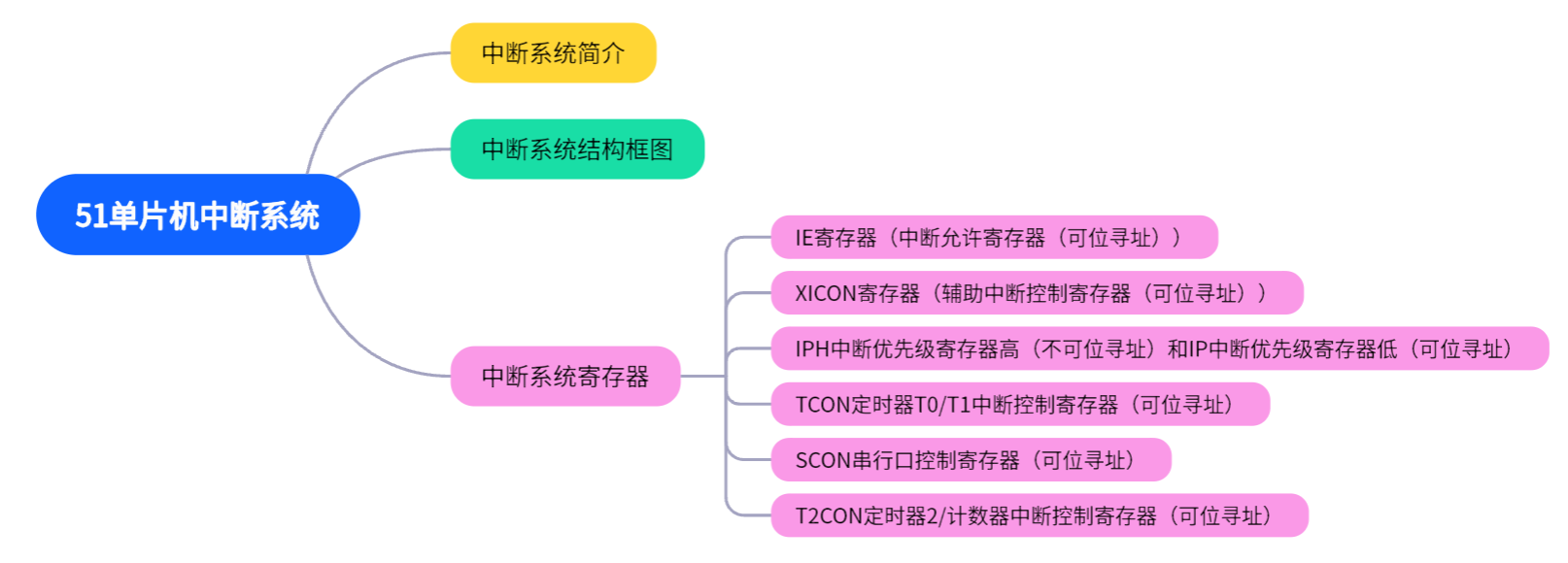

本质概述思维导图:

51单片机中断系统

中断系统概述

中断系统是为使CPU具有对外界紧急事件的实时处理能力而设置的。

当中央处理机CPU正在处理某件事的时候外界发生了紧急事件请求,要求CPU暂停当前的工作,转而去处理这个紧急事件,处理完以后,再回到原来被中断的地方,继续原来的工作,这样的过程称为中断。实现这种功能的部件称为中断系统,请示CPU中断的请求源称为中断源。微型机的中断系统一般允许多个中断源,当几个中断源同时向CPU请求中断,要求为它服务的时候,这就存在CPU优先响应哪一个中断源请求的问题。通常根据中断源的轻重缓急排队,优先处理最紧急事件的中断请求源,即规定每一个中断源有一个优先级别。CPU总是先响应优先级别最高的中断请求。

当CPU正在处理一个中断源请求的时候(执行相应的中断服务程序),发生了另外一个优先级比它还高的中断源请求。如果CPU能够暂停对原来中断源的服务程序,转而去处理优先级更高的中断请求源,处理完以后,再回到原低级中断服务程序,这样的过程称为中断嵌套。这样的中断系统称为多级中断系统,没有中断嵌套功能的中断系统称为单级中断系统。

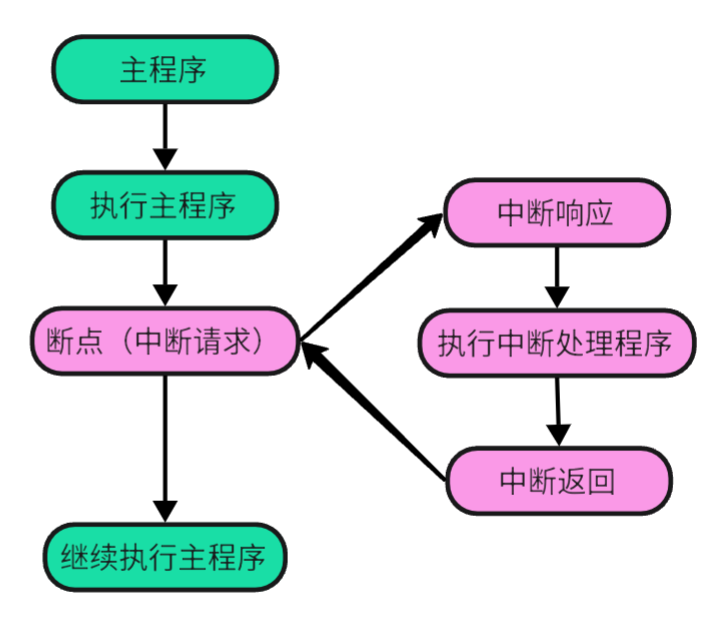

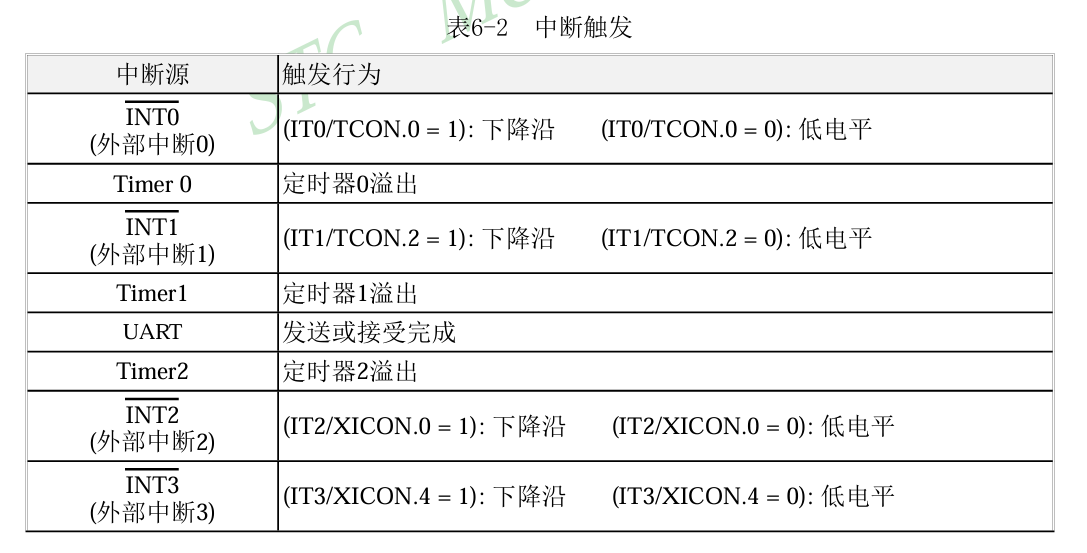

中断触发演示图:

中断处理过程可分为四个阶段:1、中断请求阶段;2、中断响应阶段;3、中断处理阶段;4、中断返回阶段;

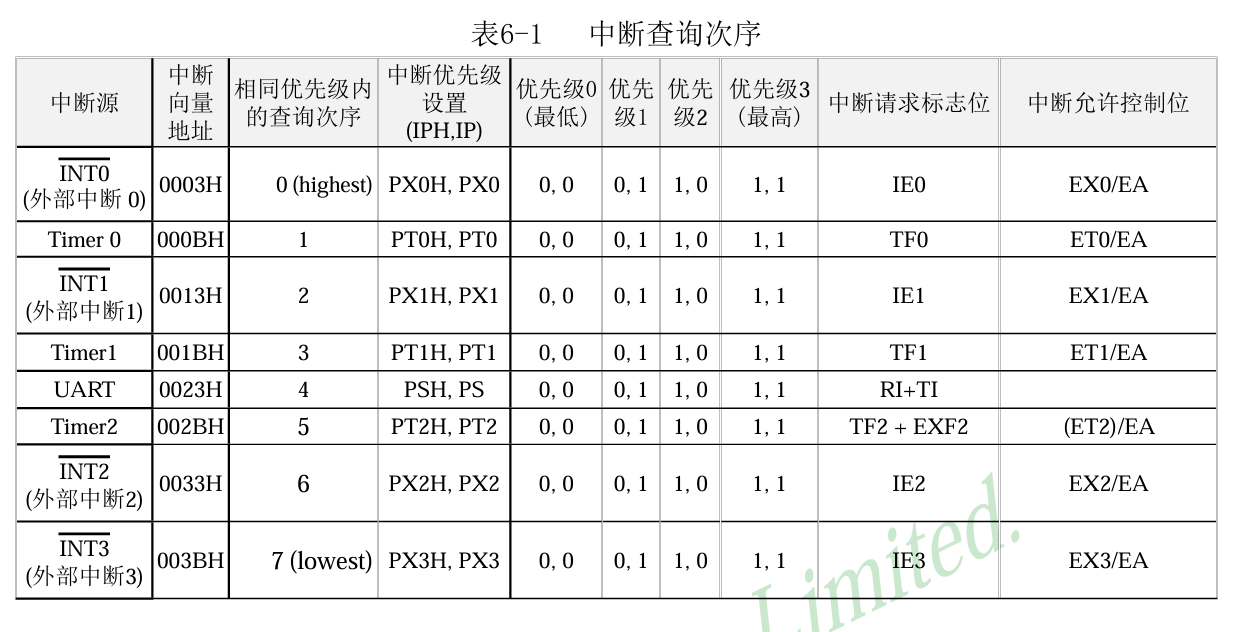

STC89C51RC/RD+系列单片机提供了8个中断请求源,它们分别是:外部中断0(INTO)定时器0中断、外部中断1(INT1)、定时器1中断、串口(UART)中断、定时器2中断、外部中断2(INT2)、外部中断3(INT3)。所有的中断都具有4个中断优先级。用户可以用关总中断允许位(EA/IE.7)或相应中断的允许位来屏蔽所有的中断请求,也可以用打开相应的中断允许位来使CPU响应相应的中断申请:每一个中断源可以用软件独立地控制为开中断或关中断状态;每一个中断的优先级别均可用软件设置。高优先级的中断请求可以打断低优先级的中断,反之,低优先级的中断请求不可以打断高优先级及同优先级的中断。当两个相同优先级的中断同时产生时,将由查询次序来决定系统先响应哪个中断。STC89C51RC/RD+系列单片机的各个中断查询次序如下表6-1所示:

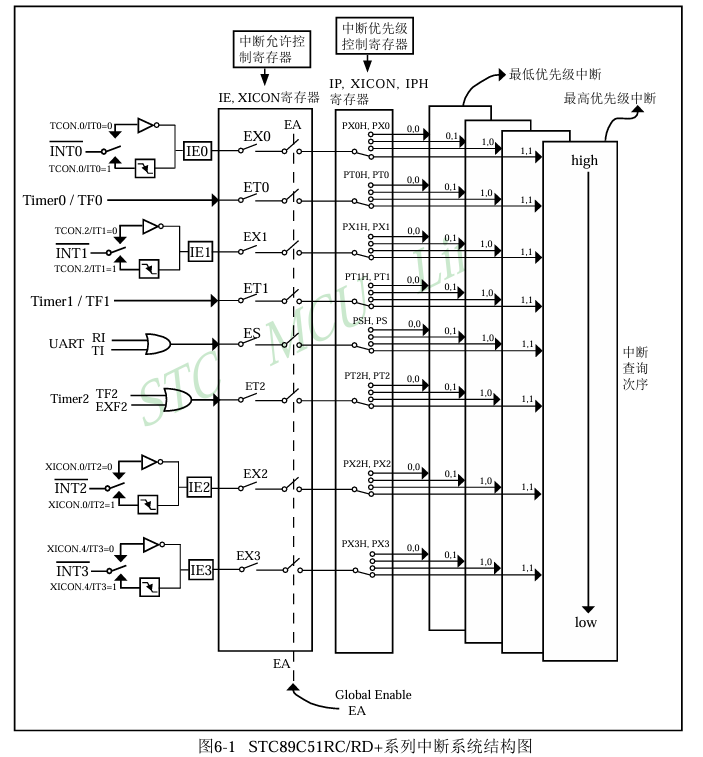

中断系统结构

STC89C51RC/RD+系列单片机的中断系统结构示意图如图6-1所示

中断源介绍:

结构图中共展示8个中断源,按功能分类如下:

1、外部中断(2路)

INT0(P3.2引脚)

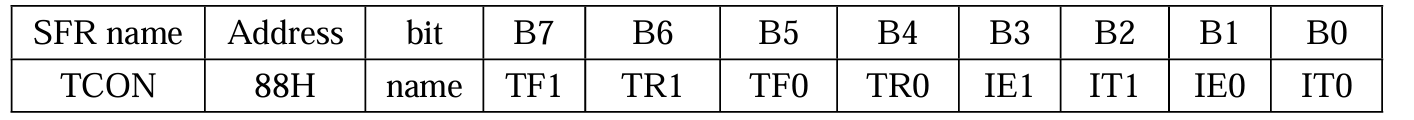

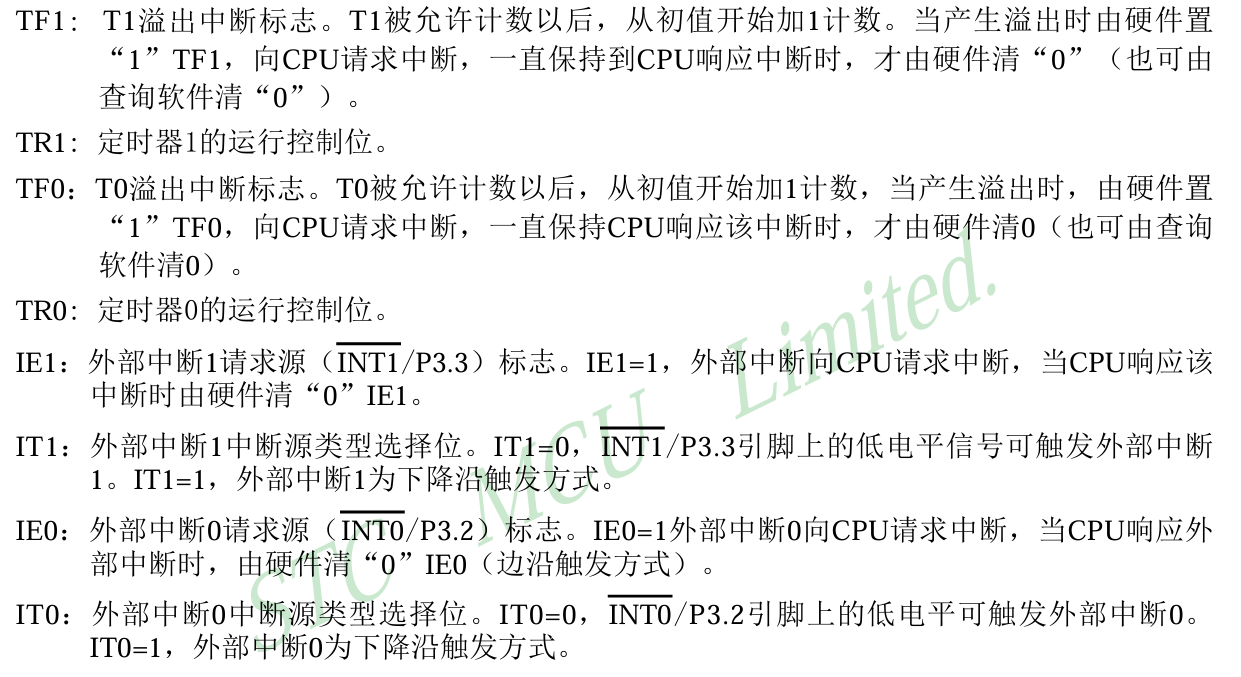

触发方式:由TCON.0(IT0位)控制

IT0=0:低电平触发

IT0=1:下降沿触发

请求标志:IE0(TCON.1),硬件自动置位,响应后硬件清零

INT1(P3.3引脚)

触发方式:由TCON.2(IT1位)控制,

IT1=0:低电平触发

IT1=1:下降沿触发

请求标志:IE1(TCON.3)

2、定时器中断(3路)

Timer0中断

触发条件:定时器0计数溢出(TF0置位)

请求标志:TF0(TCON.5),需软件清零

Timer1中断

触发条件:定时器1计数溢出(TF1置位)

请求标志:TF1(TCON.7),需软件清零

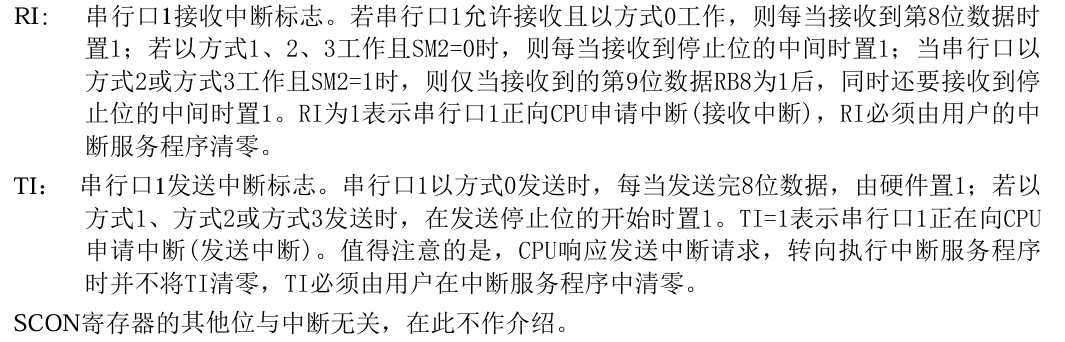

Timer2中断

触发条件:定时器2溢出(TF2)或捕获/重装载(EXF2)

请求标志:TF2(T2CON.7)或 EXF2(T2CON.6)

3、串行通信中断(1路)

UART中断

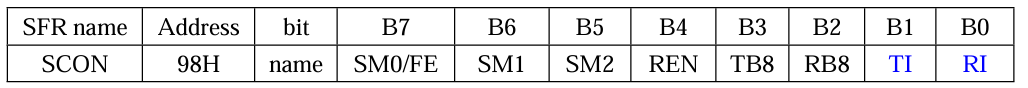

触发条件:接收完成(RI置位)或发送完成(TI置位)

请求标志:RI(SCON.0)/TI(SCON.1),需软件清零

4、扩展外部中断(2路)

INT2(P1.2引脚)

触发方式:由XICON.0(IT2位)控制

IT2=0:低电平触发

IT2=1:下降沿触发

请求标志:IE2(XICON.1)

INT3(P1.3引脚)

触发方式:由XICON.4(IT3位)控制

请求标志:IE3(XICON.5)

中断源触发表:

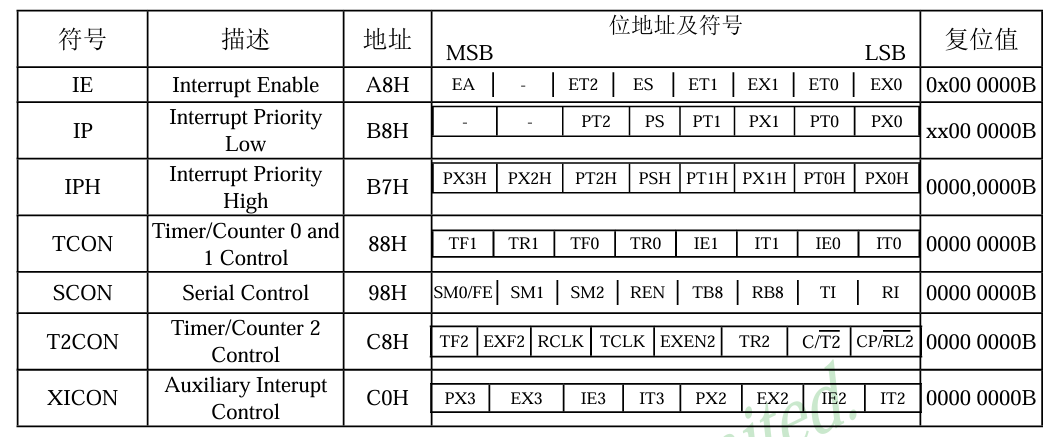

中断寄存器

下表中是与STC89C51RC/RD+系列单片机中断相关的所有寄存器。下面逐一地对寄存器进行介绍;

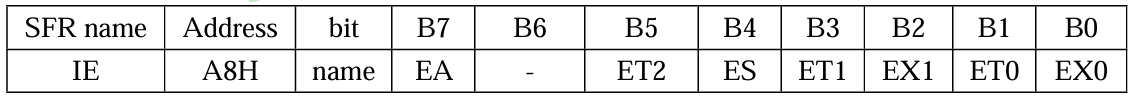

1、IE寄存器(中断允许寄存器(可位寻址))

EA:CPU的总中断允许控制位,EA=1,CPU开放中断,EA=0,CPU屏蔽所有的中断申请。EA的作用是使中断允许形成两级控制。即各中断源首先受EA控制:其次还受各中断源自己的中断允许控制位控制。

ET2:定时/计数器T2的溢出中断允许位。ET2=1,允许T2中断;ET2=0,禁止T2中断。

ES :串行口1中断允许位。ES=1,允许串行口1中断;ES=0,禁止串行口1中断。

ET1:定时/计数器T1的溢出中断允许位。ET1=1,允许T1中断;ET1=0,禁止T1中断。

EX1:外部中断1中断允许位。EX1=1,允许外部中断1中断;EX1=0,禁止外部中断1中断。

ETO:TO的溢出中断允许位。ETO=1,允许T0中断;ET0=0禁止T0中断。

EX0:外部中断0中断允许位。EX0=1,允许中断:EX0=0禁止中断。

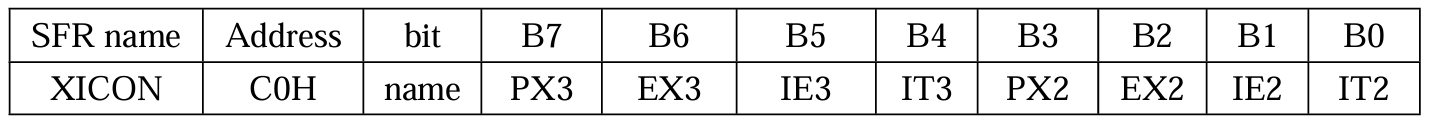

2、XICON寄存器(辅助中断控制寄存器(可位寻址))

PX3:置位表明外部中断3的优先级为高,优先级最终由[PX3H,PX3]=[0,0];[0,1];[1,0];[1,1]来决定。

EX3:如被设置成1,允许外部中断3中断;如被清成0,禁止外部中断3中断。

IE3:外部中断3中断请求标志位,中断条件成立后,IE3=1,可由硬件自动清零。

IT3:当此位由软件置位时,外部中断3为下降沿触发中断;当此位由软件清零时,为低电平触发中断。

PX2:置位表明外部中断2的优先级为高,优先级最终由[PX2H,PX2]=[0,0];[0,1];[1,0];PX2:[1,1]来决定。

EX2:如被设置成1,允许外部中断2中断;如被清成0,禁止外部中断2中断。

IE2 :外部中断2中断请求标志位,中断条件成立后,IE2=1,可由硬件自动清零。

IT2:当此位由软件置位时,外部中断2为下降沿触发中断;当此位由软件清零时,为低电平触发IT2 :中断。

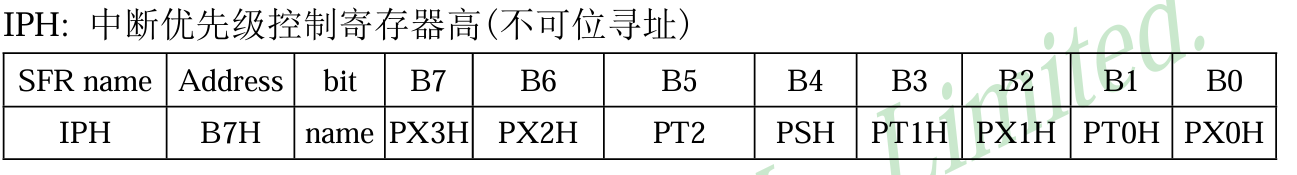

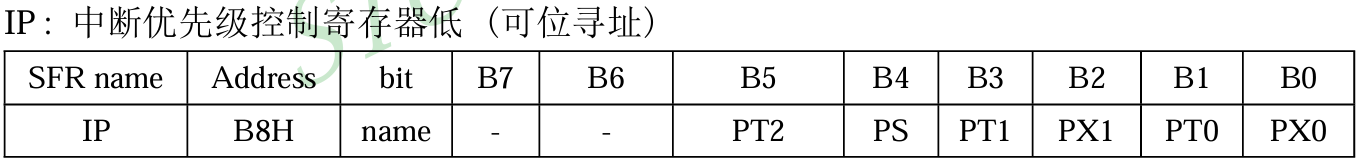

3、IPH中断优先级寄存器高(不可位寻址)和IP中断优先级寄存器低(可位寻址)

PX3H,PX3:外部中断3优先级控制位:

当PX3H=0日PX3=0时,外部中断3为最低优先级中断(优先级0)

当PX3H=0日PX3=1时,外部中断3为较低优先级中断(优先级1)

当PX3H=1日PX3=0时,外部中断3为较高优先级中断(优先级2)

当PX3H=1日PX3=1时,外部中断3为最高优先级中断(优先级3)

PX2H,PX2:外部中断2优先级控制位:

当PX2H=0且PX2=0时,外部中断2为最低优先级中断(优先级0)

当PX2H=0且PX2=1时,外部中断2为较低优先级中断(优先级1)

当PX2H=1日PX2=0时,外部中断2为较高优先级中断(优先级2)

当PX2H=1且PX2=1时,外部中断2为最高优先级中断(优先级3)

PT2H,PT2:定时器2中断优先级控制位:

当PT2H=0且PT2=0时,定时器2中断为最低优先级中断(优先级0)

当PT2H=0且PT2=1时,定时器2中断为较低优先级中断(优先级1)

当PT2H=1月PT2=0时,定时器2中断为较高优先级中断(优先级2)

当PT2H=1月PT2=1时,定时器2中断为最高优先级中断(优先级3)

PSH,PS:串口1中断优先级控制位。

当PSH=0日PS=0时,串口1中断为最低优先级中断(优先级0)

当PSH=0且PS=1时,串口1中断为较低优先级中断(优先级1)

当PSH=1日PS=0时,串口1中断为较高优先级中断(优先级2)

当PSH=1月PS=1时,串口1中断为最高优先级中断(优先级3)

PT1H,PT1:定时器1中断优先级控制位。

当PT1H=0且PT1=0时,定时器1中断为最低优先级中断(优先级0)

当PT1H=0日PT1=1时,定时器1中断为较低优先级中断(优先级1)

当PT1H=1月PT1=0时,定时器1中断为较高优先级中断(优先级2)

当PT1H=1日PT1=1时,定时器1中断为最高优先级中断(优先级3)

PX1H,PX1:外部中断1优先级控制位。

当PX1H=0且PX1=0时,外部中断1为最低优先级中断(优先级0)

当PX1H=0且PX1=1时,外部中断1为较低优先级中断(优先级1)

当PX1H=1月PX1=0时,外部中断1为较高优先级中断(优先级2)

当PX1H=1且PX1=1时,外部中断1为最高优先级中断(优先级3)

PTOH,PT0:定时器0中断优先级控制位:

当PTOH=0且PT0=0时,定时器0中断为最低优先级中断(优先级0)

当PTOH=0日PT0=1时,定时器0中断为较低优先级中断(优先级1)

当PT0H=1月PT0=0时,定时器0中断为较高优先级中断(优先级2)

当PTOH=1且PT0=1时,定时器0中断为最高优先级中断(优先级3)

PXOH,PX0:外部中断0优先级控制位。

当PX0H=0且PX0=0时,外部中断0为最低优先级中断(优先级0)

当PX0H=0日PX0=1时,外部中断0为较低优先级中断(优先级1)

当PX0H=1日PX0=0时,外部中断0为较高优先级中断(优先级2)

当PX0H=1日PX0=1时,外部中断0为最高优先级中断(优先级3)

4、TCON定时器T0/T1中断控制寄存器(可位寻址)

5、SCON串行口控制寄存器(可位寻址)

6、T2CON定时器2/计数器中断控制寄存器(可位寻址)

制作不易!喜欢的小伙伴给个小赞赞!喜欢我的小伙伴点个关注!有不懂的地方和需要的资源随时问我哟!