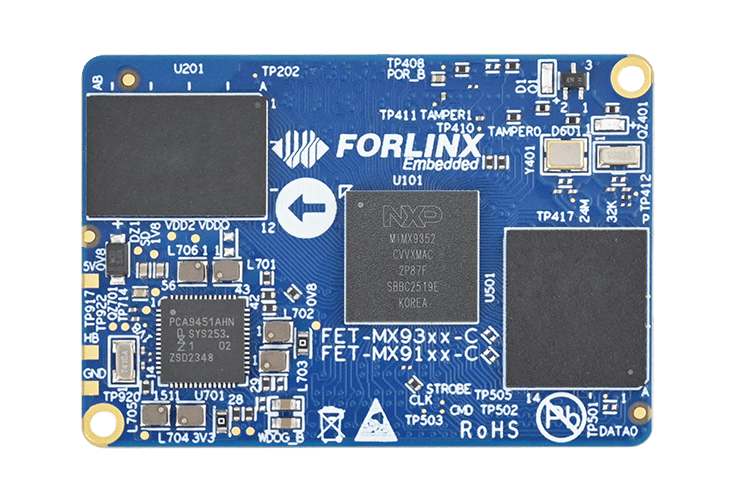

飞凌嵌入式作为NXP金牌合作伙伴,已基于i.MX系列应用处理器推出了多款嵌入式主控产品,除了最新发布的i.MX95xx系列核心板外,同为i.MX9系的i.MX93xx系列核心板也已上市多年并获得了众多客户的认可和选择。

在长期的技术支持服务过程中,飞凌嵌入式总结了用户在i.MX93xx系列产品开发时常见的问题及排查方法,本文小编就为大家梳理这些经验,希望能够帮助各位开发者快速定位问题、提升开发效率。

一、通用排查思路

在i.MX93xx系列主控的开发过程中,若遇到功能异常,大家可遵循以下通用排查步骤:

1. 硬件一致性验证

- 确保底板设计与参考原理图一致,若更换功能芯片需移植对应驱动;

- 检查功能芯片的电源、复位、时钟是否正常。

2. 交叉测试定位

- 通过替换核心板或底板,判断问题归属。

3. 信号与焊接检查

- 确认引脚电平匹配,数据信号输出正常;

- 检查阻容器件是否存在虚焊、连焊等工艺问题。

4. 引脚复用配置

- 验证引脚复用设置是否与功能需求一致。

二、具体模块的常见问题与解决思路

1. 不启动问题

- 除电源和复位外,需确认PWR_EN信号是否正常;

- 检查底板BOOT启动引脚是否按要求配置上下拉电阻。

2. I2C总线问题

- 确认I2C总线是否添加上拉电阻(OD输出特性);

- 检查同组设备地址是否冲突;

- 测量波形:空闲状态应为高电平,数据传输时波形需符合标准;

- 调整上拉电阻阻值:上升沿缓慢可减小阻值,低电平过高可增大阻值;

- 使用工具检测:

i2cdetect -l # 检测I2C总线组

i2cdetect -r -y 2 # 检测第2组总线设备

3. SPI通讯问题

- SPI接口MISO与MOSI需对应连接;

- 确认片选信号(CS)已正确连接;

- 校验通信双方的模式(如CPOL、CPHA)是否一致;

- 测量时钟、数据输出是否正常。

4. USB接口问题

- USB_VBUS_3V3信号必须为3.3V;

- 严禁交叉连接USB差分信号线。

5. SDIO接口问题

- SD2接口的引脚电平与传输速度有关,默认为3.3V,高速模式为1.8V;

- SDIO信号不可以通过电平转换芯片转换引脚电平;

- 检查SDIO总线是否等长处理;

- 优先排查时钟输出是否正常。

6. LVDS显示问题

- 确认屏幕输出模式(VESA/JEIDA)与驱动配置一致。

7. Ethernet网络问题

- 验证PHY芯片与MAC接口模式(如RGMII)是否一致,是否做了等长处理;

- 检查MDIO总线上拉电阻及波形是否正常,避免分叉布线;

- 如果速度不满足需求,可以检测各路电源以及参考地是否完整;

- 确认网络变压器中心抽头接法正确,同一总线PHY地址无冲突;

- MDI数据线是否等长处理,阻抗是否满足要求。

8. CAN总线问题

- CAN总线有多个设备时,需要确认两端的设备是否有120Ω的匹配电阻;

- 如果CAN设备无法通讯,可以尝试将CAN设备的参考地连接,减小工模干扰。

9. UART串口问题

- 串口收发信号需要对应连接;

- 确认串口工具配置是否正确,如:波特率;

- 测量数据输出是否正常。

10. RS485问题

- RS485总线有多个设备时,需要确认两端的设备是否有120Ω的匹配电阻;

- 如果RS485设备无法通讯,可以尝试RS485设备的参考地连接,减小工模干扰;

- 由于RS485为半双工传输,有些RS485芯片需要收发控制信号,需要确认芯片驱动是否已经添加。

11. Audio音频问题

- 通过I2C工具确认音频芯片是否被系统识别;

- 检查I2S数据波形及音频输出通路(如功放电路)。

12. GPIO问题

- 若GPIO复用为BOOT启动引脚,上电时避免添加上下拉电路,或通过缓冲芯片隔离。

三、总结

有了系统化的排查思路与模块化解决方案,就可以高效应对接口通信、信号完整性及配置逻辑等常见开发难题。希望本文总结的实战经验能够为各位开发者朋友提供清晰的问题定位路径,助力项目快速落地。