引言

当项目规模扩大,源文件数量从几个增加到几十个时,基础的Makefile写法会变得冗长且难以维护。例如,为每个.c文件手动编写生成.o文件的规则,不仅重复劳动,还容易在新增文件时遗漏配置。此时,掌握Makefile的通用化语法就变得至关重要------它能通过变量、自动变量、模式规则等特性,让一份Makefile适配大多数项目,实现"一次编写,灵活复用"。

@[toc]

一、通用化语法的核心价值:告别重复劳动

在基础语法中,我们为每个目标文件编写单独的规则,例如:

makefile

app: main.o func.o tool.o

gcc main.o func.o tool.o -o app

main.o: main.c

gcc -c main.c -o main.o

func.o: func.c

gcc -c func.c -o func.o

tool.o: tool.c

gcc -c tool.c -o tool.o当新增一个calc.c文件时,需要手动添加calc.o的规则和链接命令,效率极低。而通用化语法通过"批量处理"思想,将上述规则简化为:

makefile

BIN = app

SRC = $(wildcard *.c) # 自动获取所有.c文件

OBJ = $(SRC:.c=.o) # 自动生成对应的.o文件列表

CC = gcc

$(BIN): $(OBJ)

$(CC) $(OBJ) -o $(BIN)

%.o: %.c

$(CC) -c $< -o $@这种写法下,无论新增或删除.c文件,Makefile都无需修改,极大提升了可维护性。

二、变量:让Makefile更"可编程"

变量是通用化的基础,它能将重复出现的文件名、命令、选项等抽象为符号,便于统一修改。

1. 变量的定义与引用

Makefile中变量的定义格式为变量名=值,引用格式为$(变量名)

makefile

BIN = mytest # 最终目标文件名

SRC = $(wildcard *.c) # 源文件列表(使用内置函数)

OBJ = mytest.o # 目标文件列表

CC = gcc # 编译器

RM = rm -f # 删除命令BIN:存储可执行文件的名称;SRC:存储所有.c源文件的列表;OBJ:存储对应的.o目标文件列表;CC:指定编译器(如gcc或g++);RM:指定删除命令(带-f选项避免文件不存在时报错)。

2. 变量赋值的四种方式(扩展知识点)

-

=(延迟赋值) :变量的值在引用时才解析,可能受到后续赋值影响。makefileA = hello B = $(A) world A = hi # 引用B时,结果为"hi world"(A的最终值) -

:=(立即赋值) :变量的值在定义时立即解析,不受后续赋值影响。makefileA := hello B := $(A) world A := hi # 引用B时,结果为"hello world"(A的初始值) -

?=(默认赋值) :仅当变量未定义时才赋值。makefileA ?= hello # 若A未定义,则A=hello;否则保持原值 -

+=(追加赋值) :在变量原有值的基础上追加内容。makefileCFLAGS = -Wall CFLAGS += -O2 # 最终CFLAGS = -Wall -O2

3. 内置变量与环境变量

除了自定义变量,Makefile还支持:

-

内置变量 :如

$@、$^(自动变量,后文详解); -

环境变量 :可通过

export导出系统环境变量(如PATH)供Makefile使用。makefileexport PATH := /usr/local/gcc/bin:$(PATH) # 优先使用自定义gcc路径

三、自动变量:简化命令中的文件名引用

在基础语法中,命令(如gcc main.o -o main)中的文件名需要手动输入。而自动变量能动态替换为"目标文件""依赖文件"等,让命令更通用。

| 自动变量 | 含义 | 示例场景 |

|---|---|---|

$@ |

当前规则的目标文件 | app: main.o中,$@代表app |

$^ |

当前规则的所有依赖文件(去重) | app: main.o func.o中,$^代表main.o func.o |

$< |

当前规则的第一个依赖文件 | main.o: main.c func.h中,$<代表main.c |

示例:用自动变量简化命令

makefile

# 基础写法(硬编码文件名)

app: main.o func.o

gcc main.o func.o -o app

main.o: main.c

gcc -c main.c -o main.o

# 自动变量写法(通用化)

app: main.o func.o

gcc $^ -o $@ # $^替换为所有依赖,$@替换为目标

main.o: main.c

gcc -c $< -o $@ # $<替换为第一个依赖(main.c)两者功能完全一致,但后者无需因文件名变化而修改命令。

四、模式规则:批量处理同类文件

模式规则是通用化的"核心引擎",它通过通配符%匹配一类文件,实现"一条规则处理多个文件"。

1. 模式规则的语法

makefile

%.o: %.c

$(CC) -c $< -o $@%是通配符,代表任意长度的字符串;- 规则含义:所有

.o文件都依赖于同名的.c文件,且通过gcc -c 源文件 -o 目标文件生成。

例如,当需要生成main.o时,Makefile会自动匹配该规则,等价于:

makefile

main.o: main.c

gcc -c main.c -o main.o同理,func.o会自动匹配为:

makefile

func.o: func.c

gcc -c func.c -o func.o无需手动为每个.c文件编写规则,极大简化了Makefile。

2. 模式规则与自动变量的配合

模式规则通常与自动变量结合使用,例如:

makefile

# 编译所有.c文件为.o文件(通用规则)

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

# 链接所有.o文件为可执行文件

$(BIN): $(OBJ)

$(CC) $(LDFLAGS) $^ -o $@其中:

$(CFLAGS):可自定义编译选项(如-Wall开启警告、-g生成调试信息);$(LDFLAGS):可自定义链接选项(如-lm链接数学库)。

五、实战:通用化Makefile模板

结合变量、自动变量和模式规则,我们可以编写一个适配大多数C项目的通用Makefile模板

1. 完整模板

makefile

# 1. 变量定义

BIN = app # 可执行文件名

SRC = $(wildcard *.c) # 所有.c源文件(使用wildcard函数)

OBJ = $(patsubst %.c,%.o,$(SRC)) # 将.c替换为.o(等价于$(SRC:.c=.o))

CC = gcc # 编译器

CFLAGS = -Wall -g # 编译选项:-Wall显示警告,-g生成调试信息

LDFLAGS = -lm # 链接选项:-lm链接数学库

RM = rm -f # 删除命令

# 2. 最终目标:生成可执行文件

$(BIN): $(OBJ)

$(CC) $(OBJ) $(LDFLAGS) -o $@

@echo "编译完成:$@" # @表示不回显命令本身

# 3. 模式规则:生成.o文件

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

# 4. 伪目标:清理编译产物

.PHONY: clean

clean:

$(RM) $(BIN) $(OBJ)

@echo "清理完成"

# 5. 伪目标:查看变量值(调试用)

.PHONY: debug

debug:

@echo "源文件列表:$(SRC)"

@echo "目标文件列表:$(OBJ)"2. 模板解析

- 变量定义 :

SRC通过wildcard *.c自动获取当前目录所有.c文件,OBJ通过patsubst函数将.c替换为.o,无需手动列举; - 编译选项 :

CFLAGS = -Wall -g开启警告和调试信息,便于代码调试; - 链接选项 :

LDFLAGS = -lm链接数学库(如使用sin、sqrt函数时需要); - 伪目标

clean:删除可执行文件和.o文件,@符号使命令不回显到终端; - 伪目标

debug:用于调试变量值,确认SRC和OBJ是否正确解析。

3. 使用方法

- 将模板保存为

Makefile,放在项目根目录; - 执行

make:自动编译所有.c文件,生成app; - 执行

make clean:删除编译产物; - 执行

make debug:查看变量解析结果(如源文件是否全部被识别)。

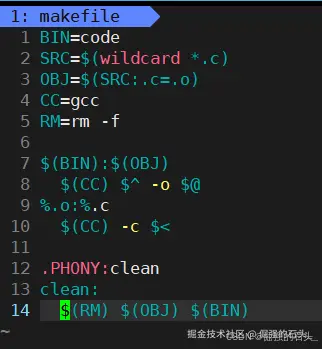

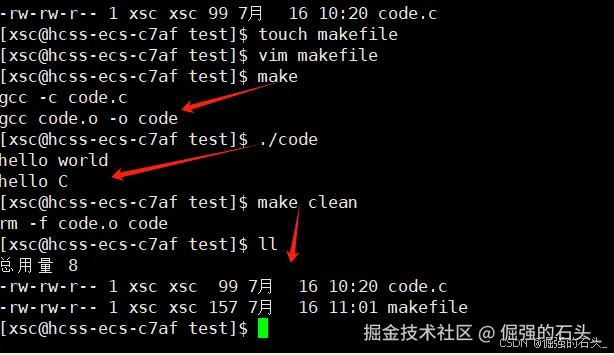

我自己平时写一些简单的代码使用的makefile:

4. 扩展:多目录源文件处理

若源文件分布在src/、inc/等目录,可扩展模板如下:

makefile

SRC_DIR = ./src

INC_DIR = ./inc

SRC = $(wildcard $(SRC_DIR)/*.c)

OBJ = $(patsubst $(SRC_DIR)/%.c,%.o,$(SRC)) # 将src/main.c转为main.o

CFLAGS += -I$(INC_DIR) # -I指定头文件搜索路径

# 模式规则适配目录

%.o: $(SRC_DIR)/%.c

$(CC) $(CFLAGS) -c $< -o $@六、Makefile的执行流程与效率优化

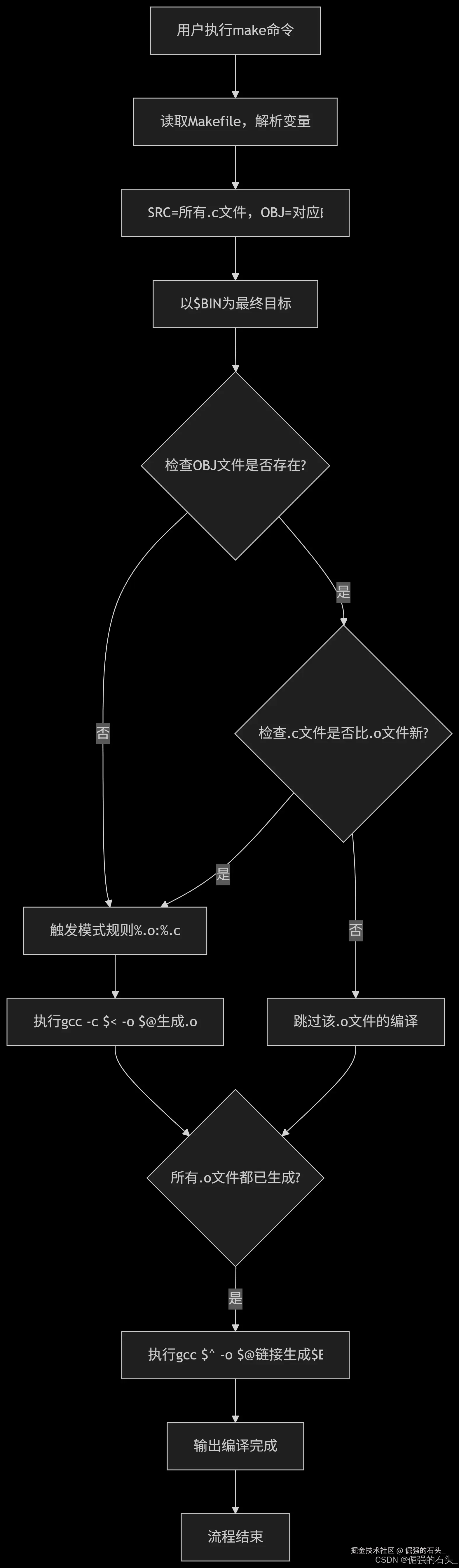

通用化Makefile的执行流程与基础语法一致,但模式规则和变量让依赖解析更高效。其核心逻辑可通过流程图展示: 这里因为CSDN的markdown编辑器实在渲染不出来mermaid的流程图,没办法只能上图片了......

效率优化点

- 增量编译:通过对比文件修改时间,只重新编译修改过的文件(核心优势);

- 并行编译 :使用

make -jN(N为CPU核心数)开启多线程编译,例如make -j4利用4个线程同时编译不同.o文件,速度提升明显; - 减少不必要的依赖 :头文件

func.h若被main.c引用,需在规则中声明main.o: main.c func.h,避免头文件修改后未重新编译。

七、总结

通用化Makefile通过变量、自动变量和模式规则,将重复的构建逻辑抽象为通用模板,实现了"一份文件适配多项目"的目标。其核心价值在于:

- 简化维护:新增文件无需修改Makefile;

- 增强可读性:变量和规则集中管理,逻辑清晰;

- 提升效率:结合增量编译、并行编译,缩短构建时间。

掌握这些语法后,即使面对包含数十个源文件的项目,也能通过几行规则完成自动化构建。Makefile的进阶用法远不止于此(如条件判断、函数嵌套、多目录管理),但通用化语法已能满足大多数中小型项目的需求,是Linux开发中不可或缺的高效工具。