一 基本概要

并发断言用于描述随时间推移的行为特性。与即时断言不同,其评估模型基于时钟周期,使得并发断言仅在时钟跳变时刻被评估。评估中所用变量值为采样值。通过这种方式,无论仿真器内部的事件排序与评估机制如何,都能从评估中获得可预测的结果。这种执行模式也对应于从RTL描述进行硬件解释的综合模型。

断言中使用的变量值在时间槽的预载区(Preponed region)进行采样,而断言本身则在观察区(Observe region)完成评估。

并发断言规范采用的时序模型基于时钟脉冲,并使用广义的时钟周期概念。时钟的定义由用户显式指定,且可随不同表达式而变化。

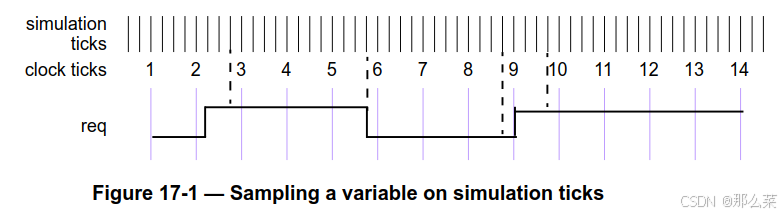

时钟脉冲是时间上的原子时刻,其本身不占据时间跨度。在任何仿真时间点,时钟仅脉冲一次,且该仿真时间的采样值将用于并发断言评估。在断言中,采样值是时钟脉冲时刻变量的唯一有效值。图17-1展示了时钟推进过程中变量的数值变化:信号req在时钟脉冲1和2处为低电平;在脉冲3时刻,其采样值为高并保持至脉冲6;变量req在脉冲6处的采样值为低,并持续至脉冲10。请注意,仿真值虽然在脉冲9处跳变为高,但脉冲9时刻的采样值仍为低。

断言中使用的表达式始终与时钟定义绑定。采样值用于评估值变化表达式或布尔子表达式,这些表达式是判定序列匹配所必需的。

这里请注意:

(1) 必须确保所定义的时钟行为无毛刺,否则可能采样到错误值。

(2)若出现在时钟表达式中的变量同时出现在断言表达式内,该变量在这两处使用的值可能不同:时钟表达式使用变量的当前值,而断言内部使用变量的采样值。

关于(2)点,更加详细说明如下:

时钟表达式中的变量 :使用当前值(Current Value)。

- 当前值 指的是在仿真时间步长(time slot)的主动区(Active Region) 等阶段计算出的最新值。它可能因为仿真事件排序而随时变化,可能存在毛刺(glitch)。

断言表达式中的变量 :使用采样值(Sampled Value)。

- 采样值 指的是在仿真时间步长最开始、所有变化发生之前的预载区(Preponed Region) 捕获的值。它代表了这个时间点开始时的"稳定状态",过滤掉了该时间点内产生的所有毛刺。

控制序列评估的时钟表达式可以比单一信号名更为复杂。诸如(clk && gating_signal)和(clk iff gating_signal)等表达式可用于表示门控时钟,还可能出现其他更复杂的表达式。然而,为确保系统行为的正确性并尽可能符合真正的基于周期的语义,时钟表达式中的信号必须无毛刺,且在任意仿真时间点最多只能发生一次跳变。

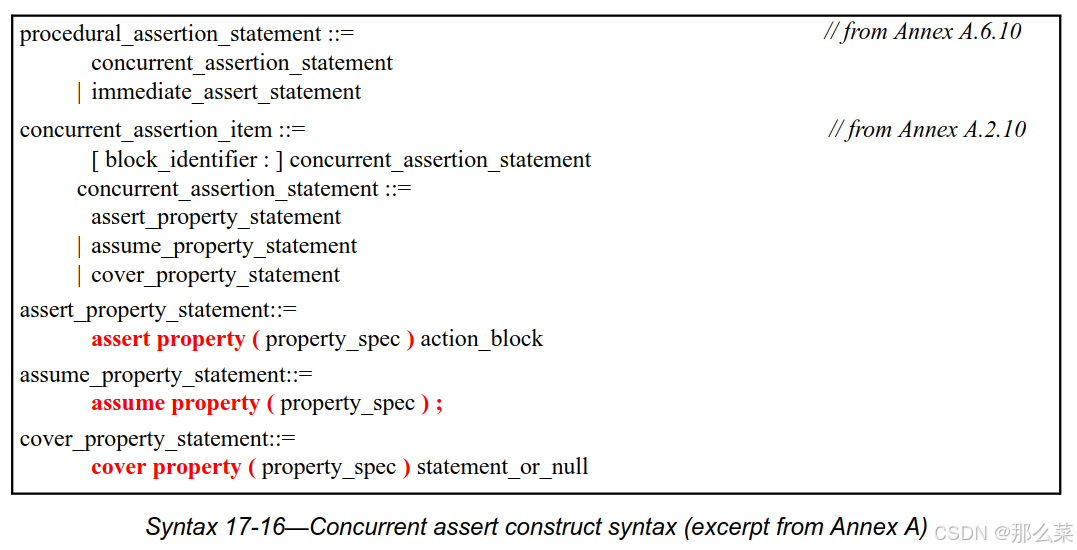

二 并发断言语法