Vivado 时序约束的完整作战地图(二)

文章目录

- [Vivado 时序约束的完整作战地图(二)](#Vivado 时序约束的完整作战地图(二))

- [从"四条路"到"四步曲":Vivado 时序约束的完整作战地图](#从“四条路”到“四步曲”:Vivado 时序约束的完整作战地图)

-

- [一、4 种时序路径------告诉工具"我要看哪里"](#一、4 种时序路径——告诉工具“我要看哪里”)

- [二、4 个步骤完成时序约束](#二、4 个步骤完成时序约束)

从"四条路"到"四步曲":Vivado 时序约束的完整作战地图

一、4 种时序路径------告诉工具"我要看哪里"

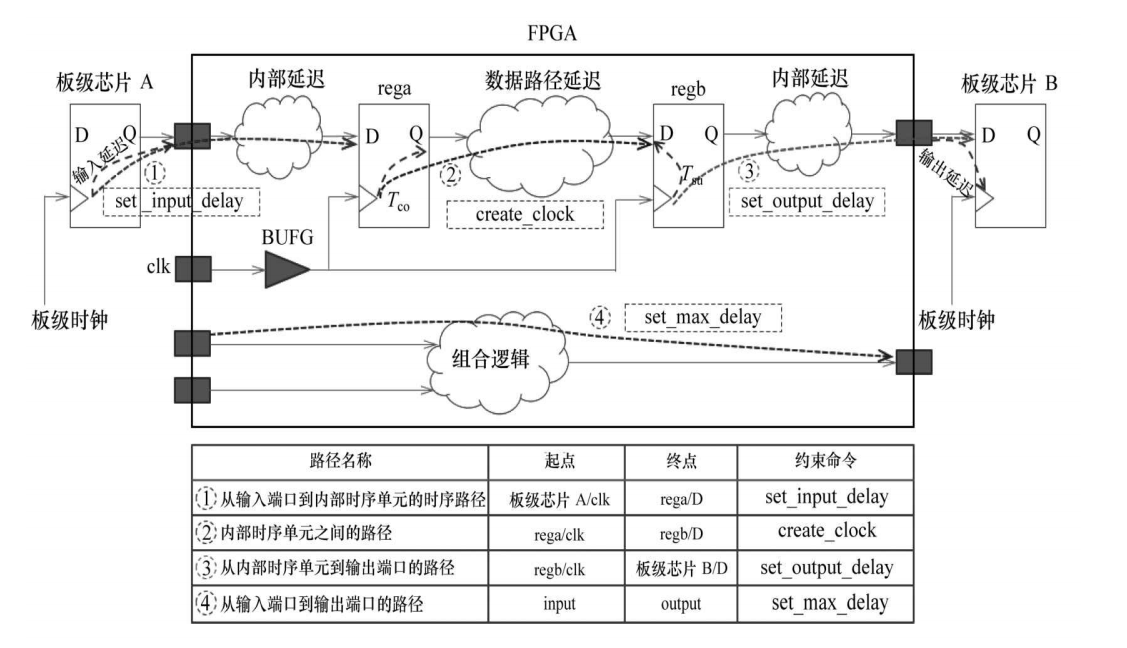

当你学会四种时序约束,再看这张图的大概和细节,如果看懂了没有个线和箭头,时序约束你就学会了!!!

- 帮助理解的关键1 :必须理解三个关键字:时序路径都有起点 、终点 、约束命令

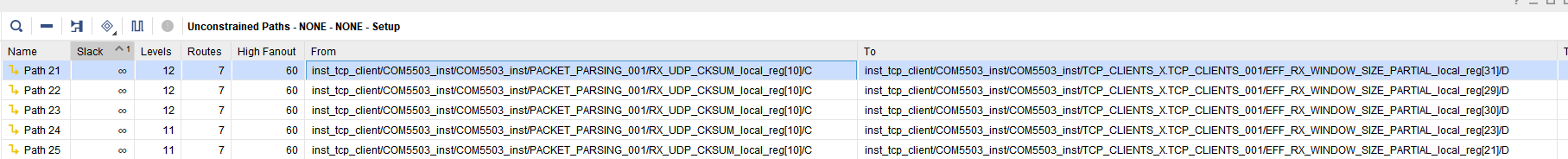

- 帮助理解的关键2 :时序路径的起点大多为时钟端口 而不是输出端口,也就是时序路径是从上一个触发器的C端开头,再到下一个触发器的D端,这是一条路径。在vivado软件分析时序时,也是如此设定的,看vivado时序报告中的路径尾部(起点和终点),是C->D 或者是C->R,具体路径具体分析。主要搞清楚这个起点一般是时钟C

- 后面的时序路径分析都是基于上面两个关键,后面的分析都要带入

| 路径名称 | 真实物理轨迹 | 工具视角起点→终点 | 必须回答的时序问题 | 对应 XDC 命令 |

|---|---|---|---|---|

| ① 输入→内部 | 板级芯片→PCB 走线→FPGA 引脚→第一级寄存器 | clk port(external) → reg/D | "数据比时钟晚到多久?" | set_input_delay |

| ② 内部→内部 | 寄存器→组合逻辑→寄存器 | reg/CLK → reg/D | "一个时钟周期内能不能算完?" | create_clock 周期约束 |

| ③ 内部→输出 | 末级寄存器→引脚→PCB→下游芯片 | reg/CLK → output port | "数据离开 FPGA 多久后有效?" | set_output_delay |

| ④ 输入→输出 | 纯组合:引脚→组合逻辑→引脚 | input port → output port | "横穿 FPGA 的组合延迟上限?" | set_max_delay |

记忆口诀:"进-游-出-穿"

数据从板级"进"来→芯片内部"游"走→"出"口离开→也可能直接"穿"堂过。

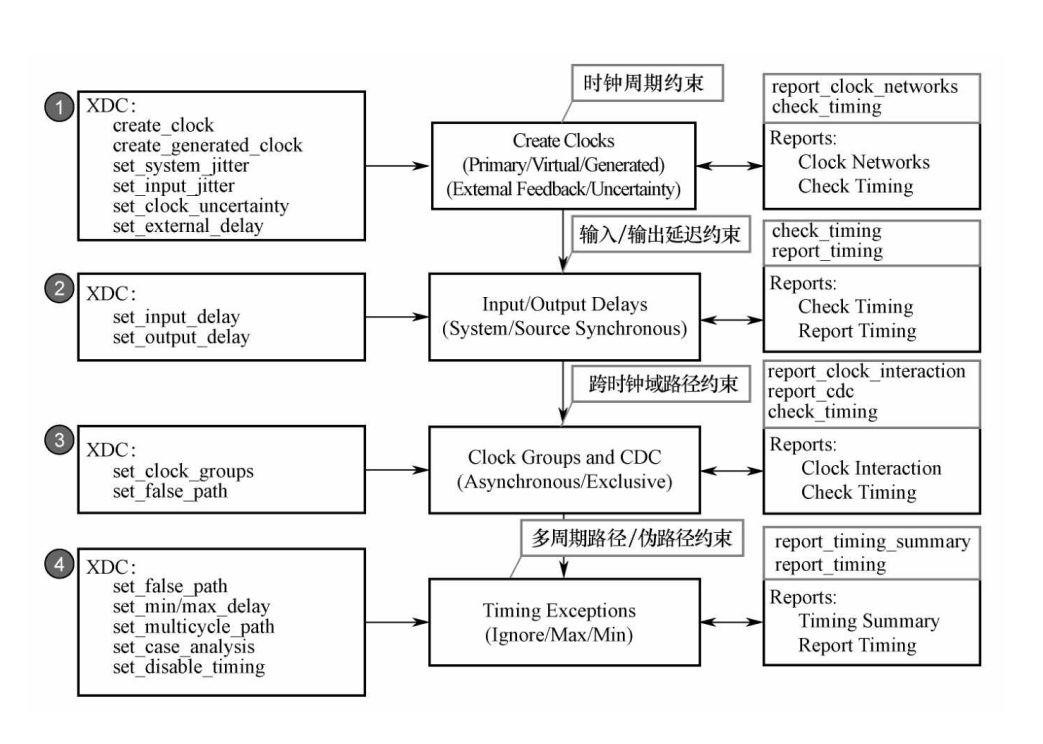

二、4 个步骤完成时序约束

- 第1步针对片内时序路径。时钟周期约束即可覆盖这些路径。这些时钟包括从全局时钟引脚进入的时钟、MMCM/PLL生成的时钟、高速收发器提供的时钟,以 及用户逻辑生成的时钟。

- 第2步针对输入/输出延迟约束,可能会涉及虚拟时钟。

- 第3步针对跨时钟域路径约束。

- 第4步针对多周期路径/伪路径约束。

- Xilinx建议采用Constraints Wizard创建约束

- 通 过report_clock_networks或check_timing等命令验证约束是否已经生效